# A FRAMEWORK FOR EMBEDDED HARDWARE SECURITY ANALYSIS

by

Colin O'Flynn

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

$\operatorname{at}$

Dalhousie University Halifax, Nova Scotia June 2017

© Copyright by Colin O'Flynn, 2017

To my family (old and new).

# Table of Contents

| List of         | Tables                            | $\mathbf{v}$                                                                              |  |  |

|-----------------|-----------------------------------|-------------------------------------------------------------------------------------------|--|--|

| List of Figures |                                   |                                                                                           |  |  |

| Abstra          | ct                                |                                                                                           |  |  |

| List of         | Abbre                             | viations and Symbols Used                                                                 |  |  |

| Acknow          | Acknowledgements                  |                                                                                           |  |  |

| Chapte          | er 1                              | Introduction                                                                              |  |  |

| 1.1             | Backgi                            | ound                                                                                      |  |  |

| 1.2             | Motiva                            | tion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $3$                                              |  |  |

| 1.3             | Contri<br>1.3.1<br>1.3.2<br>1.3.3 | butions of the Thesis4Capture Tools4Fault Attacks5Attack Examples5                        |  |  |

| 1.4             | Outlin                            | e of Thesis                                                                               |  |  |

| Chapte          | er 2                              | Background and Related Work                                                               |  |  |

| 2.1             | Side-C<br>2.1.1<br>2.1.2          | hannel Power Analysis7Attack Types9Implementation Leakage and Success Rate17              |  |  |

| 2.2             | Fault 1<br>2.2.1<br>2.2.2         | Injection20Non-Cryptographic Attacks21Methods of injecting faults22                       |  |  |

| Chapte          | er 3                              | Power Measurements                                                                        |  |  |

| 3.1             | Emissi<br>3.1.1<br>3.1.2          | ons from Decoupling Capacitors23SASEBO-GII CPA Measurement Setup24Measurement Results27   |  |  |

| 3.2             | Acquis<br>3.2.1<br>3.2.2<br>3.2.3 | ition Requirements30External Clock Inputs31External Clock Phase Adjust32Adjustable Gain32 |  |  |

| 3.3    | -                                          | $\frac{33}{35}$                                |

|--------|--------------------------------------------|------------------------------------------------|

| 3.4    | Summary                                    | 36                                             |

| Chapte | er 4 ChipWhisperer Attack Platform         | 38                                             |

| 4.1    | 4.1.1Modular FPGA Design                   | $39 \\ 41 \\ 42 \\ 43 \\ 44 \\ 45 \\ 45 \\ 45$ |

| 4.2    |                                            | 46<br>48                                       |

| 4.3    | 1                                          | $\frac{48}{49}$                                |

| 4.4    | 4.4.1Preprocessing                         | 50<br>51<br>52<br>53                           |

| 4.5    | Example Results                            | 54                                             |

| 4.6    | Summary                                    | 54                                             |

| Chapte | er 5 Clock Recovery                        | 57                                             |

| 5.1    | 1                                          | 58 $59$                                        |

| 5.2    | 5.2.1Synchronous Sampling of Varying Clock | 60<br>62<br>63<br>68                           |

| 5.3    |                                            | 70<br>72                                       |

| 5.4    | 5.4.1 Hardware Design                      | 72<br>76<br>76                                 |

|        | 5.4.3                                              | Results of CPA Attack                                                                                                                                 | 78                                    |

|--------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

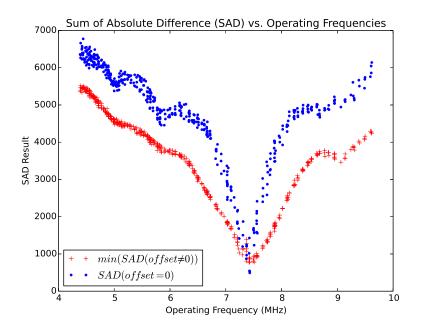

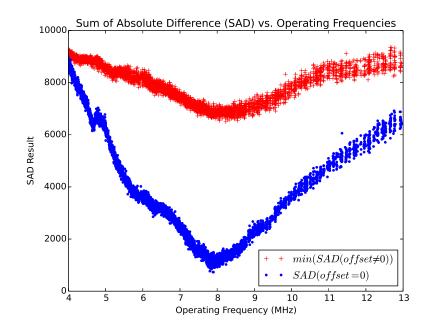

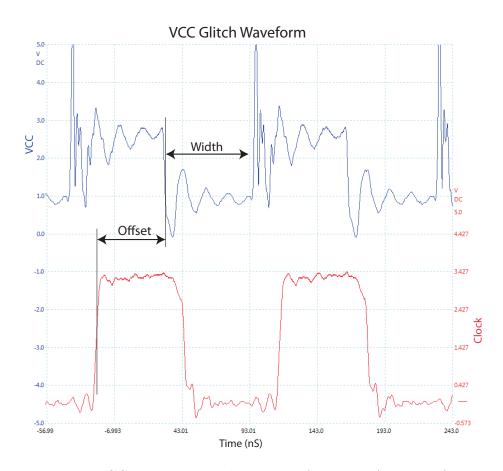

| 5.5    | Fault I<br>5.5.1<br>5.5.2<br>5.5.3                 | InjectionInjectionInjectionSum of Absolute Difference TriggerInjectionFault Injection and Target CodeInjectionDependency on Target FrequencyInjection | 80<br>83<br>85<br>89                  |

| 5.6    | Summa                                              | ary                                                                                                                                                   | 89                                    |

| Chapte | er 6                                               | AES-256 Bootloader Attack                                                                                                                             | 92                                    |

| 6.1    | Introdu                                            | uction                                                                                                                                                | 92                                    |

| 6.2    | Descrip                                            | ption of Bootloader                                                                                                                                   | 92                                    |

| 6.3    | AES-23<br>6.3.1<br>6.3.2<br>6.3.3                  | 56 Decryption       Background       Side Channel Power Analysis       Cipher Block Chaining Mode                                                     | 94<br>94<br>95<br>96                  |

| 6.4    | Hardw.<br>6.4.1<br>6.4.2                           | are                                                                                                                                                   | 96<br>97<br>98                        |

| 6.5    | Determ                                             | nining Key                                                                                                                                            | 98                                    |

| 6.6    | Determ                                             | nining IV                                                                                                                                             | 99                                    |

| 6.7    | Determ                                             | nining Signature                                                                                                                                      | 102                                   |

| 6.8    | Summa                                              | ary                                                                                                                                                   | 102                                   |

| Chapte | er 7                                               | IEEE 802.15.4 Wireless Node Attacks                                                                                                                   | 04                                    |

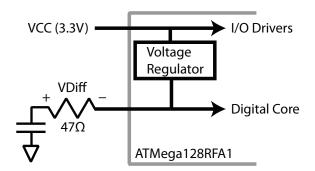

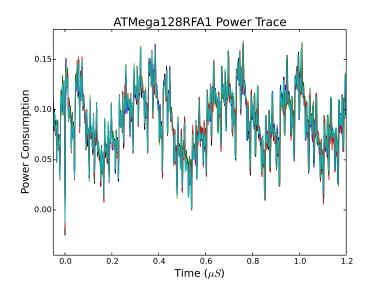

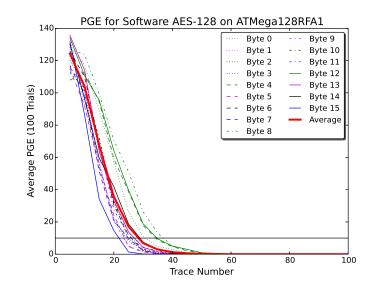

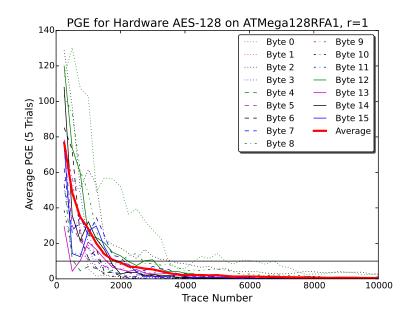

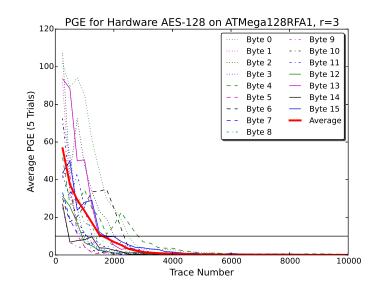

| 7.1    | ATMeg<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5 | Side-Channel Power Analysis1Power Measurement1Related Hardware Attack1Application to ATMega128RFA11                                                   | 106<br>106<br>108<br>109<br>111<br>15 |

| 7.2    | IEEE 8<br>7.2.1<br>7.2.2                           | Detailed Message Format                                                                                                                               | 17<br>19<br>21                        |

| 7.3    | Applica<br>7.3.1                                   |                                                                                                                                                       | 121<br>122                            |

| 7.4     | Attack                                              | ing Wireless Nodes 130                                                                                                                              |

|---------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.5     | Summa                                               | ary                                                                                                                                                 |

| Chapte  | er 8                                                | Crowbar Glitch Generation                                                                                                                           |

| 8.1     | Related                                             | d Work                                                                                                                                              |

| 8.2     | Glitchi                                             | ng Mechanism                                                                                                                                        |

| 8.3     | Target<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5 | Devices136AVR Microcontroller.137Raspberry Pi (ARM11).137Beaglebone Black (ARM Cortex-A8)138Android Smart Phone (ARM11).138FPGA Board (SAKURA-G)138 |

| 8.4     | Fault I<br>8.4.1<br>8.4.2<br>8.4.3                  | nsertion Results139Low-Precision Faults on Microprocessors140Low-Precision Faults on FPGAs143High-Precision Faults146                               |

| 8.5     | Discuss<br>8.5.1<br>8.5.2<br>8.5.3                  | sion                                                                                                                                                |

| 8.6     | Summa                                               | ary                                                                                                                                                 |

| Chapte  | er 9                                                | Conclusions and Future Work                                                                                                                         |

| 9.1     | Conclu                                              | ding Remarks                                                                                                                                        |

| 9.2     | Future                                              | Work                                                                                                                                                |

| 9.3     | Beyond                                              | l Power Analysis and Glitching                                                                                                                      |

| Bibliog | graphy                                              |                                                                                                                                                     |

| Appen   | dix A                                               | Publications and Contributions                                                                                                                      |

| A.1     | Peer R                                              | eviewed Publications                                                                                                                                |

| A.2     | Acader                                              | nic Conference Activities                                                                                                                           |

| A.3     | Industr                                             | ry Conference Presentations                                                                                                                         |

| A.4     | Industi                                             | ry Publications                                                                                                                                     |

| Appen | dix B Copyright Permission Letters                                                                                  | 177 |

|-------|---------------------------------------------------------------------------------------------------------------------|-----|

| B.1   | Side channel power analysis of an AES-256 Bootloader $[100]$ $\ .$                                                  | 177 |

| B.2   | Power Analysis Attacks against IEEE 802.15.4 Nodes [104] $\ .$                                                      | 177 |

| B.3   | Synchronous sampling and clock recovery of internal oscillators for side channel analysis and fault injection [103] | 182 |

| B.4   | ChipWhisperer: An Open-Source Platform for Hardware Embedded<br>Security Research [105]                             | 187 |

| B.5   | A case study of Side-Channel Analysis using Decoupling Capacitor<br>Power Measurement with the OpenADC [101]        | 192 |

# List of Tables

| 3.1 | Number of traces required to attack a FPGA implementation for various measurement techniques | 27    |

|-----|----------------------------------------------------------------------------------------------|-------|

| 3.2 | Examples of sampling rates used in various published attacks                                 | 31    |

| 4.1 | Capture speed of various platforms including the ChipWhisperer and commercial oscilloscopes  | 50    |

| 5.1 | Variation of clock frequency for the ATMega48A clocking options.                             | 63    |

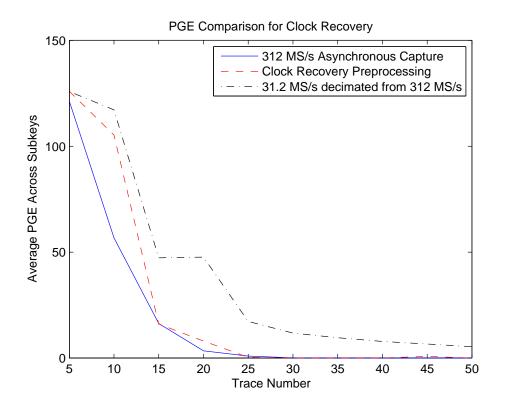

| 5.2 | Results of attack using various preprocessing methods to remove effect of varying frequency. | 68    |

| 6.1 | Results of CPA attack against I.V. with AES-256                                              | 101   |

| 7.1 | Power analysis attacks against commercially available crypto-<br>graphic implementations     | 107   |

| 7.2 | Range of points used in performing CPA attack on ATMega128RFA1                               | 1.116 |

| 8.1 | Specifics of crowbar activation time required for various platforms.                         | 141   |

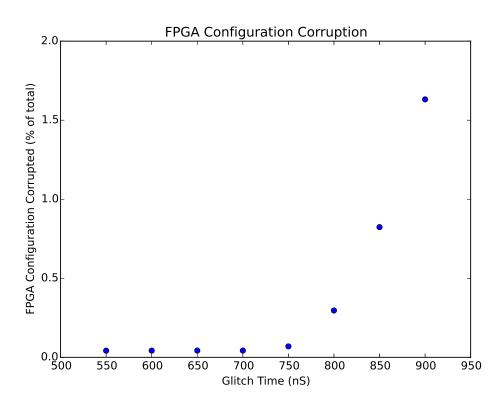

| 8.2 | Results of fault injection against Spartan 6 LX75 FPGA, repeated $10 \times$ for each width  | 146   |

# List of Figures

| 2.1 | SPA attack against RSA                                                                                           | 9  |

|-----|------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | DPA attack on a single bit.                                                                                      | 11 |

| 2.3 | Power consumption of an AVR compared to bits set to '1'                                                          | 13 |

| 3.1 | Simplified H-Field probe                                                                                         | 26 |

| 3.2 | Location of decoupling capacitors on underside of FPGA                                                           | 26 |

| 3.3 | Wire wrapped around decoupling capacitor for EM measurement.                                                     | 27 |

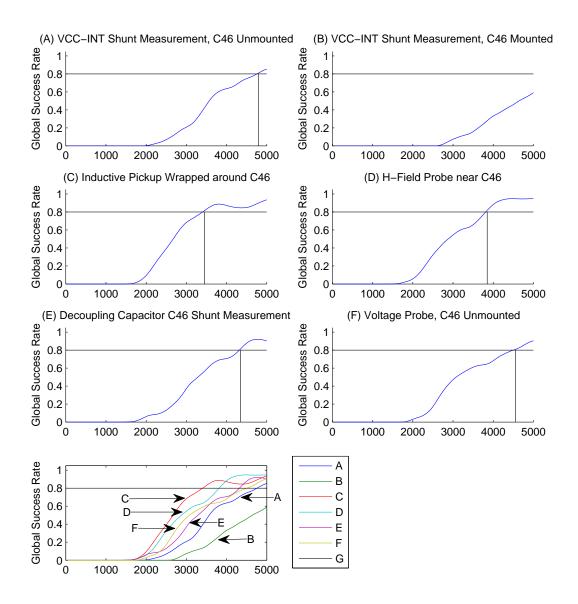

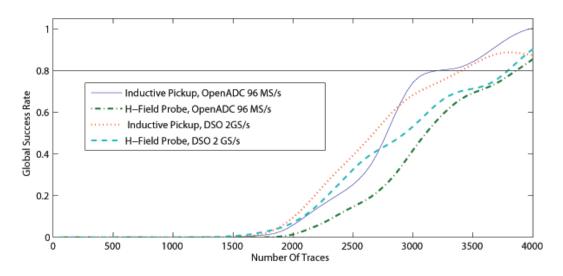

| 3.4 | Success rate of an attack against an FPGA for various measurement techniques.                                    | 28 |

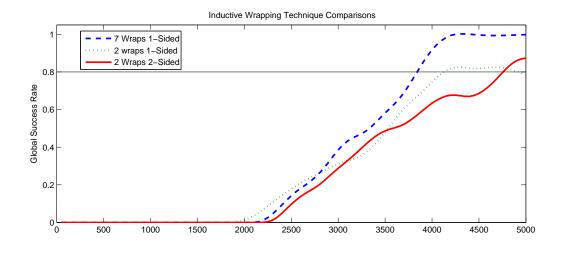

| 3.5 | Comparison of different techniques for wrapping a decoupling capacitor with measurement wire.                    | 30 |

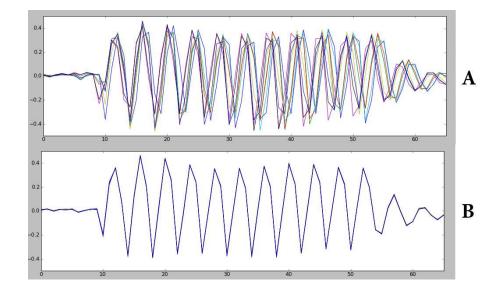

| 3.6 | Comparison of asynchronous and synchronous sampling                                                              | 32 |

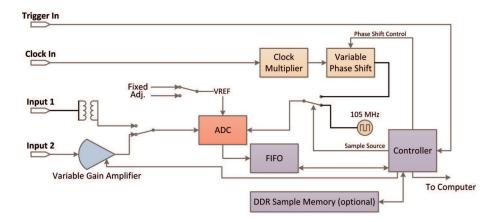

| 3.7 | Architecture of the ADC and FPGA measurement platform                                                            | 33 |

| 3.8 | The OpenADC (ADC sampling platform) mount on a FPGA development board                                            | 35 |

| 3.9 | Comparison of success rate for the OpenADC and a commerical oscilloscope                                         | 36 |

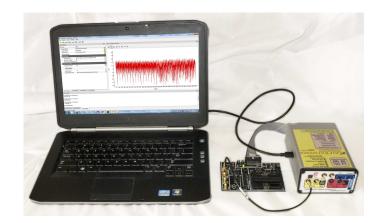

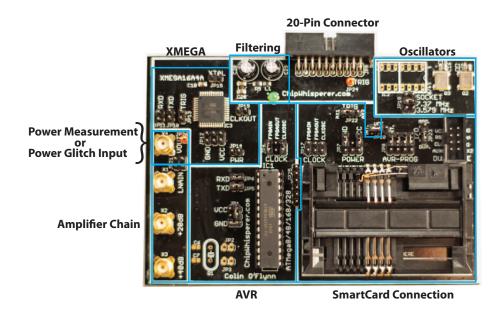

| 4.1 | Example of the ChipWhisperer baseboard using a FPGA module.                                                      | 40 |

| 4.2 | Complete ChipWhisperer attack system, including computer<br>and target board                                     | 40 |

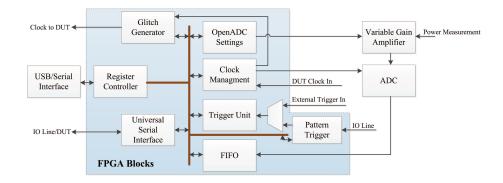

| 4.3 | Details of the ChipWhisperer FPGA blocks                                                                         | 41 |

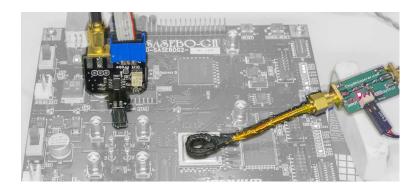

| 4.4 | Examples of differential probe and H–Field probe usage. $\ . \ .$                                                | 42 |

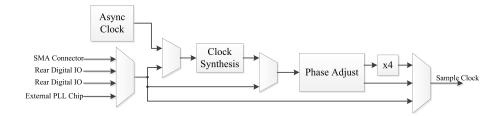

| 4.5 | Clock Routing in ChipWhisperer capture hardware                                                                  | 42 |

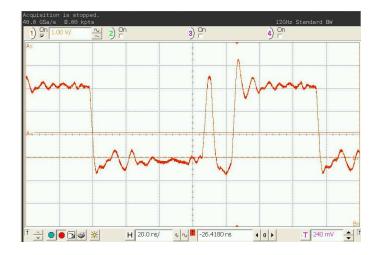

| 4.6 | Inserting a glitch into a 7.37 MHz clock coming from a target device.                                            | 44 |

| 4.7 | The ChipWhisperer built on to the SAKURA-G hardware                                                              | 46 |

| 4.8 | The Multi-Target board provides a simple platform for testing various attacks and cryptographic implementations. | 47 |

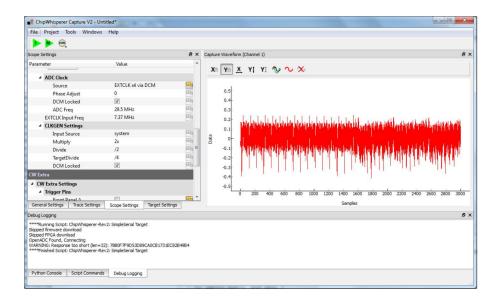

| 4.9  | The Capture GUI provides an interface to the capture hard-<br>ware, target device, and storage media                      | 49 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

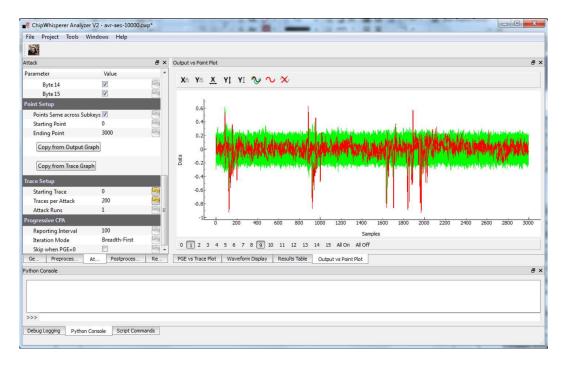

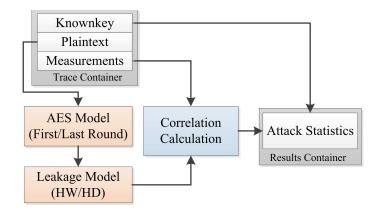

| 4.10 | The Analyzer GUI runs a given attack on the stored traces.                                                                | 51 |

| 4.11 | The ChipWhisperer attack module allows specification of dif-<br>ferent leakage and cryptographic models.                  | 53 |

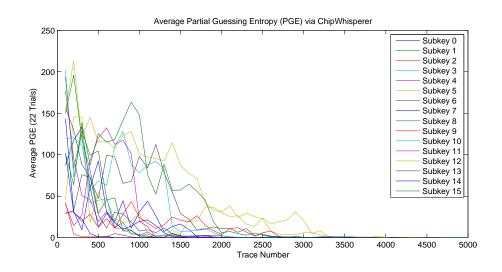

| 4.12 | Attack results on the SASEBO-GII from the ChipWhisperer                                                                   | 55 |

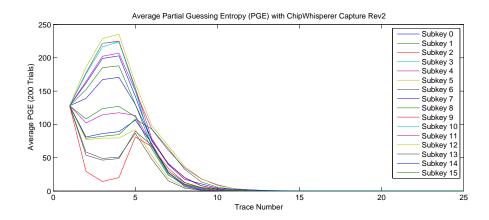

| 4.13 | Attack results against AES-128 software running on a micro-<br>controller from the ChipWhisperer.                         | 55 |

| 4.14 | Attack results against AES-128 software running on a micro-<br>controller from the PicoScope                              | 56 |

| 5.1  | Comparison of sampling platforms including both asynchronous and synchronous capture                                      | 59 |

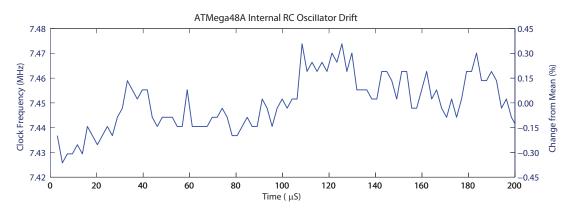

| 5.2  | Atmel AtMega48A internal clock drift during a side-channel attack.                                                        | 61 |

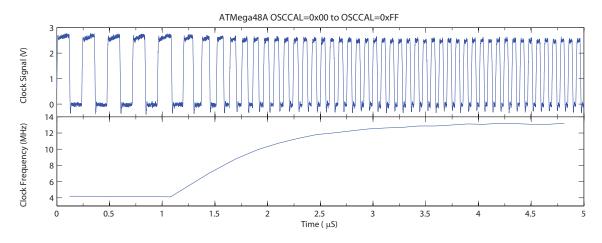

| 5.3  | Atmel AtMega48A internal clock frequency change as OSCCAL changes from 0 to 255                                           | 62 |

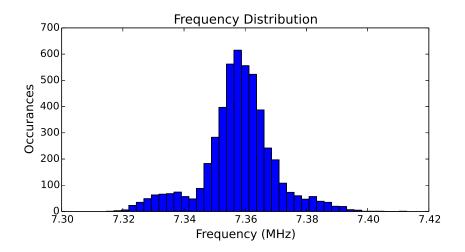

| 5.4  | The histogram of the operating frequency for the 'drift' range.                                                           | 64 |

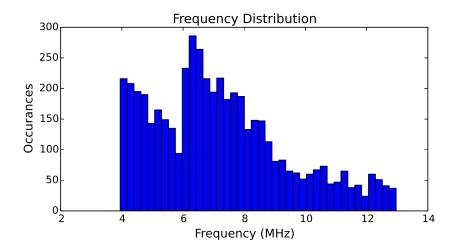

| 5.5  | The histogram of the operating frequency for the 'extended' range.                                                        | 64 |

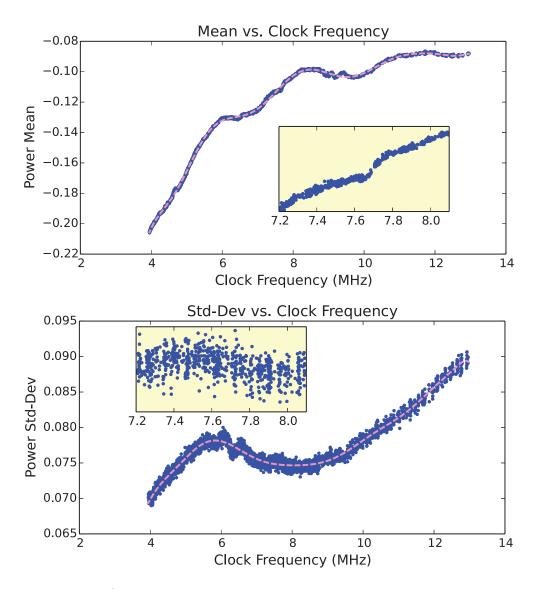

| 5.6  | Plot of the trace mean and standard deviation compared to operating frequency of the microcontroller                      | 66 |

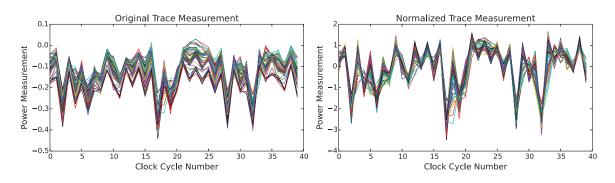

| 5.7  | Example of trace normalization to remove the effect of varying operating frequency.                                       | 68 |

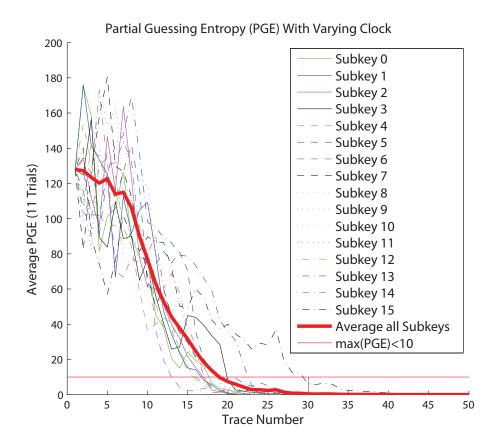

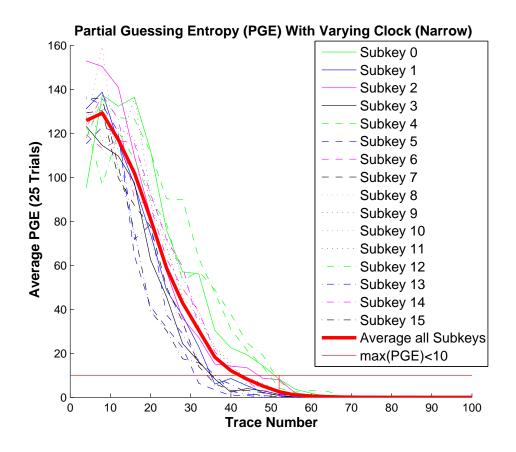

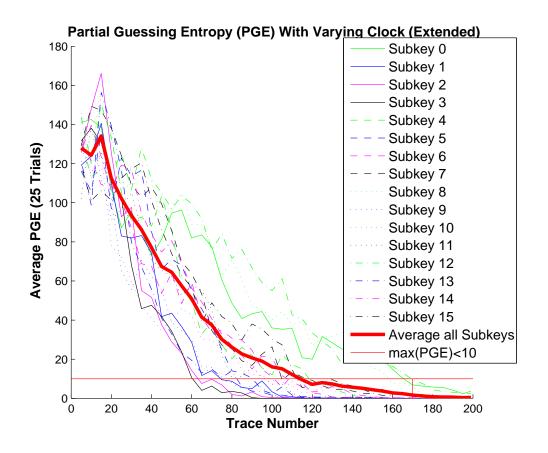

| 5.8  | Results of a CPA attack on a device with oscillator frequency randomly varying between 3.9 MHz–13 MHz on each encryption. | 69 |

| 5.9  | Trace compression can be considered a form of clock recovery<br>by detecting zero-crossings                               | 70 |

| 5.10 | Clock recovery can reduce the trace sizes, without impacting attack results.                                              | 71 |

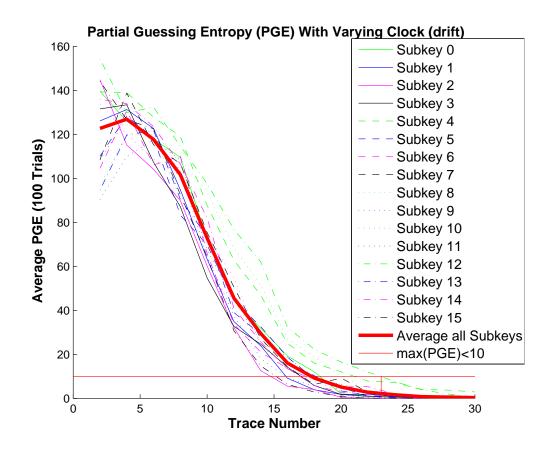

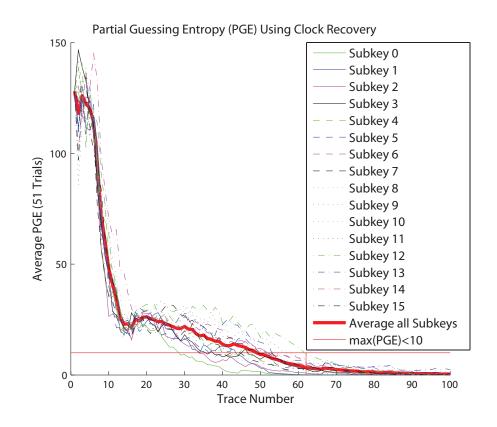

| 5.11 | Results of a CPA attack on a device with a drifting internal RC oscillator using clock recovery preprocessing.            | 73 |

| 5.12 | Results of a CPA attack on a device with a slightly varied in-<br>ternal RC oscillator using clock recovery preprocessing | 74  |

|------|---------------------------------------------------------------------------------------------------------------------------|-----|

| 5.13 | Results of a CPA attack on a device with a widely varied inter-<br>nal RC oscillator using clock recovery preprocessing   | 75  |

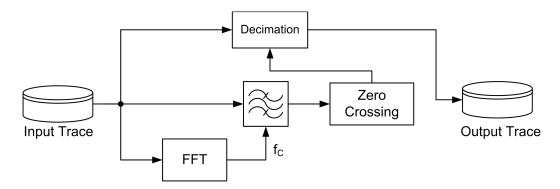

| 5.14 | Clock recovery block diagram                                                                                              | 76  |

| 5.15 | Example of recovery of internal oscillator frequency on AVR                                                               | 77  |

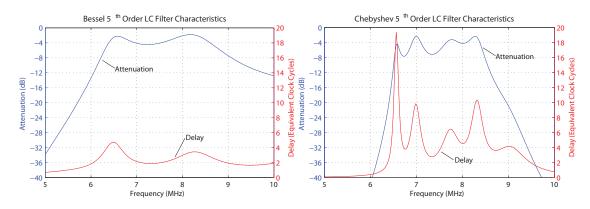

| 5.16 | Comparison of Chebyshev and Bessel filter delay resulting in phase differences.                                           | 78  |

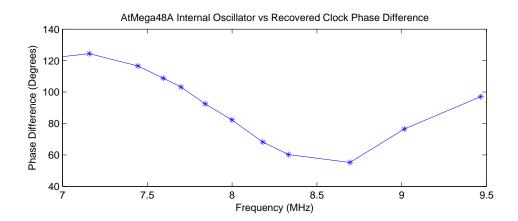

| 5.17 | Measurement of actual phase difference over frequency in the system                                                       | 79  |

| 5.18 | Photo of test setup for performing clock recovery                                                                         | 79  |

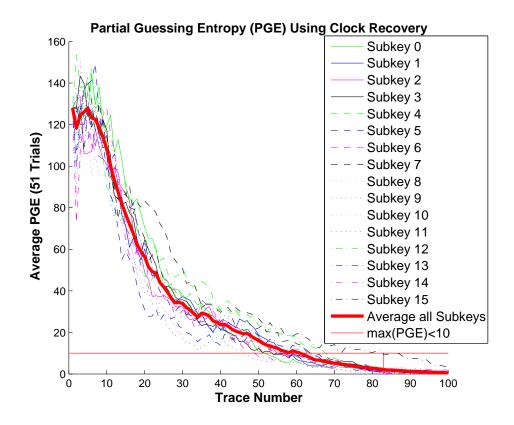

| 5.19 | Results of a CPA attack on a device with a drifting internal RC oscillator using clock recovery hardware.                 | 81  |

| 5.20 | Results of a CPA attack on a device with a slightly varied in-<br>ternal RC oscillator using clock recovery hardware      | 82  |

| 5.21 | Results of a CPA attack on a device with a drifting internal RC oscillator with no preprocessing or clock recovery.       | 83  |

| 5.22 | SAD trigger without performing clock recovery.                                                                            | 85  |

| 5.23 | SAD trigger with performing clock recovery.                                                                               | 86  |

| 5.24 | Waveform of VCC glitch generated from a derived clock. $\ . \ .$                                                          | 87  |

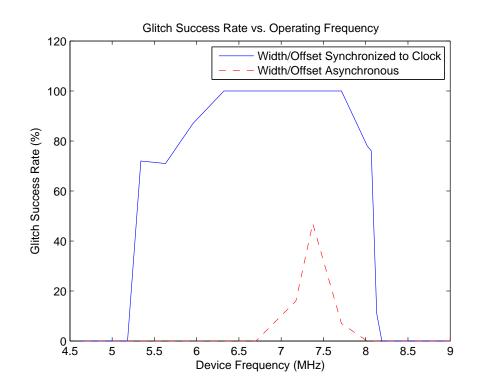

| 5.25 | Demonstration of voltage glitching success as frequency varies.                                                           | 90  |

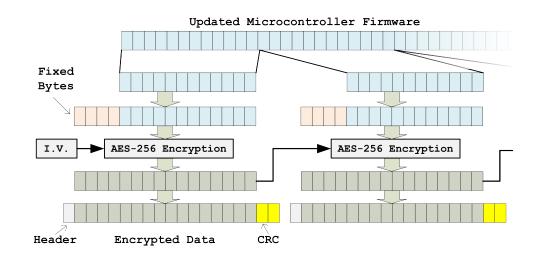

| 6.1  | Data format for AES-256 bootloader showing both encryption format and communications protocol.                            | 93  |

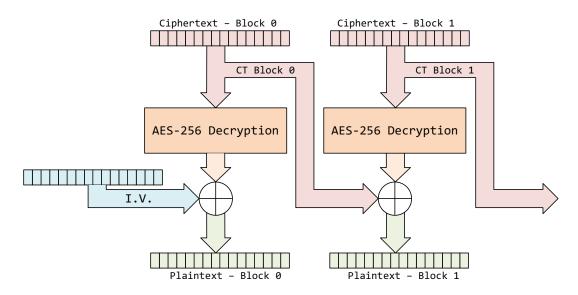

| 6.2  | AES-256 Cipher Block Chaining (CBC) Mode Decryption $~$ .                                                                 | 97  |

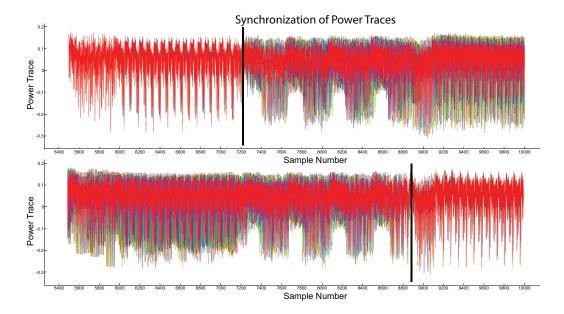

| 6.3  | Power traces in AES-256 require resyncronization                                                                          | 98  |

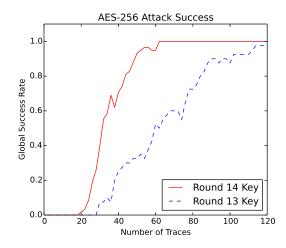

| 6.4  | Two CPA attacks are performed to determine both the 14th and 13th round keys                                              | 99  |

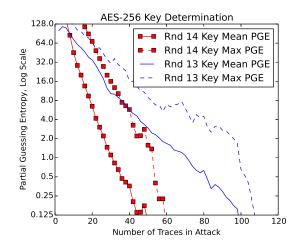

| 6.5  | The partial guessing entropy for the AES-256 attack 1                                                                     | .00 |

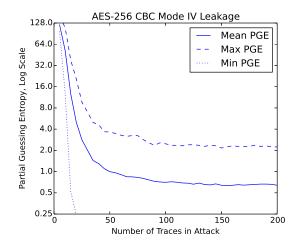

| 6.6  | A CPA attack on the I.V. of the AES-256 is not entirely successful.                                                       | .01 |

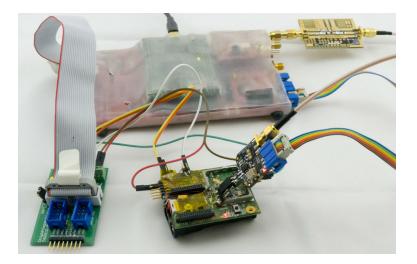

| 7.1  | ChipWhisperer setup with ATMegaRF development board $1$                                                                   | .06 |

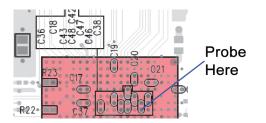

| 7.2  | Measurement shunt location for devices with internal voltage regulators.                                                                                    | 108   |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7.3  | Photo of 47-ohm resistor inserted into decoupling capacitor path.                                                                                           | 109   |

| 7.4  | Power traces for AES-128 hardware peripheral in ATMega128RFA                                                                                                | 1.110 |

| 7.5  | CPA attack results on AES-128 software implementation on ATMega128RFA1.                                                                                     | 112   |

| 7.6  | CPA attack results on AES-128 hardware peripheral in AT-Mega128RFA1.                                                                                        | 114   |

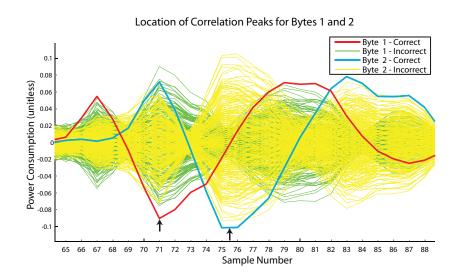

| 7.7  | Correlation peaks for CPA attack on ATMega128RFA1                                                                                                           | 114   |

| 7.8  | Attacking later-rounds in AES peripheral is also successful                                                                                                 | 116   |

| 7.9  | The following data is used as the input to AES-128 when a frame is decrypted by an IEEE 802.15.4 stack. The FrameCounter can be controlled by the attacker. | 118   |

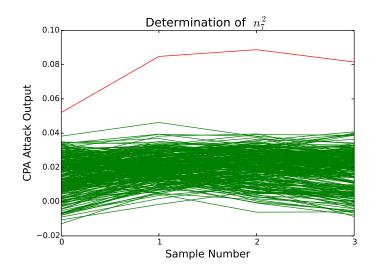

| 7.10 | The CPA attack can reach from one round to the next to de-<br>termine certain bytes in the AES algorithm                                                    | 129   |

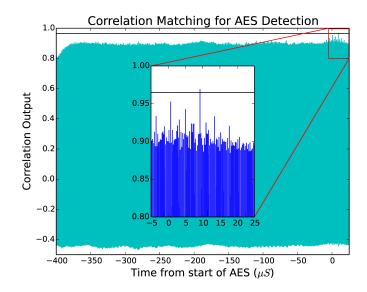

| 7.11 | Correlation matching to determine location of AES peripheral operation.                                                                                     | 132   |

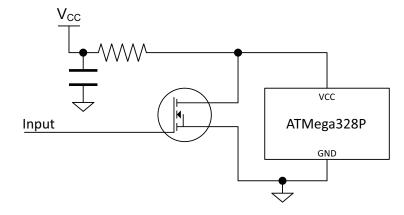

| 8.1  | Crowbar circuit attached across an ATMega328P                                                                                                               | 137   |

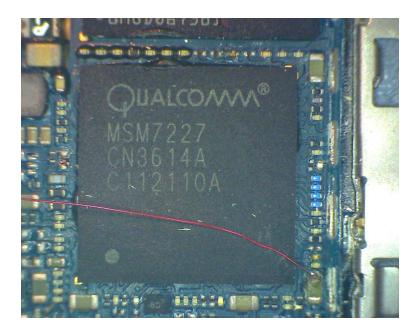

| 8.2  | Attaching a crowbar to an Android smartphone SoC                                                                                                            | 139   |

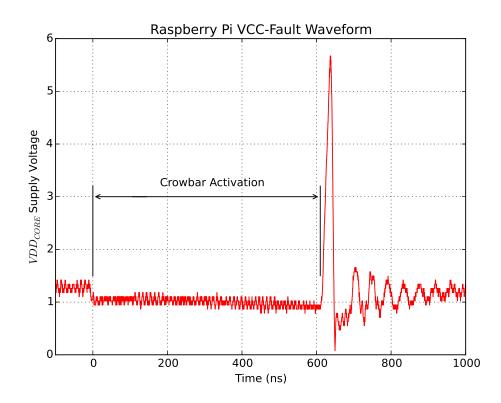

| 8.3  | The signal on the $VCC_{CORE}$ rail for the Raspberry Pi during fault injection                                                                             | 142   |

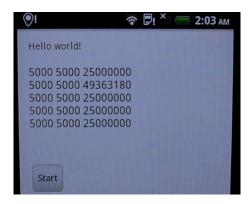

| 8.4  | Simple C program used in validating embedded Linux glitch attack.                                                                                           | 142   |

| 8.5  | Result of glitch attack on Android smartphone.                                                                                                              | 143   |

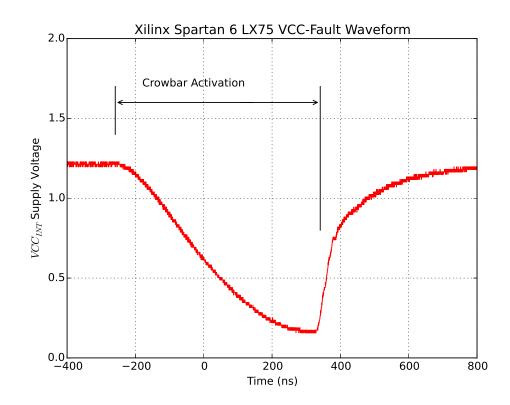

| 8.6  | Crowbar waveform on SAKURA-G platform                                                                                                                       | 144   |

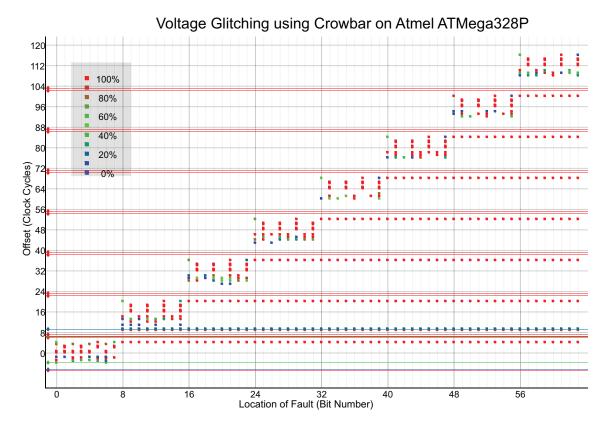

| 8.7  | Amount of FPGA configuration data corrupted based on length of crowbar activation                                                                           | 147   |

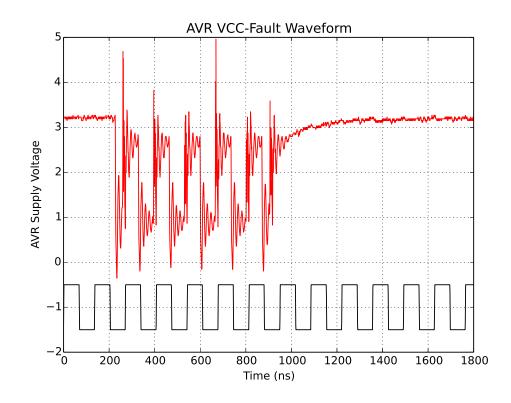

| 8.8  | Example of glitch waveform measured on ATMega328P                                                                                                           | 148   |

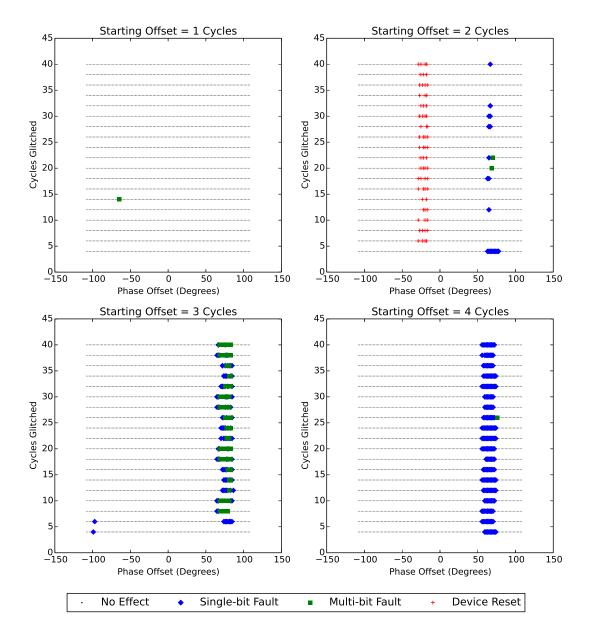

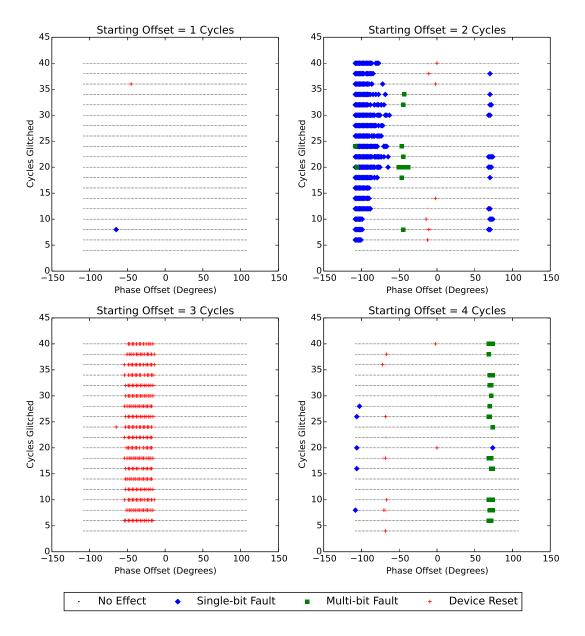

| 8.9  | Bit-set faults on ATMega328P compared to glitch parameters.                                                                                                 | 155   |

| 8.10 | Bit-reset faults on ATMega328P compared to glitch parameters.                                                                                               | 156   |

| 8.11 | Multi-bit faults on ATMega328P compared to glitch parameters.                                                                                               | 157   |

## Abstract

Embedded computers are unavoidable in our daily life, and our interaction with them only looks to increase as more products include the words 'Internet of Thing' in their selling features. Embedded computers can be found in our credit cards, in our cars, and in our thermostats. With such a wide distribution of embedded computers one might expect the companies designing and building them to look towards the large body of research present in academia about attacking and securing these devices.

But a gap exists between these two worlds, and the result can be seen in the many attacks against embedded devices presented every year at conferences such as Black Hat and DEFCON. This thesis introduces low-cost and open-source hardware and software that allows industry to more easily apply recent research publications, so this gap can be closed.

The fields of side-channel power analysis and fault injection allows us to successfully attack even strong cryptographic protocols, as these protocols can be broken when implemented on embedded devices. Understanding these attacks is critical to build strong devices that have to resist attacks for the next five to twenty years, especially where the devices may have limited ability to be updated. In addition to introducing a novel architecture for the analysis tool, this thesis includes several examples of attacks against various devices including small microcontrollers, field programmable gate arrays, embedded Linux computers, and IEEE 802.15.4 wireless nodes.

# List of Abbreviations and Symbols Used

| $\oplus$     | X-OR Operation                                          |

|--------------|---------------------------------------------------------|

| K            | Secret encryption key                                   |

| $K_j$        | Byte j of secret key $K$                                |

| $\sigma_X$   | Standard deviation of X                                 |

| $\sigma_X^2$ | Variance of X                                           |

| $\mu_X$      | Mean of X                                               |

| r(t)         | Continuous-time function of time $t$                    |

| r[n]         | Discrete-time function of sample $n$                    |

| X            | Absolute value of X                                     |

| BW           | Analog bandwidth                                        |

|              |                                                         |

| ADC          | Analog to Digital Converter                             |

| AES          | Advanced Encryption Standard                            |

| ARM          | Advanced RISC Machines (type of 32-bit microcontroller) |

| AVR          | An 8-bit RISC microcontroller (not an abbreviation)     |

|              |                                                         |

| CAN          | Controller Area Network                                 |

| CCM          | Counter with CBC-MAC (AES Mode)                         |

| CPA          | Correlation Power Analysis                              |

| COTS         | Computer Off the Shelf                                  |

|              |                                                         |

| DCM          | Digital Clock Manager (part of Xilinx FPGAs)            |

| DES          | Data Encryption Standard                                |

| DIP          | Dual In-line Pin (IC packaging)                         |

| DPA          | Differential Power Analysis                             |

| DSO          | Digital Storage Oscilloscope                            |

| DUT          | Device Under Test                                       |

| EPROM  | Erasable Programmable Read-Only Memory            |

|--------|---------------------------------------------------|

| FPGA   | Field Programmable Gate Array                     |

| GND    | Ground, negative supply voltage                   |

| GSR    | Global Success Rate                               |

| HD     | Hamming Distance                                  |

| HW     | Hamming Weight                                    |

| IoT    | Internet-of-Things                                |

| LNA    | Low Noise Amplifier                               |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| OS     | Operating System                                  |

| PGE    | Partial Guessing Entropy                          |

| PSR    | Partial Success Rate                              |

| RAM    | Random Access Memory                              |

| SAD    | Sum of Absolute Differences                       |

| SoC    | System on a Chip                                  |

| SNR    | Signal to Noise Ratio                             |

| USB    | Universal Serial Bus                              |

| VC     | Varying Clock                                     |

| VCC    | Positive supply voltage                           |

# VCO Voltage Controlled Oscillator

## Acknowledgements

Pursuing a PhD was not something in my plans during my undergraduate program, and even for the first few years afterwards. But I owe a debt to Dr. Jacek Ilow for setting me on the pathway to [eventually] pursuing one. It was under Dr. Ilow's guidance I had my first publication as part of my undergraduate degree, and with that an introduction to academic research. Dr. Ilow was also instrumental in my decision to apply for the NSERC funding program, which gave me some flexibility on research topics.

It was then under Dr. Zhizhang Chen I started the PhD, and under his guidance that I discovered the area of embedded security that this thesis pertains to. Had he not provided the freedom for me to explore these areas, I am doubtful I would have had such a fruitful PhD. I know few PhD students who have had the opportunity to so completely explore their research area while still retaining careful guidance. Dr. Chen has also been instrumental in expanding my PhD experience to see the larger academic life including assisting other students, teaching undergraduate courses, and updating labs/courses.

Just as it takes a village to raise a child, so does it to raise a PhD student. My supervisory committee also includes Dr. Srinivas Sampalli (in addition to Dr. Chen & Dr. Ilow), and I remain grateful for their guidance at many PhD 'life events' which have been critical to refining my thesis topics. This has often included a substantial time commitment to review papers, proposals, and presentations. The final version of the thesis here also includes comments and suggestions from both my committee and the external examiner, Dr. Jens-Peter Kaps. I'm grateful for their detailed remarks, and giving me a last chance to fix errors before the final version is committed in perpetuity.

Of course, I owe a great debt to my parents John & Eleanor for sending me on the path of electrical engineering. They encouraged me from a young age, even though they did not work in this area themselves. They would take me to electronics shops and stores where I would spend what I'm sure (in retrospect) was an unreasonable amount of time looking at parts, skimming books, and asking questions of store owners. Nor did they question the solder marks on the kitchen table, magazine subscriptions, and electronics kits that didn't always work.

This thesis builds on the work of many that have come before me, and I'm grateful for both their open research, along with their willingness to answer questions from an unknown PhD student. This includes those working on open-source software and hardware, which this thesis makes use of. I hope I can contribute to future work by releasing much of the work I have completed in this thesis under open-source licenses.

During the completion of this thesis, the support of my family has been instrumental. My wife Hilary has put up with many late nights, my travel to conferences, and once again solder marks on the kitchen table. I remain eternally grateful for her love, support, and encouragement for me to switch to lead-free solder.

# Chapter 1

## Introduction

#### 1.1 Background

The Internet of Things (IoT) is one of the most popular markets of electronic devices, with forcasts expecting over \$10 trillion a year of economic value by 2025 [63]. While some would question if an internet connected pet feeder is truly needed (and the resulting problems that happens when it breaks down due to a server failure[83]), the IoT market is a demonstration of what is possible with continuing advancements in embedded computer systems.

Embedded computers are typically a small task-specific computer contained within a larger system. Embedded computers are found in almost every market: within consumer goods you would find one within a smart thermostat (such as a Nest), digital camera, or an alarm system; within the automotive environment of typical car you could find 30 or more small computers, controlling everything from the engine to raising and lowering windows[131]; and within aerospace these embedded computers could be found running the autopilot on passenger aircraft, within the entertainment system, and logging critical flight parameters to the black box.

These embedded computers have continuously gained more processing capability, while at the same time requiring less electrical power to operate, and with a lower cost. As an example in 1996 a typical embedded processor for a low-cost application might be the Microchip PIC16C711, which had 1000-unit pricing of \$3.53 (approximately equivalent to \$5.36 in 2016 dollars)[86]. The PIC16C711 had 1KByte of EPROM program memory and 68 bytes of RAM, 4 channel ADC, and operates at up to a 20 MHz clock.

In 2016, for \$0.62<sup>1</sup> at 1000-unit pricing one can get a STM32F030F4P6 device which has 16Kbyte of FLASH memory, 4KByte of RAM, an 11 channel ADC, and operates at up to a 48 MHz clock. For \$4.93 a ATSAM4S16CA-AU device has 1MByte

<sup>&</sup>lt;sup>1</sup>Pricing based on Digi-Key prices in October 2016

of FLASH memory, 128KByte of RAM, operates at up to 120 MHz, and includes many peripherals such as ADCs and USB. Even more advanced devices integrate WiFi and other wireless communication interfaces, and are available at very low cost in higher quantity.

The growth of more advanced processors being available at lower cost is of great interest from a security perspective. Many consumer electronics now run small operating systems, even if the task being performed is fairly simple. The Philips Hue is a smart lighting system, yet its main bridge runs Linux and contains two microcontrollers [102]. Often this is done to simplify development – writing very small embedded code from scratch is time-intensive, and may be difficult to modify or update in the future. But if the product is developed on-top of an OS (such as Linux), the developers can take advantage of the underlying OS for features such as networking, routing, file systems, and web communication.

These more complex systems often have more attack vectors someone could potentially exploit. And if they are able to get access to a system, they may be able to perform more damaging attacks. For example a Nest wireless thermometer may have a wireless interface connected to smart lights, and a wireless interface connected to the home network. Could someone attacking the smart lights use the Nest thermometer as a bridge to attack the home network?

Such bridging has already been demonstrated. In 2015 researchers showed how they could hack a Jeep Cherokee remotely, sending messages on the local network of the car over a cellular connection [55, 87]. These local messages allowed almost complete control of car systems - they could perform everything from turning on windshield wipers to turning off the engine. It was possible to perform these attacks only after significant reverse engineering of the embedded computers, and finding ways to remotely reprogram several embedded computers, before it was finally possible to bridge messages from the external cellular modem onto the local automotive CAN network.

Security considerations are a required part of embedded design in this environment. This becomes especially important as more devices are equipped with networking and communication capabilities, giving them the ability to be used as part of a larger attack, even if the specific device in question does not perform important duties.

Typical solutions that are applicable on PCs, such as using strong encryption, may be either more difficult or considerably less effective on embedded systems. For example differential power analysis (DPA) [72] can break a perfect implementation of AES, making it trivial to attack a device even though it uses encryption to protect the firmware.

While many of the lessons learned protecting PCs from virus and security threats are relevant, there is a rather large additional body of knowledge on security threats that are specific to the embedded environment. Designers of embedded systems must be aware of these threats in order to design secure embedded systems.

#### 1.2 Motivation

Despite the importance of security on embedded systems, many products are released with insufficient protection against attackers. These security threats should be wellknown by now – DPA as a method of breaking encryption has been publically disclosed for 18 years. Yet the continual use of unprotected encryption routines shows that engineers are either unaware of the threat or do not take it seriously [107].

Before starting this PhD, I had worked at Atmel on various projects related to IEEE 802.15.4 wireless protocols, including the ZigBee-IP Standard [4]. During this time I worked on both embedded system design and protocol specifications, and part of this work included discussions around security considerations. In these discussions the types of attacks discussed in my thesis were relatively unknown by most engineers (myself included at the time), and generally it was assumed they were not a practical threat. This was almost entirely due to my unfamiliarity with performing them myself – it's difficult to gauge the relevance of these attacks without practical experience.

While engineers may be familiar with the existence of these attacks, it is very rare to find a general embedded engineer who has actually performed them. Universities doing this research might expose their undergraduate engineers to the problem, but the majority of engineering students would have seen these attacks only in a theoretical lecture, if they were mentioned at all.

It was clear to me that not only is more research needed in pushing these attacks forward, but it's needed to make this research available for use by both academics and engineers in industry. Bridging this gap is critical for ensuring products being developed in industry remain secure for their expected lifetime. What is needed is that any embedded designer is not only aware of the attacks, but has actually performed them and is able to understand how they apply to systems they are designing.

#### **1.3** Contributions of the Thesis

My motivation of both performing fundamental new research, along with helping to make this work available for a wider audience has shaped the direction of this thesis. The main contributions are related to three areas: design of a large open-source platform for performing the attacks, new methods of performing fault attacks, and further examples of attacking devices used in the development of products.

#### 1.3.1 Capture Tools

The most major contribution made in this thesis for embedded side-channel power analysis is the ChipWhisperer open-source platform, discussed in Chapter 4. This platform was released as an open-source project, and has already been used in numerous academic papers by other researchers [19, 23, 40, 42, 43, 49, 61, 76, 79, 96, 97, 113, 148]. This platform contains both the hardware designs for building a measurement platform, along with the software required to drive this hardware and perform many types of attacks on embedded systems.

I had many talks at conferences related to this platform, including talks at industryfocused conferences such as Black Hat, DEFCON, SEC-T, and RECON. In addition I ran a tutorial at CHES on the use of this ChipWhisperer platform for building a very low-cost lab setup, and later used the ChipWhisperer platform as part of a capture-the-flag (CTF) event at CHES 2016.

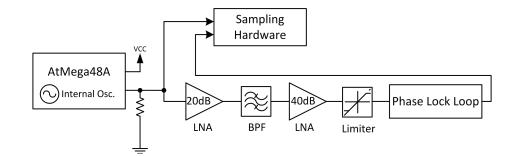

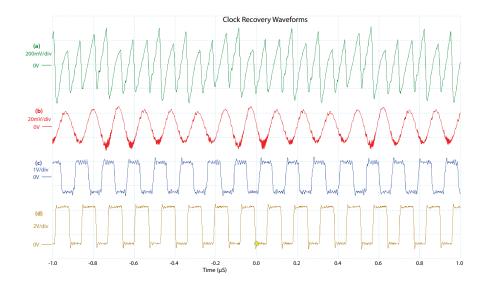

The capture tool work also built into development of novel techniques for preprocessing data, discussed in Chapter 5. This work demonstrates methods of performing 'clock recovery' both using a regular oscilloscope, and using my special ChipWhisperer platform. This clock recovery hardware opens up the ability to synchronize certain fault injection attacks to a device with an internal clock.

#### 1.3.2 Fault Attacks

Fault attacks may be one of the most powerful methods of breaking embedded systems. My work concentrated on the development of a simple 'crowbar' method of inserting faults, and demonstrating its advantages over previous systems. In particular, this method is able to achieve extremely high temporal accuracy (i.e., targeting a specific instruction). This method can also be readily applied to real devices, for example I target two different off-the-shelf embedded Linux computers in addition to an 8-bit microcontroller and a custom FPGA board. This is discussed in Chapter 8.

#### 1.3.3 Attack Examples

Finally, several examples of side-channel power analysis attacks are presented. The Atmel ATMega128RFA1 device was analyzed in Chapter 7. This chapter also demonstrates how to attack the device when it's running a standard IEEE 802.15.4 wireless stack. This requires development of several new techniques to work with the AES-CCM\* mode encryption used in this standard. It also required development of specific measurement techniques for use with this device, which are widely applicable to other IEEE 802.15.4 SoC devices from other manufactures.

I've also brought an example attack against an AES-256 bootloader, specifically one that was part of an app-note published by a microcontroller manufacture. This demonstrates how side-channel power analysis can be used to trivially break software implementations where engineers may blindly follow the suggested best practices from such app-notes.

#### 1.4 Outline of Thesis

The rest of this thesis is organized as follows – background on aspects of embedded hardware security covered in this thesis is presented in Chapter 2. This includes sidechannel power analysis and glitching attacks. The power measurement considerations are presented in Chapter 3, which are then built upon to develop the open-source ChipWhisperer platform in Chapter 4. Using this platform on practical devices may require the clock recovery techniques discussed in Chapter 5, as they allow these techniques to be applied in situations where no external clock is available. The next two chapters are practical attacks: first Chapter 6 breaks an AES-256 bootloader, and then Chapter 7 breaks an AES hardware accelerator along with providing considerations for breaking it during use with IEEE 802.15.4 wireless protocols. Chapter 8 details the novel power glitching method developed, and demonstrates this against several devices including a Raspberry Pi and a FPGA device. Finally Chapter 9 has some final remarks on this thesis, and what extensions can be made. Appendix A explicitly details my contributions made to the field during this thesis.

## Chapter 2

# **Background and Related Work**

The literature review that follows outlines the history of side-channel power analysis and other embedded hardware attacks. This has been split into two general sections – side-channel power analysis, and fault injection. Certain topics which are outside the scope of this thesis are not discussed, such as attacks involving the decapsulation of chips and directly probing the surface or attacking the decapsulated surface [5, 124].

#### 2.1 Side-Channel Power Analysis

It had been known that the power consumed by a digital device varies depending on the operations performed since at least 1998, when Kocher, Jaffe, and Jun showed the use of the power analysis for breaking cryptography[72]. The first example given was that of Simple Power Analysis (SPA), where knowing the sequence of operations would directly allow read-out of the secret key. Differences in power consumption for different operations allows breaking of cryptographic algorithms using SPA.

As an example, consider the source code from Listing 2.1. This code is taken from the file bigint.c of avr-crypto-lib, an open-source library for the AVR microcontroller. This particular function is used as part of the RSA crypto system.

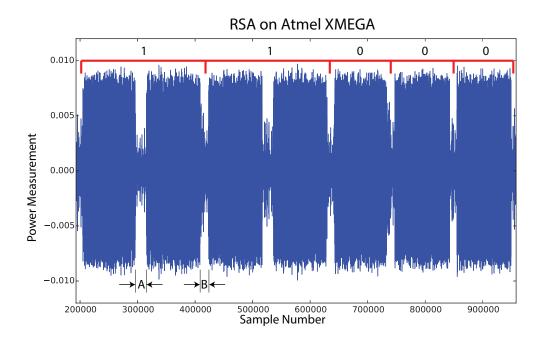

When a bit of the exp variable is 1 a square and multiply is performed, and when a bit of the variable is 0 only a square is performed. Looking at the power consumption, we can see some difference between a square and multiply operations. This is shown in Figure 2.1, where the code has been compiled onto an Atmel XMEGA microcontroller. The leakage in Figure 2.1 can be seen in the timing when a '1' is processed compared to a '0'. While both the square and multiply have similar power signatures on this platform, the delay on entering the square routine is slightly longer. The delay marked at "A" in this figure is about 80 mS, and the delay at "B" is about 60 mS. The slightly longer delay can very reliably be detected to determine if two function calls have occurred (square + multiply, indicating a '1') or only one function

Listing 2.1: The following lines are from bigint.c in avr-crypto-lib, showing an example implementation of the vulnerable RSA code.

```

uint8_t flag = 0;

t=exp->wordv[exp->length_W - 1];

for(i = exp->length_W; i > 0; --i){

t = exp - wordv[i - 1];

for(j = BIGINT_WORD_SIZE; j > 0; --j){

if(!flag){

if(t & (1 << (BIGINT_WORD_SIZE - 1))){</pre>

flag = 1;

}

}

if(flag){

bigint_square(&res, &res);

bigint_reduce(&res, r);

if(t & (1 << (BIGINT_WORD_SIZE - 1))){</pre>

bigint_mul_u(&res, &res, &base);

bigint_reduce(&res, r);

}

}

t <<= 1;

}

}

```

call (square, indicating a '0').

This particular variable that is leaked in this manner is not an arbitrary one, but instead knowledge of this variable leaks the value of the secret key used in this operation. Thus SPA allows us to directly break the secret key used during the operation.

While SPA is capable of breaking cryptography by deciphering operations, the same paper also presented a more powerful attack called differential power analysis (DPA) [72]. This seminal work demonstrated that there may be considerable problems with implementations of otherwise secure protocols on embedded hardware devices. In particular, this introduced the idea that measurements of the power could actually reveal something about the *data* on an internal bus, and not simply the

Figure 2.1: This exploits the data-path dependent code from Listing 2.1, which allows us to read the secret data off bit-by-bit.

overall operation.

Fundamentally, this is due to physical effects of how digital devices are built. A data bus on a digital device is driven high or low to transmit signals between nodes. The bus line can be modeled as a capacitor, and we can see that changing the voltage (state) of a digital bus line takes some physical amount of energy, as it effectively involves changing the charge on a capacitor.

There are several ways to use this knowledge. I'll discuss the main types of attacks used within this thesis, as well as summarizing some of the more recent work in the following sections.

#### 2.1.1 Attack Types

The initial attack presented in [72] caused a digital device to execute an operation with both known and secret data. If we consider the case where that known and secret data is mixed together, we could define the known data as P, the secret data as K, and the operation as C = f(P, K).

The DPA attack measures power consumption of the device during this operation.

We can measure  $i = 0, \dots, N$  such operations with random known input data  $P_i$ , and constant unknown secret data K. We could set K to some assumed value K'. Assuming that K is a single byte, this presents 256 possibilities for the value of K'.

For each possibility of K', we could have a group of hypothetical outputs of the operation  $C'_i = f(P_i, K')$  for each known input  $P_i$ , again where  $i = 0, \dots, N$ . At this point we wish to determine which value of K' matches the true value of K on the hardware device running the algorithm.

One method presented in [72] is to target a single bit of the value of C' (and hence K'). For each hypothetical value of K' we can separate the power traces into two groups: one where a bit of  $C'_i$  is '1', one where the bit is '0'. If our hypothetical value of K' matched the true value K, we would expect a difference at some point in the mean power consumption between the two groups.

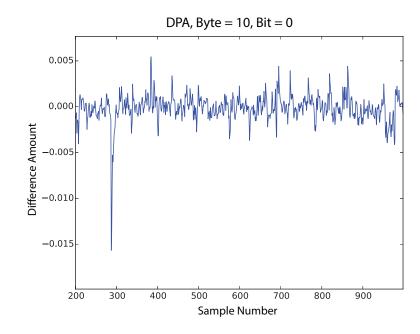

If our value was incorrect, we would expect no such difference, as the grouping could simply be considered as a random grouping of the traces into the two sets. In practice, such difference does exist when correctly grouped. Fig. 2.2 shows an example of the difference between the mean of two such groups, which have been correctly grouped into a set where the internal bit is '1' and the set where the internal bit is '0'. Note the trace shows us the location in time where the data is manipulated, as all other samples where the processor is *not* handling the data we targeted have the same mean.

This demonstrates that on a fundamental level devices do leak information regarding the state of the internal data bus. One additional consideration is how this can specifically be used to break cryptographic implementations, as it would appear this method still requires some level of "guess and check". This "guess and check" however is not performed over the entire key-space.

The implementation of cryptographic algorithms involves operations on individual bytes or words of data. For example although AES-256 involves a key of 256 bits (32 bytes), the "guess and check" for performing DPA only involves guessing a single bit at a time. This means a very tractable problem of performing  $2^1 \times 256$  guesses, something even a typical personal computer can accomplish in a few seconds.

The hypothetical output of some function we are targetting is typically referred to as the "intermediate value", as we are targetting some value within the entire

Figure 2.2: This demonstrates a DPA attack on a single bit, the large spike occurs at the instance in time where the processor is manipulating the data of interest.

operation of the algorithm. When attacking AES this is often after the first round of the SubBytes operation, as the non-linear property of the SubBytes improves our attack by eliminating the linear relationship between the input and intermediate values. In addition one byte of the plaintext will directly mix with one byte of the secret key, reducing the complexity of performing the guess and check operation.

While the DPA attack was the first proposed methods, more efficient methods of discovering the secret key information using the power traces exist. We'll discuss two major methods next: the Correlation Power Analysis (CPA) attack and template attacks.

#### Correlation Power Analysis (CPA)

Whereas DPA looked at simple differences between two groups of data, the CPA attack develops more precise assumptions on the power consumption and relation on an internal data bus. The CPA attack was first present in 2004 by Brier et al. in [22], and will be summarised here.

For a simple 8-bit microcontroller, we can use a "leakage model" that suggests the instantaneous power consumption is related to the number of bits set to '1' on the internal databus. This assumption is based on two factors: (1) our previous knowledge that moving the state of a line takes a certain amount of power, and (2) knowledge that microcontrollers set their internal buses to a constant state before the final value is loaded.

This constant state is known as the 'precharge' state. This precharge has been used since the early design of microcontrollers, where it was easier and faster to design a bus with precharge logic to pull the bus to the '1' state, requiring each module driving the bus to only have the pull-down logic (rather than requiring full push-pull and enable transistors on each bus connection)[84].

More recent devices may pre-charge to other levels, such as precharging to a level between '1' and '0', with the objective being to reduce the power and time required to transition to the final level [53]. This pre-charge would require push-pull drivers at each bus connection, so is targeting improved performance rather than a simplified design.

From an attack perspective, specifics of the pre-charge are irrelevant. Instead the attacker cares there is a constant starting level, meaning a linear relationship between the number of bits set to '1' on the databus and the power consumption. Depending on the precharge level and measurement style this relationship may have a positive or negative slope. Without this pre-charge we instead have a relationship between the *change* in bits between two bus states, and thus would also need to know (or guess) the previous state.

The case of the pre-charge will be referred to as the Hamming Weight (HW) model, where leakage is assumed to be related to the number of bits set to '1' on the bus. Without the precharge we would have the Hamming Distance (HD) model, where the leakage is related to the number of bits changing states on the bus.

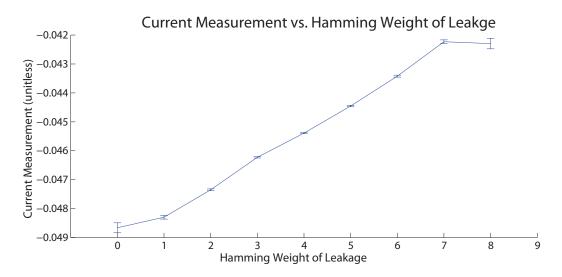

As a validation of this previous work, I have measured the power consumption of an 8-bit microcontroller (Atmel ATMega328P) at the moment it is manipulating data with various number of bits set to '1'. The results in Fig. 2.3 show an excellent relationship between the HW of the data and the power measurement.

The basic equation for a CPA attack, where  $r_{i,j}$  is the correlation coefficient at point j for hypothesis i, the actual power measurement is  $\mathbf{t}_{\mathbf{d},\mathbf{j}}$  of trace number dat point j, and  $p_{d,i}$  is the hypothetical power consumption of hypothesis i for trace

Figure 2.3: Power consumption of device under attack performing an operation on data with different Hamming Weights (HW), showing the average current consumption of the AtMega328P microcontroller for each possible hamming weight of an 8-bit number. Error bars show 95% confidence on average (based on the sample standard deviation).

number d, with a total of D traces is given in equation (2.1). This equation is simply an application of the Pearson's correlation coefficient given in equation (2.2), where  $X = \mathbf{p}$ , and  $Y = \mathbf{t}$ .

$$r_{i,j} = \frac{\sum_{d=1}^{D} \left[ \left( p_{d,i} - \overline{P_j} \right) \left( t_{d,j} - \overline{t_j} \right) \right]}{\sqrt{\sum_{d=1}^{D} \left( p_{d,i} - \overline{P_j} \right)^2 \sum_{d=1}^{D} \left( t_{d,j} - \overline{t_j} \right)^2}}$$

(2.1)

$$\rho_{X,Y} = \frac{\text{cov}(X,Y)}{\sigma_X \sigma_Y} = \frac{E\left[(X - \mu_X)(Y - \mu_Y)\right]}{\sqrt{E\left[(X - \mu_X)^2\right]}\sqrt{E\left[(Y - \mu_Y)^2\right]}}$$

(2.2)

The form given in these equations is referred to as the *normalized cross-correlation*, and frequently used in image processing applications for matching known templates to an image.

#### CPA as Matched Filter

While the CPA attack has been developed independently of similar work in communications theory, it is useful to recognize the parallel between the CPA attack and basic methods of recovering a signal in communications theory. In communications theory, the most basic problem statement is how to receive a signal that has been corrupted by Additive White Gaussian Noise (AWGN). The continuous-time and discrete-time interpretations of this problem are given as follows:

$$r(t) = s(t) + n(t)$$

(2.3)

$$r[n] = s[n] + w[n]$$

(2.4)

The transmitted signal or sequence s(t) or s[n] is one of several valid signals, the specific signal depending on the system. The objective of the communication systems is for the receiver to determine which of the possible symbols  $s_1(t), s_2(t) \cdots, s_N(t)$ was sent based on the received signal r(t).

The objective of receiving a known signal in Additive White Gaussian Noise (AWGN) has a well known solution, the matched filter (or 'North filter'), first described in 1943[99]. For a known signal s(t) transmitted over a channel with AWGN n(t), at the receiver we would have the received signal r(t):

$$r(t) = s(t) + n(t)$$

Which is then passed through the matched filter with impulse response h(t):

$$y(t) = r(t) * h(t) = \int r(\tau)h(t-\tau)d\tau$$

If we sample the output y(t) at t = T to make our decision, we will use the matched filter with the following impulse response:

$$h(t) = s(T - t), 0 \le t \le T$$

Thus leading us to find that:

$$y(t) = \int_{0}^{t} r(\tau)s(T - t + \tau)d\tau$$

Finally the value when we sample at T will become:

$$y(T) = \int_{0}^{T} r(\tau) s(\tau) d\tau$$

It can be noted this is equivalent (for t = T) to the cross-correlation of r(t) and s(t) at time t = 0:

$$y(t) = r(t) \star s(t) = \int r(\tau)s(t+\tau)d\tau$$

$$y(0) = \int_{0}^{T} r(\tau)s(\tau)d\tau \qquad (2.5)$$

The use of cross correlation for matching a known template is well known in computer vision as well, for example the use of cross correlation is presented in [77] with approximately the same form as equations (2.1).

The forms given in equations (2.1) and (2.2) force both r(t) and s(t) to be zeromean and normalized by standard deviation. This is necessary as we do not have proper scaling of the template s(t) used at the receiver.

Note again r[t] is the received signal, and s[t] is the transmitted signal. One critical difference between communications systems and side-channel power analysis is the definition of the argument of s(t). In communications we are sending a known signal  $s_n(t)$ , which may be drawn from a set of 'allowed' signals in the set  $s_1(t), s_2(t), \dots, s_N(t)$ . Each of these signals is typically a finite-length signal as a function of time (or samples in the discrete case). At the receiver we can use the matched filter to determine which of the N possible signals was transmitted.

For side-channel analysis, our function s(t) is actually defined over the number of cryptographic operations we observed. In equation (2.1) this was d, the 'trace index', and thus will be referred to as s(d). Each of the possible functions  $s_1(d), s_2(d), \dots, s_N(d)$  reflects the hypothetical value for the byte of the secret key we are attacking. Thus the matched filter comparison is always done at the same sample (i.e. time point) in each power measurement trace  $\mathbf{t}_d$ .

#### **Template Analysis**

The previous descriptions used an intuitive description of the physical hardware to produce a leakage model. For example we assumed a correlation between the number of ones on a databus and the power measurement at a single point in time. We can perform much more advanced analysis if we assume we have a copy of the device under our control; for example when attacking a specific IC with a secret key, we may have another IC from the same batch which we can program with a known secret key.

In this manner we will not make assumptions about the leakage. Instead we will build 'templates' of known leakages for specific values or attributes of the secret key using our copy of the device. We can then compare leakage from the actual device with our templates to determine the most likely value of the secret.

This template attack makes it possible to recover a secret key using only a single measurement, as we can build templates for each value of each byte of the secret key. Template attacks were published before the CPA attack, being described in 2002 by Chari et. al. [30].

To describe the template attack, I'll first take the case of the CPA attack where we consider only a single point of interest at a time. To generate a template set we could keep the input plaintext  $P_d$  fixed for each power measurement  $t_d$ . We'll instead vary the known encryption key K, such that each trace has a known and random key  $K_d$ , again where d is the trace index. Assuming the key  $K_d$  is made of a number of bytes (such as AES-128 having 16 bytes for each key), we can further look at each byte j of the key used for trace d, called  $K_{d,j}$ .

With a set of power traces  $t_d$  there is thus an associated value for the secret key  $K_d$  used on each trace d. Looking at the entire set of power traces, the power traces could be then grouped into different groups  $\mathbf{t_{K_j=g}}$ , where g is the value of secret key byte  $K_j$  in the range of  $\{0, 1, \dots, G\}$ . For example if we were attacking AES-128, we would first look at byte j = 0. Because this is a single byte, we would make 256 sets of power traces, one for each possible value of  $K_0 = \{0, 1, 2, \dots 255\}$ . If D = 100000, there would be about 390 power traces in each set.

Assuming we have a single point of interest l = l' within each trace  $t_{d,l}$ , we could determine the sample mean  $\overline{\mu}_g$  and variance  $\overline{\sigma}_g^2$  of each population. Being given a trace where the secret key is *unknown*, the problem becomes one of simply determining the most likely population the associated power trace for the unknown secret key belongs too. This gives us the value for g, which can then be mapped to the value of a secret key byte.

In practice, the template attack is extended to represent multi-variate random variables. That is rather than taking a single point in the template, we consider multiple points within the power trace  $t_{d,l}$ . This improves the templates ability to distinguish between the various populations in selecting the most likely value of the unknown byte.

Note templates do not necessarily need to directly provide the exact value of the unknown secret key. Instead a template could be built for possible Hamming weights of some known intermediate value, and the result of the template is used in a similar manner to the CPA attack to determine the most likely secret key value.

One of the difficulties of applying a template in real-life applications is finding a closely matched "copy" of the device under test. In an ideal situation, the attacker would be able to reprogram the actual device being attacked. Practical work has demonstrated that template attacks can still be applied even when this is not possible, although additional work may be required for a successful attack [109, 31].

While template attacks are not used in my thesis results, I have built several examples of their use and application available on the ChipWhisperer wiki at http: //www.chipwhisperer.com. More details of the ChipWhisperer project will be presented in later chapters.

#### 2.1.2 Implementation Leakage and Success Rate

Measuring the effectiveness of an attack toolchain is critical to understand and compare attack methods, capture hardware, and countermeasure potency.

There are two general methods of performing this assessment. The first method is to perform an empirical measurement of how successful a given attack was against a specific measurement setup. This success-based measurement demonstrates how well an entire attack works, and the specific amount of work required to break a given implementation. This measurement can be affected by a change anywhere in the attack toolchain – from physical setup differences to attack algorithm. A number of such measurement techniques are detailed in [128], and for example used in the DPA Contest v2 results summary [34].

The second general method is to measure an indicator of the "leakage" coming from a given system. This simplifies analysis of systems where the most effective exploitation technique of a specific system is unknown. It is possible for example a system is highly secure against one specific attack, but even a slight change in attack setup will cause the system to be highly vulnerable.

The leakage-based measurement does not demonstrate how to break a system, and often provides only a lower bound on the work required to break the system. It is possible a system may be considered highly leaky based on these metrics, but a practical method of attacking the system is unknown.

#### Global Success Rate (GSR)

The Global Success Rate (GSR) is an empirical performance measurement that directly measures if an attack was successful. This measurement can directly demonstrate how difficult it is to completely break an implementation using side-channel power analysis.

If the attack algorithm has access to N traces, we can consider the attack successful if the algorithm successfully determines the correct encryption key with N traces. We can present a number of different sets of N traces, and average the number of times the entire encryption key was successfully recovered with a set of size N.

This gives us the 'global success rate', where a rate of 1.0 means the attack always succeeds. Typically we will consider an attack successful for a GSR about 0.8, i.e. given a specific number of traces, the attack succeeds 80% of the time.

The GSR only indicates when the attack is completely successful – in reality it is sufficient to reduce the guessing entropy to a tractable level, instead of requiring the attack to directly give us the complete encryption key. Another metric which provides a measure of the reduction of guessing space is discussed next.

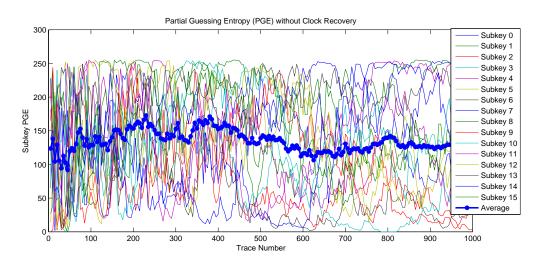

#### Partial Guessing Entropy (PGE)

The 'guessing entropy' is defined as the "average number of successive guesses required with an optimum strategy to determine the true value of a random variable X"[81]. The 'optimum strategy' here is to rank the possible values of the subkey from most to least likely based on the value of the correlation attack (higher correlation output is more likely).

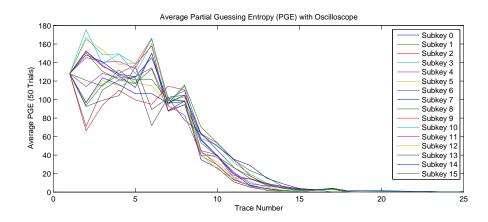

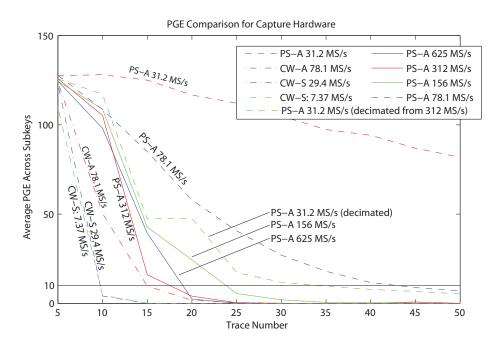

The 'partial' refers to the fact that we are finding the guessing entropy on each subkey. This gives us a PGE for each of the 16 subkeys. A PGE of 0 indicates the subkey is perfectly known, a PGE of 10 indicates that 10 guesses were incorrectly ranked higher than the correct guess.

The attack algorithm is given access to  $1, 2, \dots, N$  traces, and the PGE for each subkey is calculated. To improve consistency the PGE for each subkey is averaged over several attacks (trials). Finally, we can average the PGE over all 16 subkeys to generate a single 'average PGE' for the attack.

#### Leakage Measurement

The PGE and GSR require an attacker to know how to break a device. That is knowledge of the algorithm under test, leakage type, and particulars unique to the hardware or software cryptographic functions. Often designers of secure hardware only care about the *existence* of leakage. This means not necessarily determining how to break a device, just if a device appears to have some leakage that might be exploitable.

One of the most popular techniques uses a test-vector leakage assessment (TVLA), detailed in [54, 35]. This applies a set of preselected test vectors (test vectors being the input and secret key), and performs a statistical test on the power measurement during the test vector application. Briefly, these tests are typically applying a test vector from one of two 'groups' (such as a random or fixed group). If it is possible to determine a difference between the groups using side-channel measurements, this suggests there must be some information leakage.

The TVLA is typically performed by applying Welch's t-test to the two populations, where the two populations being tested are the power measurements recorded during each of the two different test vector groups. The t-test allows us to determine if the two measurement groups are distinguishable or not – we can simply specify some desired confidence, and the t-test provides a simple numerical output which is either above or below this threshold.

Assume the two groups were formed by grouping the complete set of traces  $\mathbf{t}$  into  $\mathbf{t} \in g_1$  and  $\mathbf{t} \in g_2$ . The set mean, variance, and cardinality is denoted by  $\mu(\mathbf{t} \in g_n)$ ,  $\sigma^2(\mathbf{t} \in g_n)$ , and  $|\mathbf{t} \in g_n|$  respectively.

Performing Welch's t-test requires the application of 2.6 to the two data sets. This test is used to determine the validity of the null hypothesis that the two sets of samples come from the same population. If the test suggests we cannot reject the null hypothesis, this means we cannot determine which population  $g_1$  or  $g_2$  a given sample came from using the power measurement.

$$t = \frac{\mu\left(\mathbf{t} \in g_{1}\right) - \mu\left(\mathbf{t} \in g_{2}\right)}{\sqrt{\frac{\sigma^{2}\left(\mathbf{t} \in g_{1}\right)}{|\mathbf{t} \in g_{1}|} + \frac{\sigma^{2}\left(\mathbf{t} \in g_{2}\right)}{|\mathbf{t} \in g_{2}|}}}$$

(2.6)

Typically, the t-test is used with a fixed threshold where if |t| > 4.5, it indicates an ability to determine which population  $g_1$  or  $g_2$  a given power trace measurement came from. This means the device has some data-dependent leakage we may be able to exploit. See [54] for details of this threshold, including determining specific values for desired confidence intervals and with certain set sizes.

Care must be taken in applying the t-test, as it simply indicates a difference in the mean of the sample groups, and not specific cryptographic leakage. All other (non-cryptographic) leakage must be carefully controlled – for example one cannot apply all of the test vectors from group 1, and then all of the test vectors from group 2. There will likely be a difference in the means between these two groups due to variation in environmental conditions (such as voltage and temperature), which the t-test metric will detect. Full consideration of this is discussed in [54, 35].

An improvement to the basic t-test is presented in [41], which also includes a reference to a number of academic publications showing the use of t-test results in analyzing hardware devices. In particular [91] shows an example of the use of a t-test to determine an appropriate leakage model, and then applying this leakage model with CPA to break a hardware AES implementation.

# 2.2 Fault Injection

Faults cause a computer program to behave in an unintended manner. For many systems this could have dire consequences, and protecting systems from such faults is an important area of research. Fault injection encompasses the techniques which are used to purposely cause faults to occur, for example as part of validating or testing a fault-tolerant or fault-detecting scheme[116]. Fault injection is also useful as a testing tool when designing for environments likely to cause single-bit failures, such as space applications or high-radiation environments [25].

Fault injection is also a powerful tool to break cryptographic algorithms. The previous example assumed the 'dire consequences' of a fault occurring were a result of the system performing an unexpected action. But a fault could be purposely injected to cause a system to behave abnormally, to an attackers advantage. It has been well known that a variety of fault injection methods can be used for this purpose[6, 14].

Previous work on fault injection has demonstrated methods of breaking cryptographic algorithms such as DES[20], AES[45, 32, 16], and RSA[21, 120, 15] by introduction of faults at specific parts of the algorithm. Of these, a practical demonstration of the proposed method is also given in [32, 120, 16, 15]. All of these demonstrations are performed on a custom board, specifically designed to inject faults into the embedded computer running the cryptographic algorithm. The reader is referred to [17] for a more detailed survey of attacks on AES and RSA.

## 2.2.1 Non-Cryptographic Attacks

Fault injection is powerful as it can be used to attack almost any aspect of an embedded system (not just cryptographic functions), but still achieve very damaging results. For example consider the C code of Listing 2.2, which is a hypothetical implementation of a response buffer in an embedded system. A fault attack could cause the value of i (or *strlen*) to become corrupt. This is made worse as compilers may replace the 'less than' comparison with a simple 'branch if not equal', which is only looking for the exit value. A fault which causes the i value to become larger than strlen will print the entire memory after the *str* buffer until the counter rolls over.

If this was a 32-bit system, the default integer size (of 32-bits) would mean it could dump the entire memory address space. If both RAM and code memory exist on the same address space (common on processors such as ARM), this would allow an attacker to receive both the code and data memory contents. This can be applied on more complex systems, such as M. Scott demonstrated by glitching a device with USB to dump an entire firmware image [121]. The work in [121] used the ChipWhisperer platform to inject a voltage glitch for this attack.

Listing 2.2: A simple puts() style routine with an added length field to avoid issues with unterminated strings.

```

void puts(char * str, int strlen){

for(int i = 0; i < strlen; i++)

putch(*(str + i));

}

}</pre>

```

# 2.2.2 Methods of injecting faults

A detailed survey of fault injection methods will be presented in Chapter 8, so only a brief summary will be replicated here.