# CENTRAL CONTROL PROGRAM INSTRUCTIONS NO. 1 ELECTRONIC SWITCHING SYSTEM

|    | CONTENTS                                       | PAGE | CONTENTS                              | PAGE |

|----|------------------------------------------------|------|---------------------------------------|------|

| 1. | GENERAL                                        | . 2  | RESULTANT DAR ADDRESS                 | . 9  |

| 2. | INFORMATION CONTAINED ON A PROGRALLISTING PAGE | _    | LOGICAL ZERO                          | . 9  |

|    | ADDRESS COLUMN                                 | . 3  | 4. LOGICAL OPERATIONS                 | . 9  |

|    | ENCODED INSTRUCTION COLUMNS .                  | . 3  | LOGICAL PRODUCT (AND)                 | . 9  |

|    | EDITOR LINE AND MACRO LEVEL NUMBI              | _    | LOGICAL UNION (OR)                    | . 9  |

|    | A. Editor Line Number                          | _    | EXCLUSIVE OR                          | . 9  |

|    | B. Macro Level Number                          | . 7  | 5. ABBREVIATIONS IN THE OPERATION COD | _    |

|    | LINE NUMBER COLUMN                             | . 7  | ORIGINS AND DESTINATIONS              | . 9  |

|    | SYMBOLIC INSTRUCTION FORMAT .                  | . 7  | OPERATIONS                            | . 10 |

|    | A. Location Field                              | . 7  | CONDITIONS                            | . 11 |

|    | B. Operation Field                             | . 7  | SPECIAL INDICATORS                    | . 11 |

|    | C. Variable Field                              | . 7  | 6. VARIABLE AND OPTION FIELDS         | . 11 |

|    | COMMENT FIELD                                  | . 8  | DA SUBFIELD                           | . 12 |

| 3. | PROGRAMMING TERMS                              | . 8  | R SUBFIELD                            | . 12 |

|    | INDEXING                                       | . 8  | M SUBFIELD                            | . 12 |

|    | INDIRECT TRANSFER                              |      | L SUBFIELD                            |      |

|    | EFFECTIVE DA NUMBER                            |      | CJ SUBFIELD                           |      |

|    |                                                |      |                                       |      |

# NOTICE

Not for use or disclosure outside the Bell System except under written agreement

|    | CONTENTS                                | PAGE | CONTENTS PAGE                                                                                 |

|----|-----------------------------------------|------|-----------------------------------------------------------------------------------------------|

| 8. | FLOW DIAGRAMS                           | . 14 | F. Interrupt Combined Instructions 82                                                         |

|    | BASIC OPERATIONS                        | . 16 | MAINTENANCE AND SPECIAL PURPOSE INSTRUCTIONS 83                                               |

|    | GENERAL PURPOSE OPERATIONS              | . 19 |                                                                                               |

|    | A. Move Operations                      | . 19 | 9. GLOSSARY 94                                                                                |

| 1  | B. Add Operations                       | . 27 |                                                                                               |

| •  | C. Subtract Operations                  | . 29 | FIGURES                                                                                       |

| I  | D. Compare Operations                   | . 31 | 1. Sample of a Program Listing Page 6                                                         |

| !  | E. Logical Operations                   | . 34 | 2. Breakdown of Encoding Columns 7                                                            |

|    | F. Transfer Operations                  | . 44 | 3. Symbols and Abbreviations Used in Flow Diagrams                                            |

|    | G. Combined Shift and Rotate Operation  |      |                                                                                               |

|    |                                         |      | TABLES                                                                                        |

|    | H. Double Destination Operations .      | . 56 |                                                                                               |

|    | I. Miscellaneous Operations             |      | A. Alphabetic Listing of Instruction  Mnemonic Codes Referenced to Instruction                |

|    | INPUT-OUTPUT INSTRUCTIONS               | . 60 | Definitions 4                                                                                 |

|    |                                         |      | B. Categorical Index of Operation Codes                                                       |

|    | RESTRICTIONS ON INPUT-OUTPUT            | _    | 5                                                                                             |

|    | INSTRUCTIONS MA, WA, MAS, WAS, MSF      | F,   |                                                                                               |

|    | AND WSF                                 | . 69 | C. Sample Instruction Encoding 14                                                             |

|    | A. K (Accumulator) Restrictions         | . 69 | 1. GENERAL                                                                                    |

|    | B. F Register Restrictions              | . 70 |                                                                                               |

|    |                                         |      | 1.01 This section describes the program instructions                                          |

|    | C. Y Register Restrictions              | . 70 | used by the central control (CC) of the 2<br>Wire No. 1 Electronic Switching System (ESS) and |

|    | D. L Register Restrictions              | . 70 | 4-Wire No. 1 ESS. Also included are the octal codes associated with the instructions and flow |

|    | COMBINED INSTRUCTIONS                   |      | diagrams which describe the gating of the instructions processed by the CC.                   |

|    | A. General Purpose Combined Instruction | ıs   |                                                                                               |

|    |                                         |      | <b>1.02</b> This section is reissued for the following reasons:                               |

|    | B. Dial Pulse Scan Combined Instruction |      | ( )                                                                                           |

|    |                                         | . 72 | (a) To include Issue 2 Addendum 3                                                             |

|    | C. Line Scan Combined Instructions .    | . 75 | (b) To revise paragraph 8.144                                                                 |

|    | D. Trunk Scan Combined Instructions     | . 77 | (c) To make minor corrections                                                                 |

|    | E. Network Combined Instructions .      | . 79 | (d) To add Part 9 Glossary.                                                                   |

Since this is a general revision, change arrows ordinarily used to indicate changes have been omitted.

1.03 The instruction definitions and flow diagrams are shown in Part 8. Flow diagrams show the timing of instruction gating in the CC. The instructions are referred to by mnemonic codes. These codes are listed alphabetically in Table A with references to the instruction definitions shown in Part 8.

1.04 The program instructions are also listed in another form as shown in Table B. Here the instructions are grouped according to category. The categories are identical to those given in Part 8 (Flow Diagrams). Table B is useful to find a particular CC instruction when a general form of the job to be carried out is known, such as an input-output job.

# 2. INFORMATION CONTAINED ON A PROGRAM LISTING PAGE

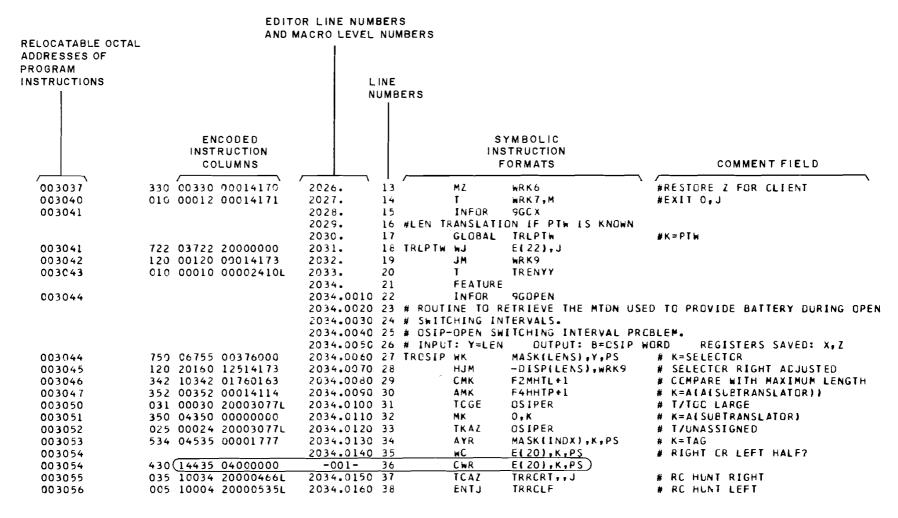

2.01 A program listing (PR) is a computer generated list of instructions and related information for a program unit(s). A program unit is called a PIDENT (program identification). In order to interpret the instructions contained in a PIDENT, there should be an understanding of the information contained in a list of instructions (PR). Figure 1 gives an example of a typical list of program instructions on a page of a PR.

# **ADDRESS COLUMN**

The left-most column of seven print positions contains the octal addresses, either relocatable or absolute, of the program instructions. A relocatable address is represented by only six print positions, whereas an absolute address occupies all seven print positions. A relocatable address is relative to the PIDENT's actual starting address, which can be found in the program map. The absolute address gives the actual program store (PS) address where the instruction is contained on the memory card. To get the absolute address for an instruction with a relocatable address in the PR, locate the actual octal starting address of the pident in the program map (PK-1A002-XX) and add the relocatable octal address to it. The addresses shown in Fig. 1 are relocatable addresses. If these columns are blank, then the line is used for an auxiliary purpose such as a programmer's comment, control card, macro name, etc.

#### **ENCODED INSTRUCTION COLUMNS**

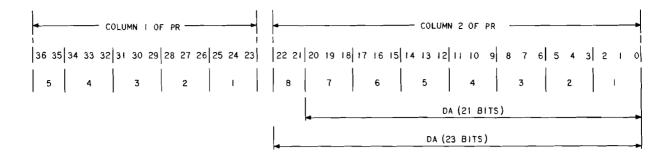

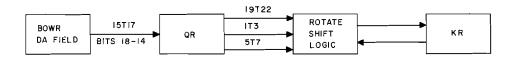

The two columns of five and eight octal 2.03 digits in Fig. 1 represent the instruction in octal, without Hamming or parity check bits. (The 3-digit column preceding the encoding columns is used as a programming tool during system testing and is not discussed.) The five octal digits of the first column, representing bits 36 through 23 with the most significant octal digit representing bits 35 and 36, contain the encoding of the basic instruction and most of the options. The eight octal digits of the second column, bits 22 through 0, include the data or address (DA) field of the instruction. The DA field may consist of 23 or 21 bits depending on whether bits 22 and 21 are required to represent the octal encoding of the instruction. If the octal encoding for an instruction can be fully represented in bits 36 through 23, the DA field consists of 23 bits (0 through 22). For some options, bits 21 and 22 are included with bits 36 through 23 in representing the octal encoding for an instruction. In this case, the DA field consists of only 21 bits (0 through 20). In either case, the most significant octal digit of columns one and two represents only two bits. (The octal digit will not be greater than three.)

2.04 The combined shift or rotate instructions make use of additional bits to further define the particular instruction. In addition to the bits already discussed, bit 19 is used to indicate the direction of shift or rotation and bits 18 through 14 specify the amount of shift or rotation.

2.05 The letter L appended to column two of encoded instruction columns (Fig. 2) indicates that the DA field is a relocatable address. The letter V appended to column two indicates that this location contains a reference into a transfer table. This table contains the address for the transfer.

# **EDITOR LINE AND MACRO LEVEL NUMBER**

# A. Editor Line Number

2.06 The editor line number is inserted by an editor program which may be used in the assembly of the PR. The form of the number is

TABLE A

ALPHABETIC LISTING OF INSTRUCTION MNEMONIC CODES REFERENCED TO INSTRUCTION DEFINITIONS

| INSTRUC-<br>TION | PAR.<br>NO. | INSTRUC-<br>TION       | PAR.<br>NO. |

|------------------|-------------|------------------|-------------|------------------|-------------|------------------|-------------|------------------|-------------|------------------------|-------------|

| ABR              | 8.31        | нсмк             | 8.76        | LG               | 8.133       | PMY              | 8.48        | QZM              | 8.69        | TUPMK                  | 8.115       |

| AFR              | 8.31        | HCMKU            | 8.76        | LH               | 8.136       | PMZ              | 8.48        | SBR              | 8.35        | TZRFU                  | 8.108       |

| AJR              | 8.31        | HCØKM            | 8.80        | LM               | 8.15        | PWK              | 8.41        | SFR              | 8.35        | TZRFZ                  | 8.109       |

| AKR              | 8.31        | HFM              | 8.69        | LN               | 8.123       | PWX              | 8.47        | SJR              | 8.35        | UMK                    | 8.44        |

| ALR              | 8.31        | НЈМ              | 8.69        | MA               | 8.91        | PWY              | 8.47        | SKR              | 8.35        | UMKMJ                  | 8.112       |

| AMK              | 8.30        | HKU              | 8.139       | MAS              | 8.93        | PWZ              | 8.47        | SLR              | 8.35        | UMX                    | 8.50        |

| AWK              | 8.29        | HLM              | 8.68        | MB               | 8.17        | Q                | 8.53        | SMK              | 8.34        | UMY                    | 8.50        |

| AWRP             | 8.32        | нмв              | 8.70        | MBCS             | 8.145       | QAMK             | 8.75        | SWK              | 8.33        | UMZ                    | 8.50        |

| AXR              | 8.31        | HMBCS            | 8.70        | MBØP             | 8.125       | QBM              | 8.67        | SXR              | 8.35        | UWK                    | 8.43        |

| AYR              | 8.31        | HMC              | 8.71        | MC               | 8.18        | QC               | 8.54        | SYR              | 8.35        | UWX                    | 8.49        |

| AZR              | 8.31        | HMCII            | 8.72        | MCII             | 8.19        | QCMK             | 8.76        | SZR              | 8.35        | UWY                    | 8.49        |

| BG               | 8.132       | HMF              | 8.74        | MCLF             | 8.20        | QCMKU            | 8.76        | $\mathbf{T}$     | 8.57        | UWZ                    | 8.49        |

| BH               | 8.135       | HMJ              | 8.74        | MD               | 8.98        | QFM              | 8.69        | TAULM            | 8.118       | WA                     | 8.90        |

| BM               | 8.13        | HML              | 8.73        | MF               | 8.23        | QJM              | 8.69        | TAUMK            | 8.111       | WAS                    | 8.92        |

| BMAP             | 8.120       | HMX              | 8.74        | MFMK             | 8.82        | QLM              | 8.68        | TCAU             | 8.60        | WB                     | 8.25        |

| BMØP             | 8.121       | HMY              | 8.74        | MJ               | 8.23        | QMB              | 8.70        | TCAZ             | 8.60        | WD                     | 8.97        |

| BN               | 8.122       | HMZ              | 8.74        | MJMK             | 8.82        | QMBCS            | 8.70        | TCGE             | 8.60        | WF                     | 8.27        |

| CMK              | 8.37        | HØKM             | 8.79        | MK               | 8.22        | QMC              | 8.71        | TCGMX            | 8.116       | WJ                     | 8.27        |

| CMKU             | 8.39        | HPMK             | 8.75        | MKII             | 8.24        | QMCII            | 8.72        | TCLE             | 8.60        | WK                     | 8.28        |

| CWK              | 8.36        | HPMX             | 8.77        | ML               | 8.21        | QMF              | 8.74        | TCLU             | 8.60        | $ _{ m WL}$            | 8.26        |

| CWKU             | 8.38        | HPMY             | 8.77        | MLMK             | 8.82        | QMJ              | 8.74        | TCLZ             | 8.60        | WNPS                   | 8.142       |

| CWR              | 8.40        | HPMZ             | 8.77        | MSF              | 8.96        | QML              | 8.73        | TCM              | 8.60        | WSF                    | 8.95        |

| EE               | 8.83        | HSMK             | 8.75        | MX               | 8.23        | QMX              | 8.74        | TCMMF            | 8.117       | wv                     | 8.143       |

| EEF              | 8.88        | HUMK             | 8.75        | MXMK             | 8.82        | QMY              | 8.74        | TCP              | 8.60        | WX                     | 8.27        |

| EGBN             | 8.87        | HUMX             | 8.77        | MY               | 8.23        | QMZ              | 8.74        | TKAU             | 8.59        | WY                     | 8.27        |

| EMMS             | 8.144       | HUMY             | 8.77        | MYMK             | 8.82        | QØKM             | 8.81        | TKAZ             | 8.59        | wz                     | 8.27        |

| ENAM             | 8.85        | HUMZ             | 8.77        | MZ               | 8.23        | QPMK             | 8.75        | TKGE             | 8.59        | XGKU                   | 8.140       |

| ENTJ             | 8.58        | HXM              | 8.69        | MZMK             | 8.82        | QPMX             | 8.77        | TKLE             | 8.59        | XHKC                   | 8.141       |

| EXC              | 8.86        | HXMK             | 8.75        | NB               | 8.126       | QPMY             | 8.77        | TKLU             | 8.59        | XM                     | 8.16        |

| EZEM             | 8.84        | HYM              | 8.69        | NBTA             | 8.130       | QPMZ             | 8.77        | TKLZ             | 8.59        | XMK                    | 8.46        |

| $\mathbf{FG}$    | 8.134       | HZM              | 8.69        | NBTB             | 8.131       | QS               | 8.55        | TKM              | 8.59        | XN                     | 8.124       |

| FH               | 8.137       | JKMSF            | 8.110       | NF               | 8.129       | QSC              | 8.56        | TKP              | 8.59        | XWK                    | 8.45        |

| FM               | 8.16        | JM               | 8.16        | NJ               | 8.129       | QSMK             | 8.75        | TRAU             | 8.61        | YM                     | 8.16        |

| FN               | 8.124       | JN               | 8.124       | NK               | 8.128       | QUMK             | 8.75        | TRAZ             | 8.61        | YN                     | 8.124       |

| GBNHJ            | 8.119       | KG               | 8.134       | NL               | 8.127       | QUMX             | 8.77        | TRGE             | 8.61        | $\mathbf{z}\mathbf{m}$ | 8.16        |

| GKC              | 8.138       | KH               | 8.137       | $ _{NX}$         | 8.129       | QUMY             | 8.77        | TRLE             | 8.61        | ZN                     | 8.124       |

| H                | 8.51        | KM               | 8.14        | NY               | 8.129       | QUMZ             | 8.77        | TRLU             | 8.61        |                        |             |

| HAMK             | 8.75        | KMKUS            | 8.113       | NZ               | 8.129       | QXM              | 8.69        | TRLZ             | 8.61        |                        |             |

| нвм              | 8.67        | KMKXS            | 8.114       |                  | 8.42        | QXMK             | 8.75        | TRM              | 8.61        |                        |             |

| нс               | 8.52        | KN               |             | PMX              | 8.48        | QYM              | 8.69        | TRP              | 8.61        |                        |             |

TABLE B

CATEGORICAL INDEX OF OPERATION CODES

| CATEGORY                                              | OPERA                                                   | ATION                     | INSTRUCTIONS                                                                                                                                                                     |  |  |

|-------------------------------------------------------|---------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                       | MOVE                                                    |                           | BM, FM, JM, KM, LM, MB, MC, MCII, MCLF, MF, MJ, MK, MKII, ML, MX, MY, MZ, WB, WF, WJ, WK, WL, WX, WY, WZ, XM, YM, ZM                                                             |  |  |

|                                                       | ADD                                                     |                           | ABR, AFR, AJR, AKR, ALR, AMK,<br>AWK, AWRP, AXR, AYR, AZR                                                                                                                        |  |  |

|                                                       | SUBTRACT                                                |                           | SBR, SFR, SJR, SKR, SLR, SMK,<br>SWK, SXR, SYR, SZR                                                                                                                              |  |  |

|                                                       | COMPARE                                                 |                           | CMK, CMKU, CWK, CWKU, CWR                                                                                                                                                        |  |  |

|                                                       | LOGICAL                                                 |                           | H, HC, PMK, PMX, PMY, PMZ, PWK, PWX, PWY, PWZ, Q, QC, QS, QSC, UMK, UMX, UMY, UMZ, UWK, UWX, UWY, UWZ, XMK, XWK                                                                  |  |  |

| GENERAL<br>PURPOSE                                    | TRANSFERS                                               |                           | ENTJ, T, TCAU, TCAZ, TCGE, TCLE, TCLU, TCLZ, TCM, TCP, TKAU, TKAZ, TKGE, TKLE, TKLU, TKLZ, TKM, TKP, TRAU, TRAZ, TRGE, TRLE, TRLU, TRLZ, TRM, TRP                                |  |  |

|                                                       | STANDARD<br>SHIFT<br>AND<br>ROTATE<br>COMBINA-<br>TIONS | MOVE                      | HBM, HFM, HJM, HLM, HMB, HMBCS, HMC, HMCII, HMF, HMJ, HML, HMX, HMY, HMZ, HXM, HYM, HZM, QBM, QFM, QJM, QLM, QMB, QMBCS, QMC, QMCII, QMF, QMJ, QML, QMX, QMY, QMZ, QXM, QYM, QZM |  |  |

|                                                       |                                                         | $\overline{\mathrm{ADD}}$ | HAMK, QAMK                                                                                                                                                                       |  |  |

|                                                       |                                                         | SUBTRACT                  | HSMK, QSMK                                                                                                                                                                       |  |  |

|                                                       |                                                         | COMPARE                   | HCMK, HCMKU, QCMK, QCMKU                                                                                                                                                         |  |  |

|                                                       |                                                         | LOGICAL                   | HPMK, HPMX, HPMY, HPMZ, HUMK, HUMX, HUMY, HUMZ, HXMK, QPMK, QPMX, QPMX, QPMX, QUMK, QUMX, QUMY, QUMZ, QXMK                                                                       |  |  |

|                                                       | SPECIAL COMBINED<br>SHIFT OR ROTATE                     |                           | нсøкм, нøкм, оøкм                                                                                                                                                                |  |  |

|                                                       | DOUBLE DES                                              | STINATION                 | MFMK, MJMK, MLMK, MXMK, MYMK, MZMK                                                                                                                                               |  |  |

|                                                       | MISCELLANI                                              | EOUS                      | EE, EEF, EGBN, ENAM, EXC, EZEM                                                                                                                                                   |  |  |

| INPUT-OUTPUT                                          |                                                         |                           | MA, MAS, MD, MSF, WA, WAS,<br>WD, WSF                                                                                                                                            |  |  |

| COMBINED                                              |                                                         |                           | GBNHJ, JKMSF, KMKUS, KMKXS,<br>TAULM, TAUMK, TUPMK, TCGMX,<br>TCMMF, TZRFU, TZRFZ, UMKMJ                                                                                         |  |  |

| MAINTENANCE<br>AND SPECIAL<br>PURPOSE<br>INSTRUCTIONS |                                                         |                           | BG, BH, BMAP, BMØP, BN, EMMS, FG, FH, FN, GKC, HKU, JN, KG, KH, KN, LG, LH, LN, MBCS, MBØP, NB, NBTA, NBTB, NF, NJ, NK, NL, NX, NY, NZ, WNPS, WV, XGKU, XHKC, XN, YN, ZN         |  |  |

Fig. 1—Sample of a Program Listing Page

Fig. 2-Breakdown of Encoding Columns

XXXXX.XXXX or XXXXX, where the Xs are decimal digits.

#### B. Macro Level Number

- 2.07 A macro instruction, or macro, is an abbreviated form for a sequence of predefined instructions or comments. A macro is an instruction the PR assembly program interprets and converts into zero or more valid machine instructions. Whenever a macro is used, the predefined sequence of valid machine instructions is generated in place of the macro and placed in the PR.

- 2.08 The machine instructions generated by the macro are identified by the macro level number. The level number identifies which level of nested macros generated this line of the PR. The form of this number is recognizably different from the form of an editor line number. The number is of the form —XXX— where X is a decimal digit.

- 2.09 If a line in the PR does not come from the editor program or is not generated by a macro, this column remains blank.

#### LINE NUMBER COLUMN

2.10 This column is a sequence of two decimal digits which represent the line numbers on this page of the PR. These numbers start at 01 and may go up to 50.

# SYMBOLIC INSTRUCTION FORMAT

2.11 This format is comprised of three columns with each column representing a field. The left-most column is the location field; the middle

column is the operation field; and the right column is the variable field.

#### A. Location Field

2.12 The location field is used for assigning a symbolic address to an instruction which can then be referred to by other instructions in the program. If the first character in this field is a sharp sign (#), the complete line in the listing is a comment only.

#### B. Operation Field

2.13 The operation field contains the symbolic instruction codes or macro names. The instruction codes can consist of one to five letters. Macro names can be larger.

#### C. Variable Field

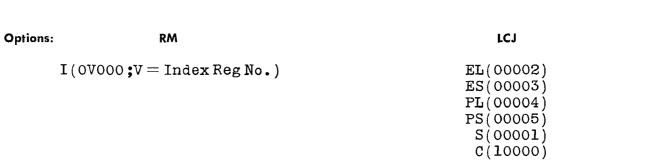

- 2.14 The variable and option fields form one undivided field on the programming form. The field consists of seven possible subfields: HQ, A, DA, R, M, L, and CJ. Not all of the subfields can apply to any one instruction. For programming convenience, the subfields are grouped by commas into three or four major subfields. For all instructions except the standard combined shift or rotate class, the grouping is DA, RM, and LCJ. For the standard combined shift or rotate instructions, the grouping is HQ, A, R, and LCJ. When a subfield is not required in an instruction, it is left blank or, in the case of the DA field, made zero. The seven subfields are briefly described as follows.

- (a) **HQ Subfield:** In the standard combined shift or rotate instruction, this subfield specifies the extent of the shift or rotation (bits 18 through 14) in decimal. Whether it is H,

HC, or Q is determined by encoding in bits 21 and 19.

- (b) *A Subfield:* In the standard combined shift or rotate instructions, this subfield specifies an address (or a part of an address when indexing is used) of limited size. Only 15 bits are used for this field, including the sign in bit 20 so that the absolute value of the contents of the A subfield cannot exceed octal 37,777 (16,383).

- (c) **Data or Address** (**DA**) **Subfield:** This subfield is used to specify either data or an address (or part of an address when indexing is used).

- (d) **R Subfield:** This subfield is used to specify one of the following CC registers:

| LETTER       | REGISTER                |  |  |  |

|--------------|-------------------------|--|--|--|

| В            | Buffer Register         |  |  |  |

| $\mathbf{F}$ | First One Register      |  |  |  |

| J            | Return Address Register |  |  |  |

| K            | Accumulator             |  |  |  |

| $\mathbf{X}$ | Index Register X        |  |  |  |

| $\mathbf{Y}$ | Index Register Y        |  |  |  |

| ${f z}$      | Index Register Z        |  |  |  |

If an instruction includes an option specifying register modification, the letter indicating the option also appears in the R subfield.

- (e) *M Subfield:* This subfield is used only for an indirect conditional or unconditional transfer. The presence of an M specifies an indirect transfer.

- (f) *L Subfield:* This subfield is used to specify the set logic register option (S) or logical masking option EL, ES, PL, or PS.

- (g) *CJ Subfield:* This subfield, when used, specifies the complement option C or the store return address option J.

# **COMMENT FIELD**

2.15 This field is reserved for explanatory comments, remarks, or references that may

be made by the programmer. This field is marked by a sharp (#) sign at the beginning of each comment.

#### 3. PROGRAMMING TERMS

#### INDEXING

**3.01** A number is indexed by a given register when the contents of that register are algebraically added to the number.

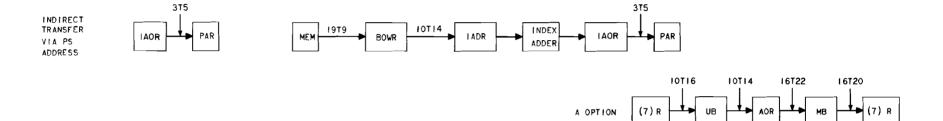

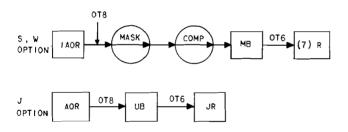

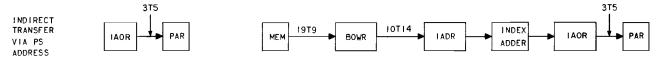

#### **INDIRECT TRANSFER**

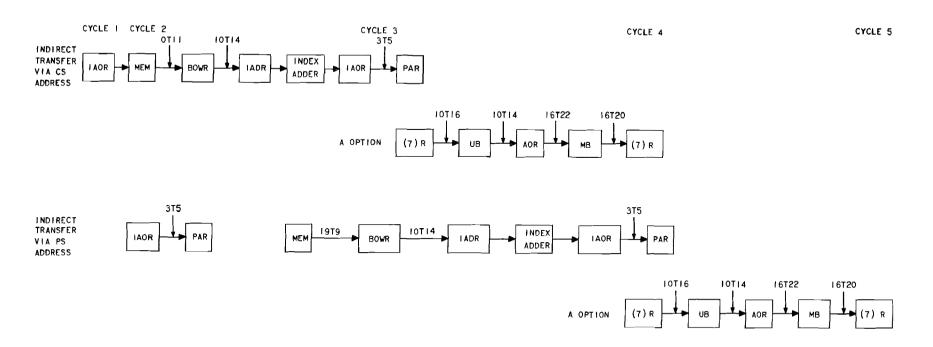

3.02 When an indirect transfer (conditional or unconditional) is specified by the appearance of an M in the M subfield, the initial address is the resultant DAR address. This initial address may be either a call store (CS) or PS address that contains (in bits 19 through 0) the address to which the transfer is made.

#### **EFFECTIVE DA NUMBER**

3.03 The effective DA number is the contents of the DA field unless an S, ES, or PS appears in the L subfield, in which case the effective DA number is defined to be zero. An S, ES, or PS in the L subfield specifies that the contents of the DA field are sent to the logic register (LR). For the standard combined shift or rotate instructions, the effective DA number is the contents of the A field, which may be blank or specify a signed number of absolute value not greater than 16,383 (octal 37777).

#### **RESULTANT DAR NUMBER**

- DA number indexed, if indexing occurs, by the contents of the register identified in the R subfield. The resultant DAR number consists of 22 data bits and a sign bit. When the DA field of an instruction consists of 21 bits (20 information bits and a sign bit), the field is expanded by inserting 0 or 1, whichever is in bit 20, into bit positions 21 and 22. During this expansion, if bit 20 of the DA field is a 1 and either or both bits 21 and 22 of the index register are ones, an overflow (end around carry) results if indexing occurs. The resultant DAR number can take one of the following forms:

- (a) The contents of the DA field plus the contents of an index register (provided that no S

appears in the L subfield and that indexing is used)

- (b) The contents of the DA field (provided no S appears in the L subfield and indexing is not used)

- (c) The contents of an index register (provided an S appears in the L subfield and indexing is available and used)

- (d) Zero (provided an S appears in the L subfield and indexing is not used).

#### **RESULTANT DAR ADDRESS**

the resultant DAR address is that part of the resultant DAR number that is actually used as an address in the execution of the instruction. The resultant DAR number is calculated as a signed number, 22 bits plus a sign bit, and is used as such by instructions treating it as data. When it is a transfer address (PS or CS, direct or indirect), a buffer bus register, or address of data in CS, bits 0 through 19 are treated as a positive address and bits 20 through 22 are ignored. When it is the address of data in PS, bits 0 through 20 are treated as a positive address and bits 21 and 22 are ignored. (A 1 or 0 in bit 20 specifies the left or right part, respectively, of a data word in the PS.)

# ARITHMETIC ZERO

3.06 Arithmetic zero can be either plus zero (all zeros) or minus zero (all ones). The C control flip-flop indicate arithmetic zero by a 1 in the homogeneity bit regardless of the state of the sign bit.

# **LOGICAL ZERO**

3.07 Logical zero is the all-zero state of a 23-bit word (plus zero). The C control flip-flops indicate logical zero by a 1 in the homogeneity bit and a 0 in the sign bit.

# 4. LOGICAL OPERATIONS

# **LOGICAL PRODUCT (AND)**

4.01 When two binary numbers are combined by the logical product (AND) operation, each bit of one binary number is matched with the corresponding bit of the other binary number.

When both bits are ones, the result is a 1. When either bit is a 0, the result is a 0. For example:

A = 1010

B = 0110

Logical Product = 0010

# **LOGICAL UNION (OR)**

4.02 When both binary numbers are combined by the logical union (OR) operation, each bit of one binary number is matched with the corresponding bit of the other binary number. When both bits are 0, the result is a 0. When either bit is a 1, the result is a 1. For example:

A = 1010 B = 0110 Logical Union = 1110

#### **EXCLUSIVE OR**

4.03 When two binary numbers are combined by the EXCLUSIVE OR operation, each bit of one binary number is matched with the corresponding bit of the other binary number. When these bits agree (both bits are ones or both are zeros), the result is a 0. When these bits do not agree (one bit is a 1 and the corresponding bit is a 0), the result is a 1. For example:

A = 1010 B = 0110 EXCLUSIVE OR = 1100

#### 5. ABBREVIATIONS IN THE OPERATION CODES

5.01 Letters appearing in the operation codes in the operation field have significant meanings. This part explains those letters.

## **ORIGINS AND DESTINATIONS**

5.02 The following letters mean the source from which information is moved or used or the

#### **SECTION 231-001-102**

location to which information is sent in the execution of an instruction:

- (a) **W:** The letter W appearing in the operation code designates the formation of the resultant DAR number W. The resultant DAR number is the effective DA number if indexing does not occur.

- (b) **M:** The letter M appearing in the operation code means **one** of the following:

- (1) A memory location in either the CS or PS whose address is the resultant DAR address

- (2) A buffer bus register whose address is the resultant DAR address.

In each of the above cases, the specified address is called location M.

(c) R: The presence or absence of the letter R in the operation code specifies the use for the register identified in the R subfield. If there is an R in the operation code, the register specified in the R subfield represents the destination of the instruction. If the R is missing from the operation code, the register designated in the R subfield is used for indexing. Any one of the seven letters listed below can appear in the operation code or the R subfield. The indicated code is used in the binary encoding of an instruction involving the corresponding register.

| LETTER       | REGISTER                          | OCTAL<br>CODE |

|--------------|-----------------------------------|---------------|

|              | No Register                       | 0             |

| В            | Buffer Register                   | 1.            |

| $\mathbf{F}$ | First One Register                | 2             |

| J            | Return Address (Jump)<br>Register | 3             |

| K            | Accumulator                       | 4             |

| X            | Index Register X                  | 5             |

| Y            | Index Register Y                  | 6             |

| $\mathbf{Z}$ | Index Register Z                  | 7             |

All of the above registers can be used for indexing and are therefore referred to as index registers. In addition to the above listed registers, L for logic register may appear in the operation code, but never in the R subfield and, hence, is not an index register.

- (d) **A, S, D, or V:** One of these letters appears as the second letter of the operation code of all input-output instructions to indicate the destination and function of the instruction as follows:

- A Peripheral Address Bus

- S Scanner

- D Central Pulse Distributor

- V A register on the buffer bus which functions to control flip-flops or to provide a pulse on one or more leads to perform miscellaneous functions.

- (e) **N:** The letter N appears in the operation code of some maintenance instructions and refers to nonmemory locations. The nonmemory locations are control flip-flops or inspection points in certain units of the equipment such as the CS or PS.

- (f) *G or H:* The letter G or H appears in the operation code of some maintenance instructions to designate a particular physical CS or PS. (These are the only instructions which explicitly refer to the duplication of units in the system.)

# **OPERATIONS**

**5.03** The following letters, when appearing as the first letter of the operation code, specify the action to be performed.

| A—Add                                                  |

|--------------------------------------------------------|

| S—Subtract                                             |

| C—Compare                                              |

| Q-Rotate                                               |

| H—Shift (except in the maintenance instruction $HKU$ ) |

| P—Logical Product (AND)                                |

| U—Logical Union (OR)                                   |

| X—EXCLUSIVE OR                                         |

| T—Transfer                                             |

#### **CONDITIONS**

- 5.04 On conditional transfer instructions, the first letter after T specifies the source of information on which the decision for a transfer is made as follows:

- (a) **K:** The contents of the accumulator register (KR)

- (b) *C:* The current state of the C control flip-flops

- (c) **R:** The state of the C control flip-flops after being set according to the contents of the register identified in the R subfield.

The following letters appear last in the operation code of conditional transfer instructions. They specify the conditions which must exist in K, C, or R (whichever is named in the operation code) for a transfer to occur. S and H in the following list refer to the sign and homogeneity control flip-flops.

|           | S | Н |        |

|-----------|---|---|--------|

| P — Plus  | 0 | 0 | )      |

|           | 0 | 1 | }*     |

|           |   |   | ר<br>ה |

| M — Minus | 1 | 0 | (*     |

|           | 1 | 1 | }*     |

| AZ — Arithmetic Zero                          | $\begin{matrix} 0 \\ 1 \end{matrix}$      | 1<br>1                                    | }*     |

|-----------------------------------------------|-------------------------------------------|-------------------------------------------|--------|

| AU — Arithmetic Unzero                        | 0<br>1                                    | 0                                         | }*     |

| LZ — Logical Zero                             | 0                                         | 1                                         |        |

| LU — Logical Unzero                           | 0<br>1<br>1                               | $\begin{matrix} 0 \\ 0 \\ 1 \end{matrix}$ | }*     |

| LE — Less than or equal to arithmetic zero    | 0<br>1<br>1                               | 1<br>1<br>0                               | }<br>} |

| GE — Greater than or equal to arithmetic zero | $\begin{matrix} 0 \\ 1 \\ 0 \end{matrix}$ | 1<br>1<br>0                               | }*     |

<sup>\*</sup>Any one of the two or three combinations.

#### SPECIAL INDICATORS

- 5.05 The letter U appearing as the last letter of compare instructions CMKU and CWKU means that the homogeneity bit of the C control flip-flops will be set to the logical union (OR) of its former state and of the state corresponding to the difference resulting from the comparison.

- 5.06 The letter E appearing as the first letter of the operation code denotes an exceptional symbolic operation code and means that the remaining letters are not necessarily used as the standard abbreviations described in this section. For example, NAM in the instruction ENAM is a mnemonic code for next address to memory.

#### 6. VARIABLE AND OPTION FIELDS

6.01 Throughout the following definitions of options and descriptions of their use, no implication is intended that a given option is available on all instructions nor that, if available, it must be used.

The particular options available with a given operation code are listed in Part 8.

#### **DA SUBFIELD**

data, an address, or a masking constant. When the ES or PS option is used in the L subfield, the contents of the DA subfield is sent to the L register for masking. Address information in the DA subfield is identified as the resultant DAR address. This is the address referred to when W is specified in an operation code. In an instruction in which the contents of the DA subfield is relevant, a blank DA subfield is interpreted as zero.

#### **R SUBFIELD**

- **6.03** The R subfield, when used, specifies one of the following three functions.

- (a) *Identification:* When the operation code contains an R, the R subfield specifies a register by providing the abbreviation of one of the seven index registers listed in 5.02(c). On any instruction whose operation code contains an R and the R subfield is blank, the instruction is executed as though the contents of the unidentified register are zero.

- (b) **Set Register** (S): When the R subfield consists of the letter S followed by a register abbreviation, the specified register is set to the contents of the DA field. On conditional transfer instructions, the S option occurs only if the transfer occurs.

- (c) Indexing (I): If neither (a) nor (b) applies, a register abbreviation in the R subfield will index the effective DA number. If an S, ES, or PS appears in the L subfield of the instruction, the effective DA number to be indexed is zero; in which case, the contents of the register identified in the R subfield become the resultant DAR number.

- 6.04 In certain instructions, using the R subfield for identification or indexing, either of two additional letters (A or W) can appear in the R subfield accompanying the register abbreviation.

The A or W changes the contents of the register upon execution of the instruction as follows.

- (a) A: This letter, following the register abbreviation in the R subfield, causes the quantity one to be added algebraically to the contents of the register as follows.

- (1) On transfer instructions, the A option (add one) occurs only if the transfer occurs and will be the last step in the execution of the instructions. For example, consider an executed transfer instruction where the R subfield specifies the J register and the A option and the CJ field specify the store return address option J. The quantity one will be added to the new return address after it is placed in the J register.

- (2) On instructions other than transfers, the A option occurs immediately after the contents of the register have been used for either identification or indexing as determined by the instruction.

- (b) **W:** This letter following the register abbreviation in the R subfield causes the result of the indexing operation to be placed in the register. For example, the W option will add the contents of the DA field to the contents of the register, and will place the result in the register, as well as use this result as the resultant DAR number. On conditional transfer instructions, the W option occurs only if the transfer occurs.

# M SUBFIELD

6.05 The M subfield is used only on transfer instructions. The letter M in the subfield specifies an indirect transfer. The resultant DAR address specifies either a CS or PS location that contains the actual transfer address. The DAR address is not the actual transfer address. The actual address is found in bits 19 through 0 of PS or bits 20 through 0 of CS.

# L SUBFIELD

6.06 The L subfield is used to specify masking (EL, ES, PL, PS) or the set-the-logic register option (S). The letter P indicates logical product masking (the AND function). The letter E indicates insertion masking that is used only on instructions sending information to either the CS, the data buffer bus register from any other CC register, or from the instruction word itself. The following operations are specified in the L subfield.

- (a) **PL** or **EL**: These options use the contents of the L register set by a previous instruction for product or insertion masking.

- (b) **PS or ES:** These options cause the contents of the DA subfield to be placed in the L register before the masking is done.

- (c) S: The letter S appearing in the L subfield causes the contents of the DA subfield to be placed in the L register, but no masking is done.

- 6.07 Assume that an instruction specifies that its resultant DAR number be sent to the BR. On an instruction with the BR as the destination, an E in the L subfield specifies insertion masking control by the contents of the LR. The new information from the DA field or CC register, therefore, replaces the contents of the BR bits corresponding to bits of the LR that contain ones. The BR bits corresponding to LR bits that contain zeros are not changed. The words in the following examples contain 8 bits instead of 23 bits for simplicity:

| Contents of CC Register                          | 0011 | 0011 |

|--------------------------------------------------|------|------|

| Contents of LR                                   | 1111 | 0000 |

| Original Contents of BR                          | 0101 | 0101 |

| Final contents of BR after insertion masking has |      |      |

| occurred                                         | 011  | 0101 |

When E is used in an instruction sending information to the BR as the ultimate destination, the information being sent sets the C control flip-flops. These flip-flops are set before insertion masking and after complementing if called for in the CJ subfield.

destination in the CS and that specifies insertion masking involves the same operations as when the BR is the destination. In addition, the new contents of the BR replace the contents of the CS location specified in the instruction. Therefore, the operation is not a direct insertion into memory. The insertion changes the contents of the BR and the new contents are sent to the CS.

#### CJ SUBFIELD

- **6.09** This subfield, when used, specifies either of the following options.

- (a) Complement Option C: The letter C in the CJ subfield will cause the information going to the masked bus (MB) to be complemented in route to its destination. If a P appears in the L subfield, the logical product (AND) operation occurs before the complementing. If an E appears in the L subfield, the complementing occurs first followed by the insertion of the selected bits into the BR.

- (b) Store Return Address Option J: On all transfer instructions except ENTJ, the J option is specified by the letter J in the CJ subfield. This causes the address following the transfer instruction to be placed in the return address register J in the event a transfer does occur. The return address in this case is the address of the ENTJ instruction plus two.

#### 7. ENCODING OF CC INSTRUCTIONS

- 7.01 As discussed in 2.03, these are two columns in the PR dedicated to the octal encoding of instructions. The five-octal digit column (Fig. 2 and Table C) contains the octal encoding for the basic instruction and some of the options associated with that instruction. Some options are represented by bits 21 and 22 in column two of Fig. 2.

- 7.02 The octal encoding of each instruction is given in Part 8. The basic encoding is in parentheses right after the symbolic intruction code. The options for the instruction are also listed with the octal code (in parentheses) representing the option.

- 7.03 In order to better understand the encoding and deviation of complete instructions, a sample encoding is given. The sample instruction (Fig. 1) is CWR with options K (index register) and PS. The sum of the octal numbers, 14435, represents the octal encoding for the instruction and options. This is the manner in which the 5-digit number of Fig. 1 is derived. The same procedure is used for any instruction with any options. To arrive at the number in the PR, add the octal equivalent of the options to the basic

TABLE C

SAMPLE INSTRUCTION ENCODING

| 5     | 4        | 3        | 2        | 1                                                 | DIGITS IN COL 1 IN PR (FIG. 2) |

|-------|----------|----------|----------|---------------------------------------------------|--------------------------------|

| 36 35 | 34 33 32 | 31 30 29 | 28 27 26 | 25 24 23                                          | BITS OF PS WORD                |

| 0 1   | 0 0 0    | 1 0 0    | 0 1 1    | 1 0 0 0 BINARY REPRESENTA<br>OF BASIC INSTRUCTION |                                |

| 1     | 0        | 4        | 3        | 0                                                 | BASIC ENCODING FOR CWR         |

| 0     | 1 0 0    | 0        | 0        | 0                                                 | ENCODING FOR K REGISTER OPTION |

|       |          |          |          | 1 0 1                                             | ENCODING FOR PS                |

| 0     | 0        | 0        | 0        | 5                                                 | OPTION                         |

| 1     | 4        | 4        | 3        | 5 SUM                                             |                                |

octal representation of the instruction. There are instances where options require bits 22 and 21 of column 2 (Fig. 2). In these cases, a 6-digit number is added to the basic code with the sixth being digit 8 of column 2 (Fig. 2). All numbers given in Part 8 are octal.

7.04 For the combined shift or rotate instructions, an additional encoding bit is needed (2.04). Bit 19 is used in addition to bits 22 and 21. Bit 19 is not shown in Part 8. Only bits 22 and 21 are given for the shift and rotate instructions.

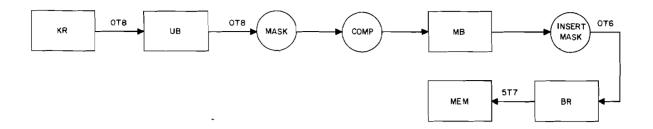

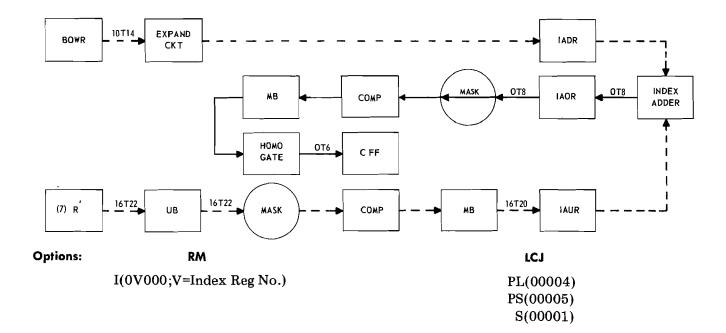

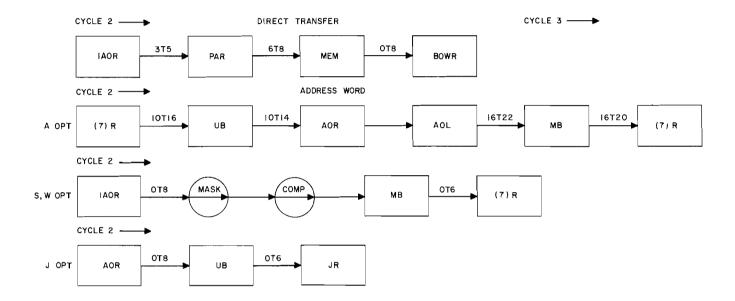

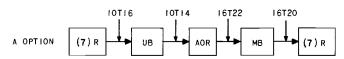

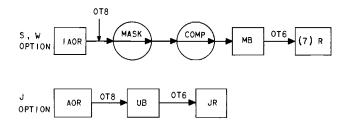

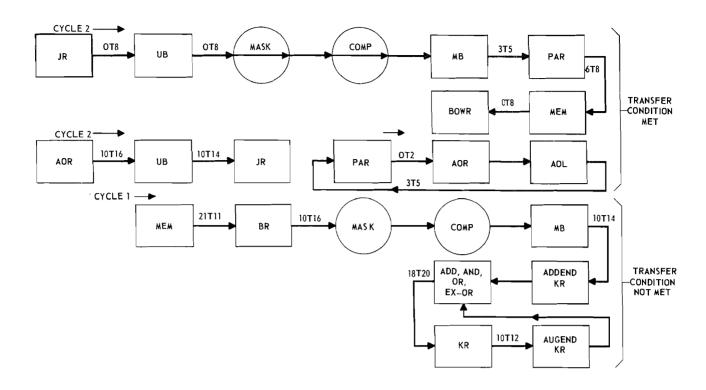

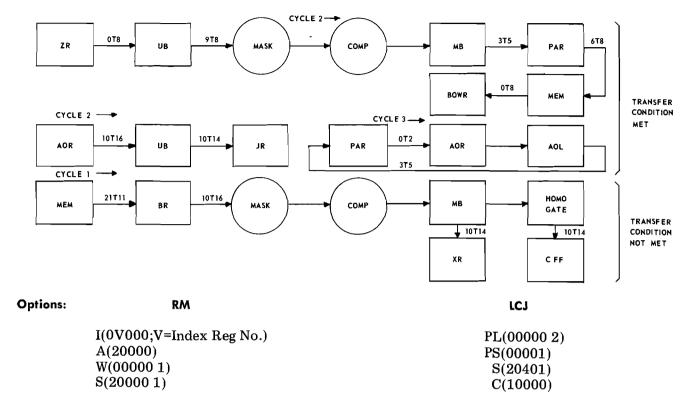

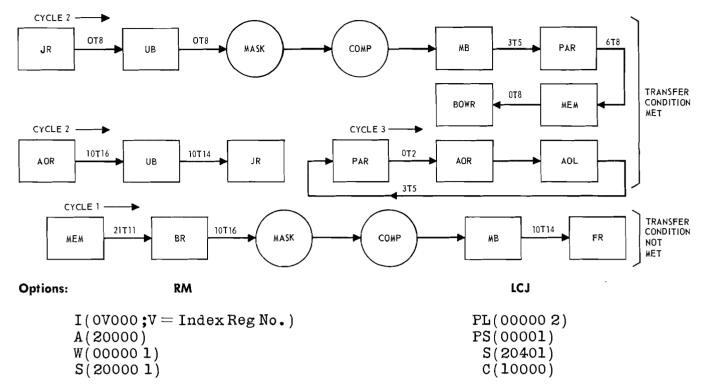

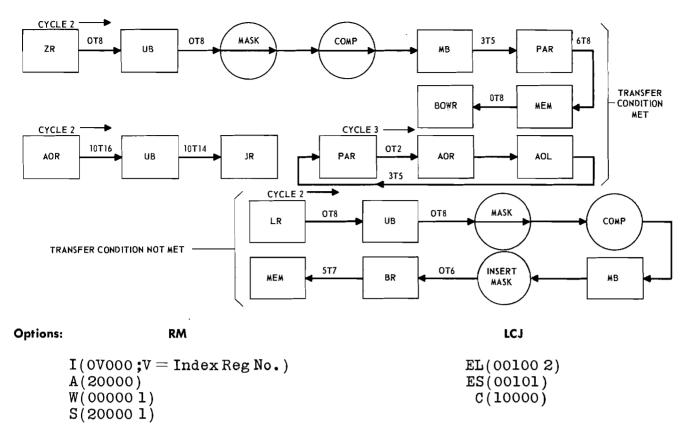

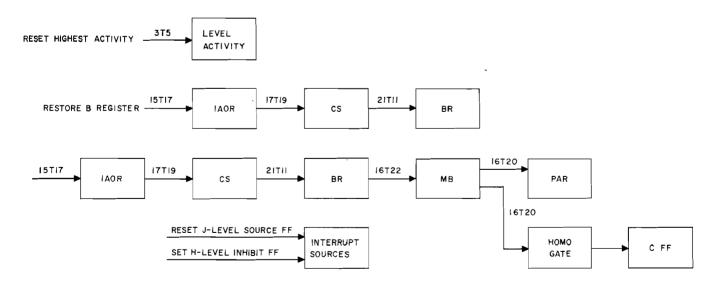

#### 8. FLOW DIAGRAMS

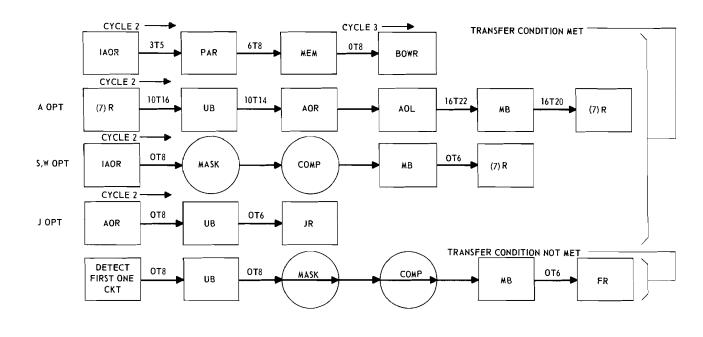

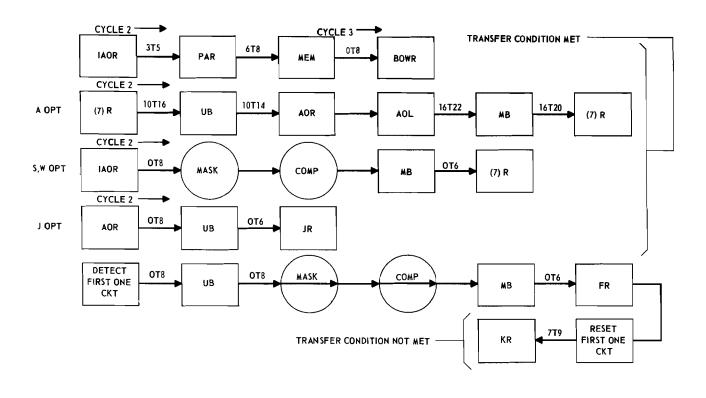

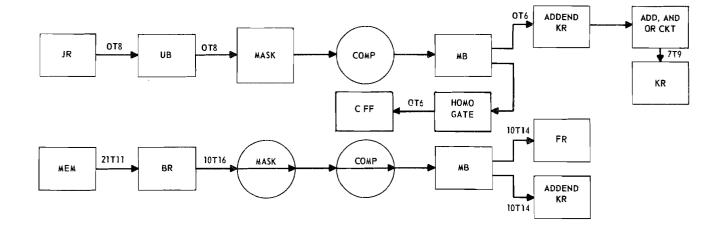

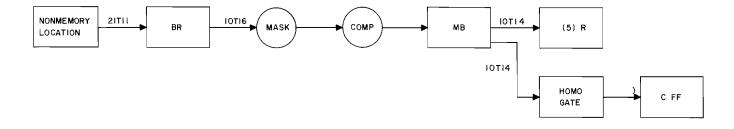

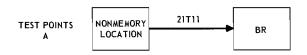

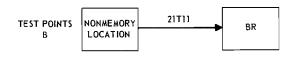

- **8.01** Definitions of symbols and abbreviations used in the flow diagrams are shown in Fig. 3.

- **8.02** As described in Part 7, the flow diagrams include the octal encoding for the instructions and options. The codes are given in parentheses.

Fig. 3—Symbols and Abbreviations Used in Flow Diagrams

# **BASIC OPERATIONS**

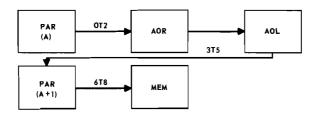

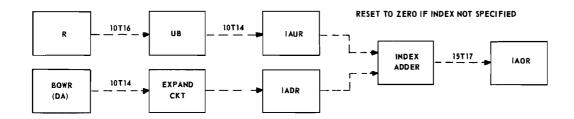

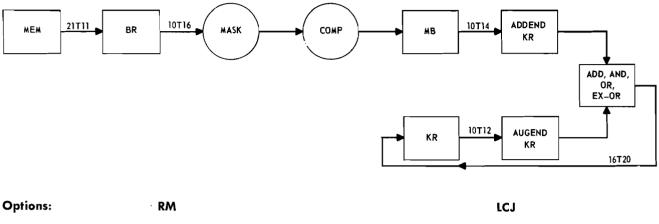

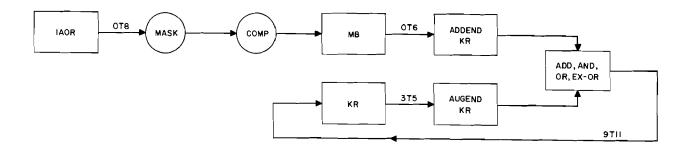

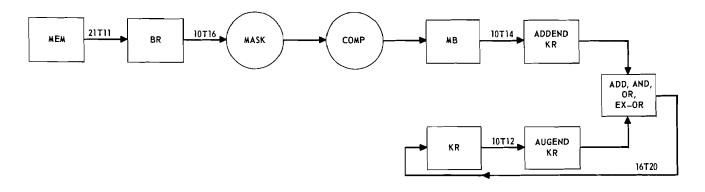

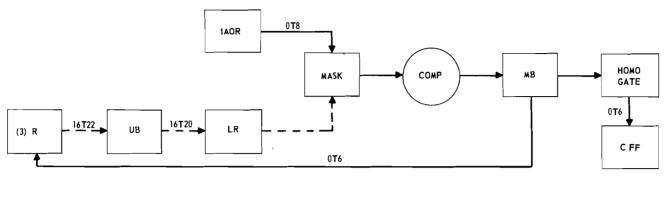

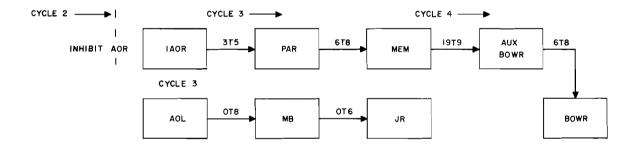

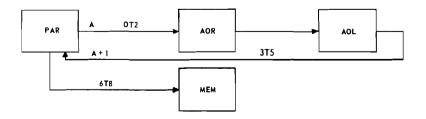

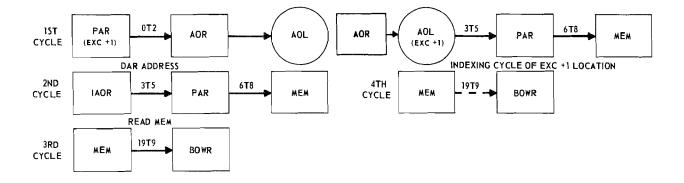

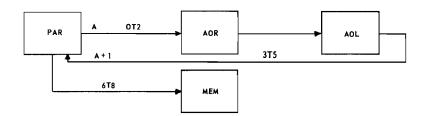

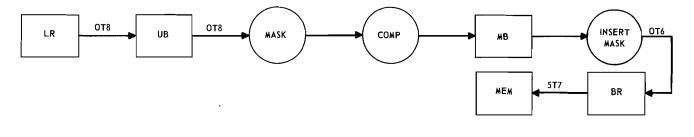

8.03 Timing for the normal incrementing of the PAR (program address register).

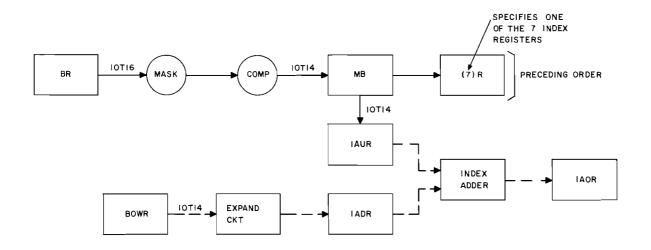

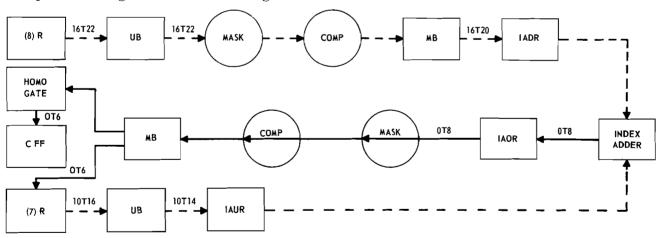

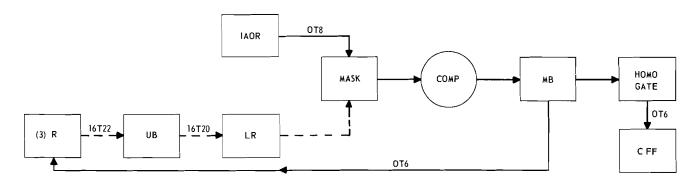

**8.04** Timing for the indexing cycle.

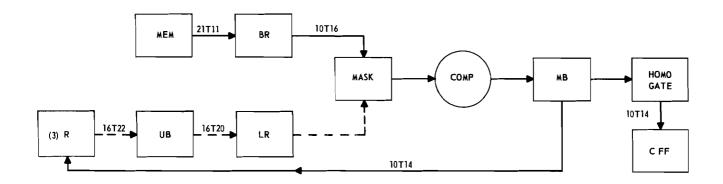

**8.05** Timing for the mixed indexing cycle.

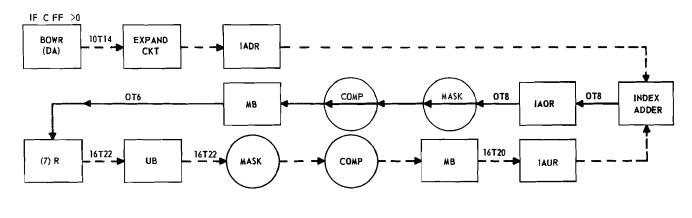

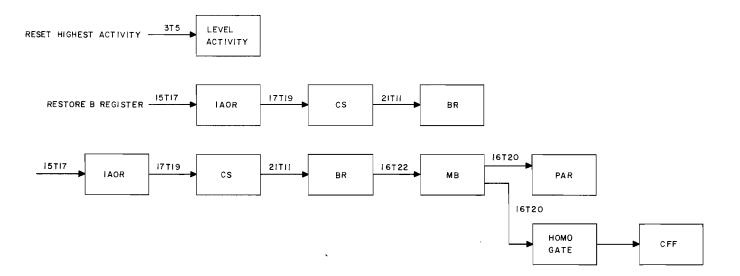

**8.06** Timing for the R subfield options.

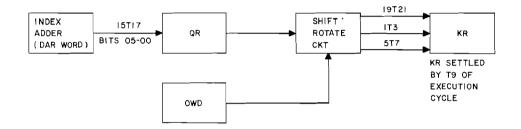

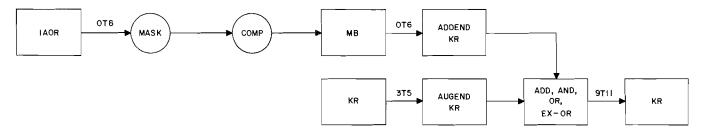

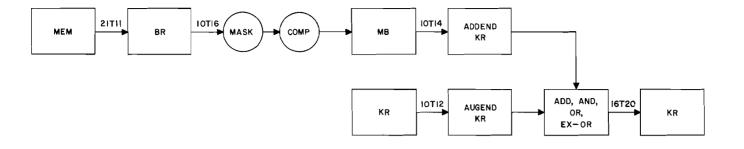

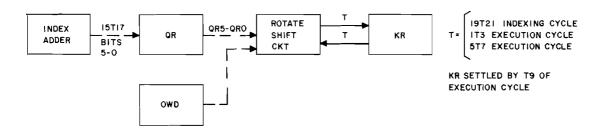

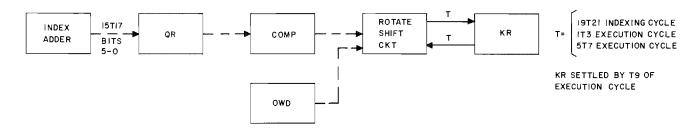

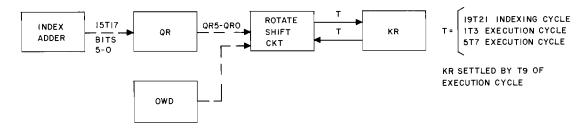

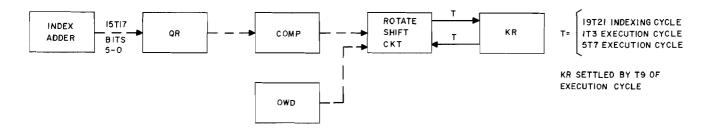

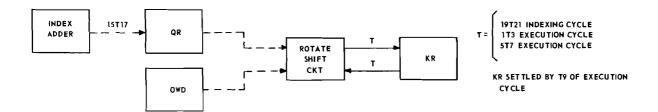

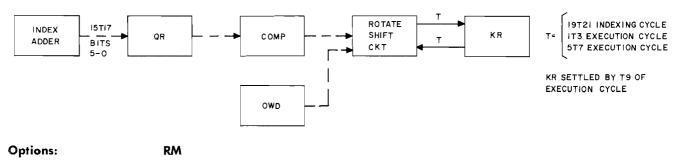

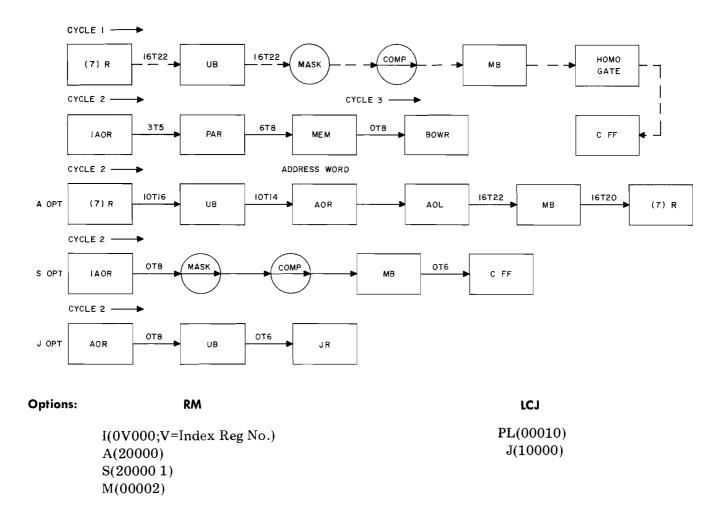

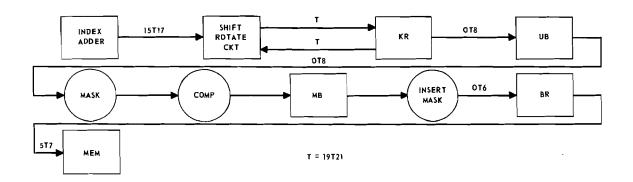

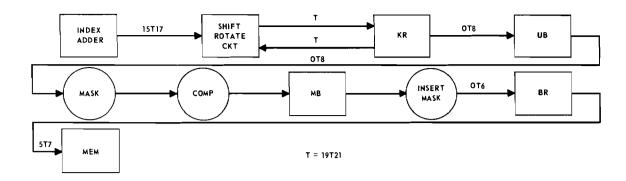

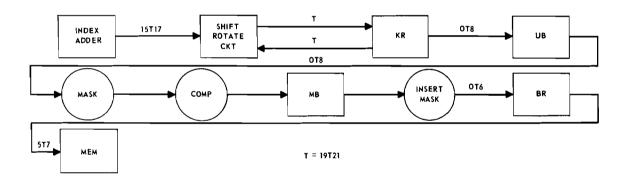

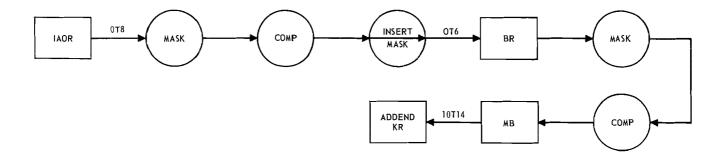

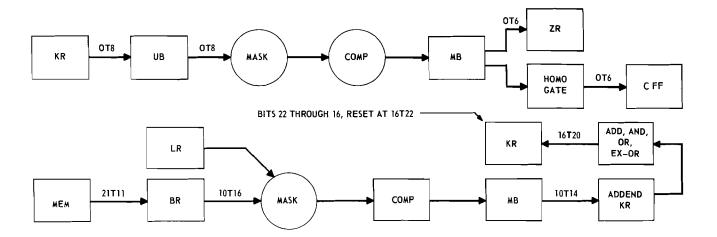

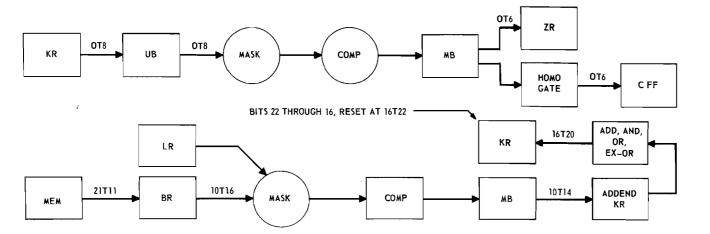

**8.07** Timing for the H and Q operations.

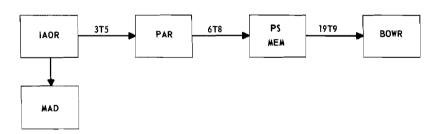

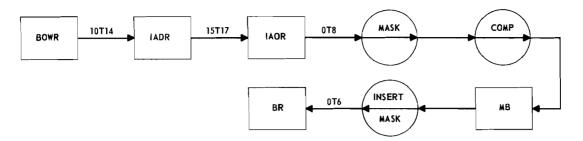

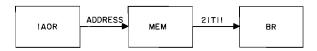

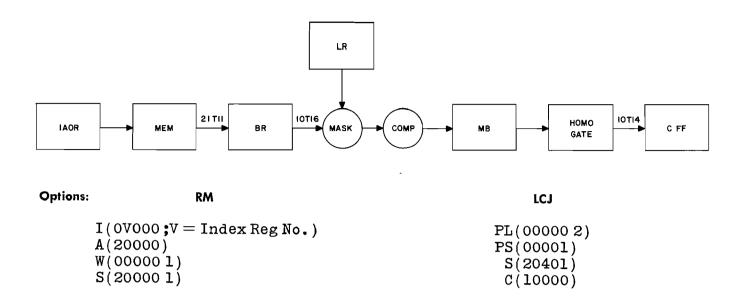

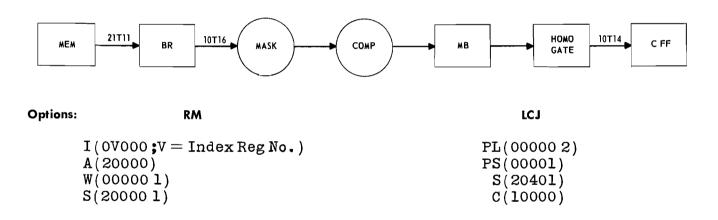

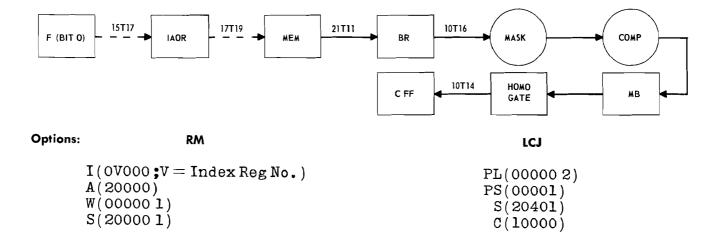

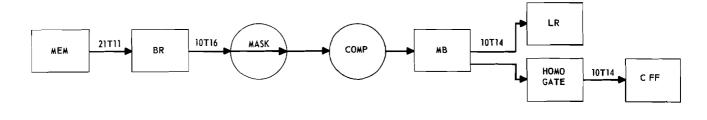

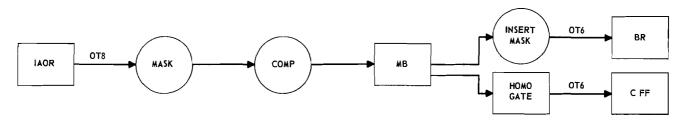

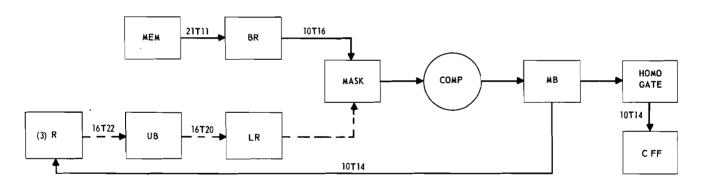

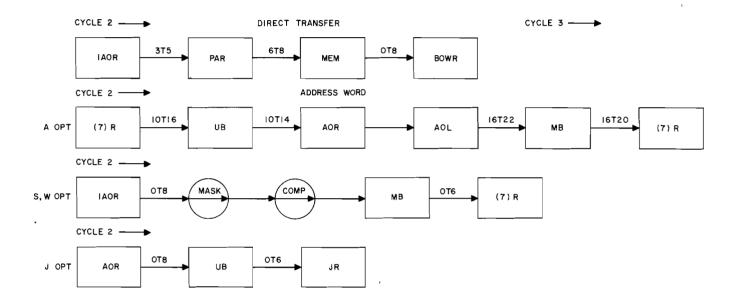

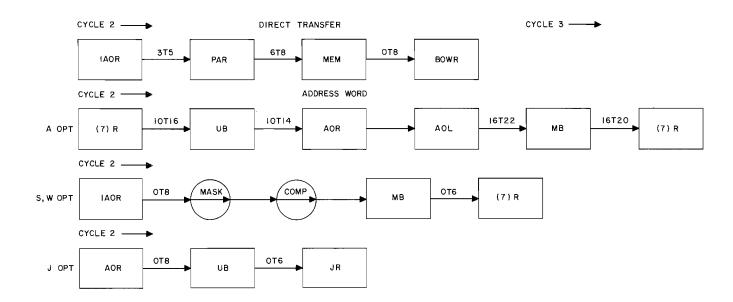

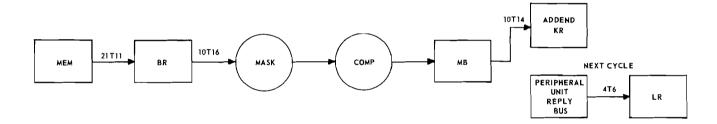

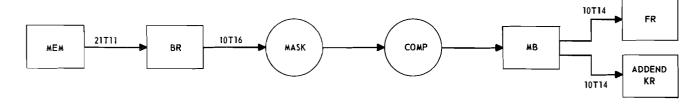

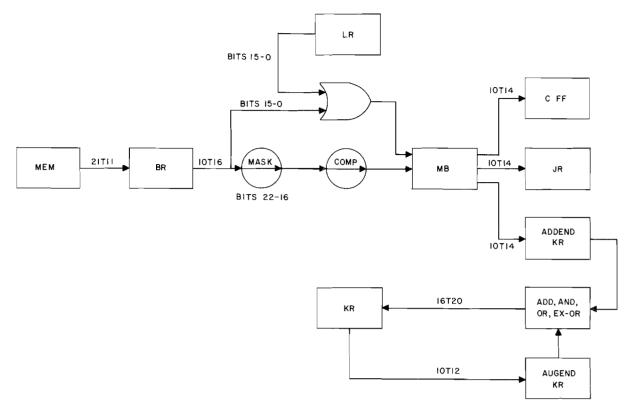

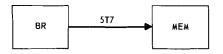

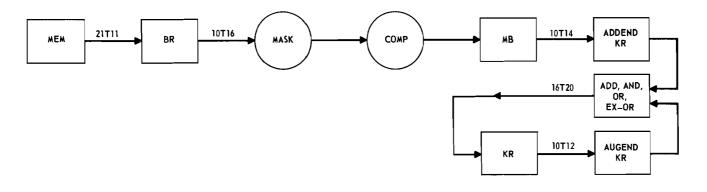

**8.08** A read data from memory operation using a PS address is shown below. The read-write sequencer is activated when the memory address decoder (MAD) recognizes that the address in the index adder output register (IAOR) is a PS address.

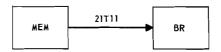

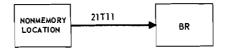

8.09 The data obtained from the PS is gated to the BR. Once the data is in the BR, the processing is completed under control of the order word register (OWR). The instruction was retained in the OWR while data was being gated into the BR.

#### **SECTION 231-001-102**

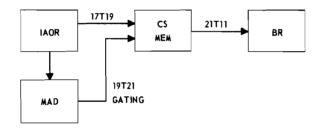

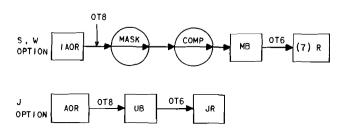

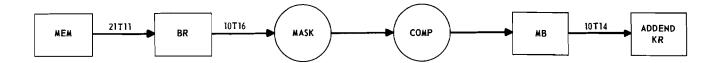

- **8.10** Read-memory instructions that specify CS addresses require use of a sequencer when the effective execution time is more than one 5.5-microsecond machine cycle. The CS reading operations are as follows:

- (a) Reading from a CC CS (one cycle)

- (b) Reading from a single processor CS immediately after writing into a signal processor CS (four cycles)

- (c) Reading from a signal processor CS immediately after any operation other than writing into a signal processor CS (two cycles).

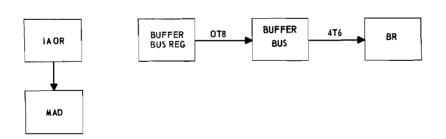

**8.11** A read-memory instruction using a buffer bus register address reads data from any buffer bus register.

#### **GENERAL PURPOSE OPERATIONS**

# A. Move Operations

- **8.12** The effective execution time (in 5.5-microsecond machine cycles) of move operations where information in a CC register is written into a CS is as follows:

- (a) Writing into a CC CS (one cycle)

- (b) Writing into a signal processor CS immediately after writing into the same location or into another signal processor CS location (two cycles)

- (c) Writing into a signal processor CS immediately after any operation other than writing into a signal processor CS (one cycle).

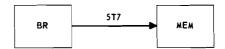

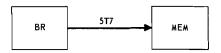

- **8.13 BM**(00102)—**Buffer Register to Memory:** The contents of the data buffer register (B) replace the contents of location M.

**Options:**

RM

LCJ

**Restrictions:** The data buffer register B must not appear in the R subfield except as generated by the MCBAM macro. If B is specified in the R subfield, the contents of B replace the contents of the memory location whose address was generated on the preceding instruction.

**8.14** KS(00112)—The contents of the accumulator K, after possible product masking and/or complementing, replace or are insertion masked into the BR. The contents of the BR replace the contents of location M.

**Restrictions:** K must not appear in the R subfield except as generated by the MKKAM macro. If K is specified in the R subfield, the contents of K, after possible product masking, insertion masking, or complementing, replace the contents of the memory location whose address was generated on the preceding instruction.

8.15 LM(00100)—Logic Register to Memory: If neither ES nor PS masking is specified in the instruction, the contents of the LR, after possible complementing, replace or are insertion masked (EL) into the contents of the BR. The new contents of the BR replace the contents of location M. If either ES or PS masking is called for in the instruction, the contents of the DA field replace the contents of the LR. The new contents of the LR, after possible complementing, replace or are insertion masked into the contents of the BR. The new contents of BR replace the contents of location M.

**8.16** FM(00110), JM(00120), XM(00122), YM(00130), and ZM(00132): The contents of register F, J, X, Y, or Z (whichever is specified in the operation code), after possible product masking and/or complementing, replace or are insertion masked into the BR. The contents of the BR replace the contents of location M.

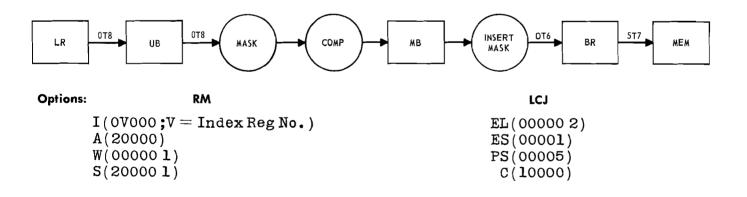

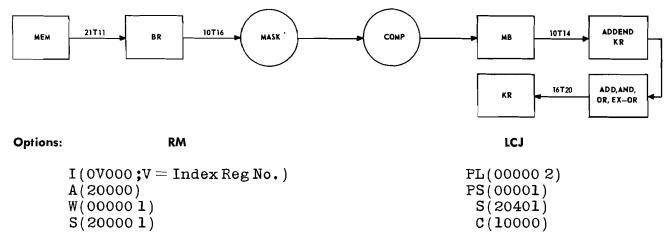

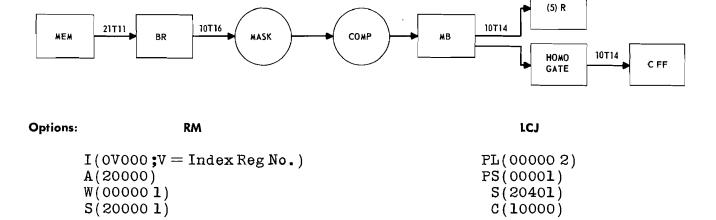

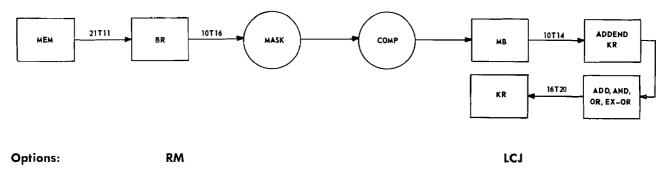

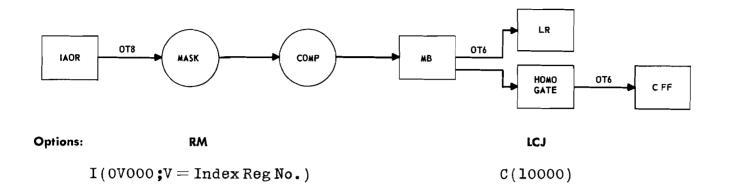

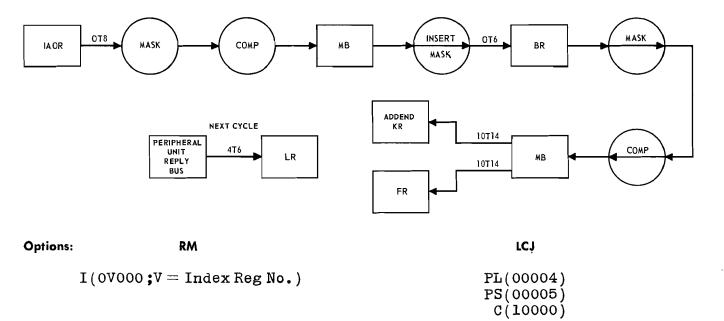

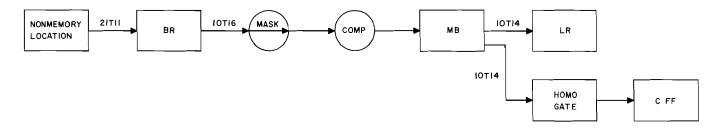

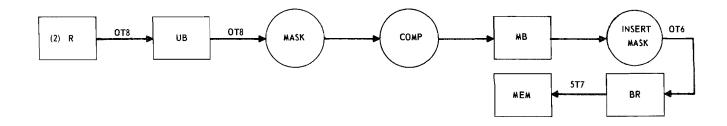

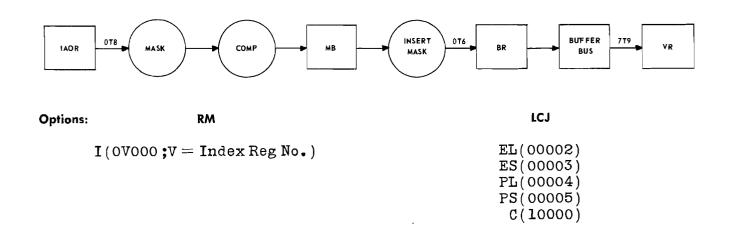

**8.17** *MB(00202)—Memory to Data Buffer Register:* The contents of location M replace the contents of the BR. The C control flip-flops are not affected by this operation.

**8.18** *MC(00210)—Memory to C Control Flip-Flops:* The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, set the C control flip-flops.

8.19 MCII(00212)—Memory to C Control Flip-Flops and Inhibit Interrupts: The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, set the C control flip-flops. During the following cycle, interrupts of levels H through K are inhibited and, if location M is in the SP call store, the SP is stopped during the following cycle.

**Restrictions:** If MCII was the last instruction excecuted prior to an A through G interrupt, it must be repeated following the interrupt. The data buffer bus register B must not be used as an index register because it is destroyed on the first execution of MCII.

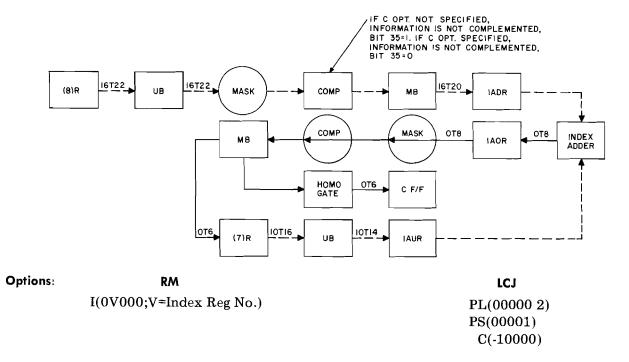

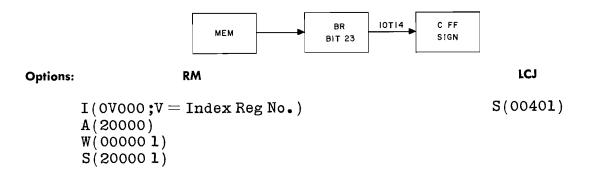

8.20 MCLF(00214)—Memory to C Control Flip-Flops: Address Modified by Low Bit of First One Register (FR): The least significant bit of the FR replaces the next to least significant bit of the resultant DAR address in computing the address of location M. The contents of this location replace the contents of the BR and, after possible product masking and/or complementing, set the C control flip-flops. If an index register other than the FR is specified with register modification S or W, the index register will be set to the resultant DAR address with bit position 1 modified by the least significant bit of the FR.

Restrictions: If register F appears in the R subfield, register modification S, A, or W is not available.

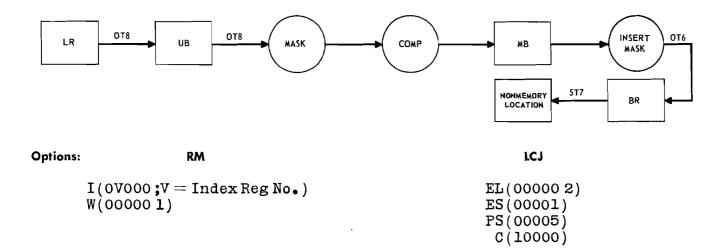

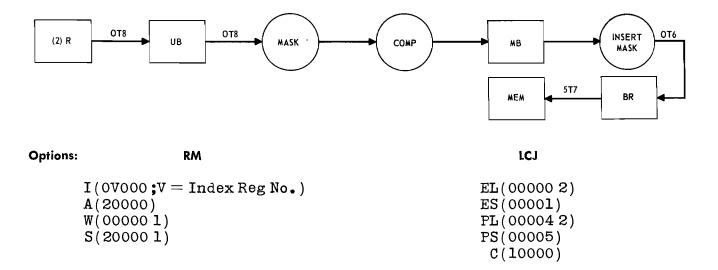

**8.21** *ML(00320)—Memory to Logic Register:* The contents of location M replace the contents of the BR and, after possible complementing, set the C control flip-flops and replace the contents of the LR.

Options: RM LCJ

I(0V000;V = Index Reg No.)

A(20000)

W(000001)

S(200001)

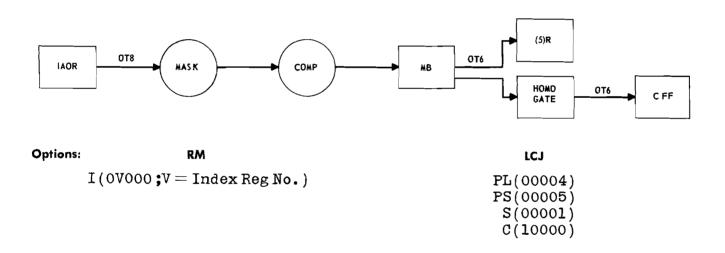

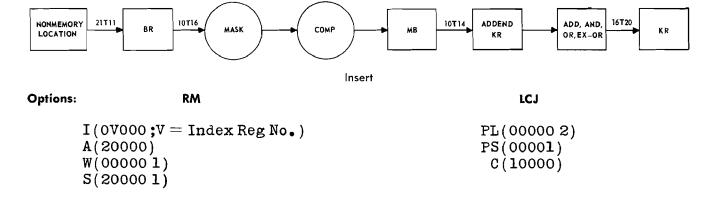

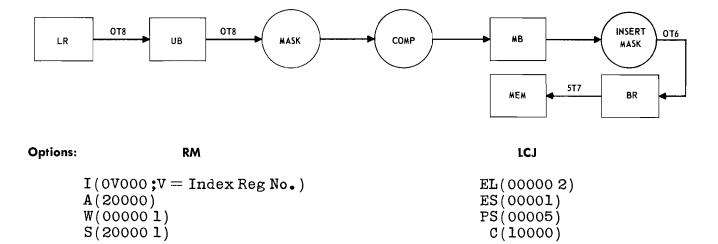

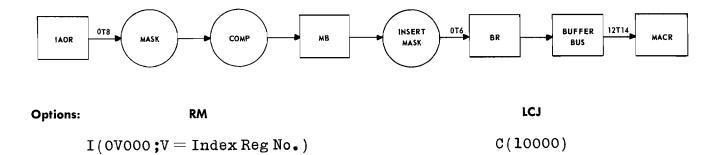

**8.22** *MK(00350)—Memory to Accumulator:* The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, replace the contents of the KR. The C control flip-flops are not set by this operation.

Restrictions: The following instruction must not be

- (1) AKR or SKR

- (2) One of the following instructions with K in the R subfield: AWRP, CWR, and all TR instructions.

- **8.23** MF(00222), MJ(00322), MX(00310), MY(00300), and MZ(00330)—Memory to Register: The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, set the C control flip-flops and replace the contents of the FR, JR, XR, YR, or ZR, whichever is specified in the operation code.

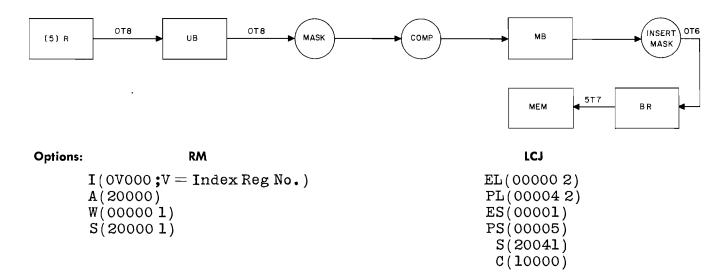

8.24 MKII(00376)—Memory to Accumulator; Inhibit Interrupts: The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, replace the contents of the KR. The sign bit of the C control flip-flops is set to 1 if the sign bit of the new contents of the KR is a 1 or either of the signal processor flag flip-flops contains a 1. If the sign bit of the new contents of the KR and both of the signal processor flag flip-flops are 0, the sign bit of the C control flip-flops will be 0. During the following cycle, interrupts of levels H through K are inhibited. If location M is in the SP call store, the SP is stopped during the following cycle. Neither the B register nor K register can be used as an index register because their contents are destroyed on the first execution of MKII.

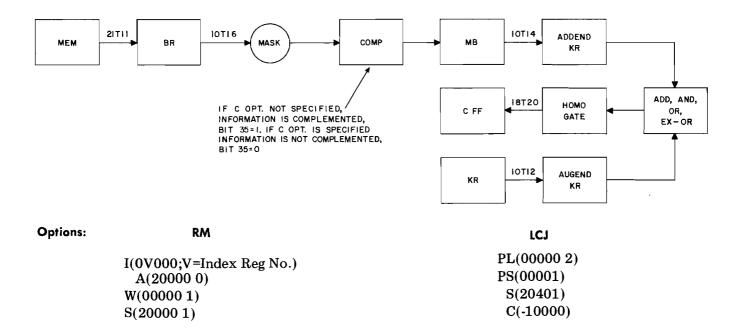

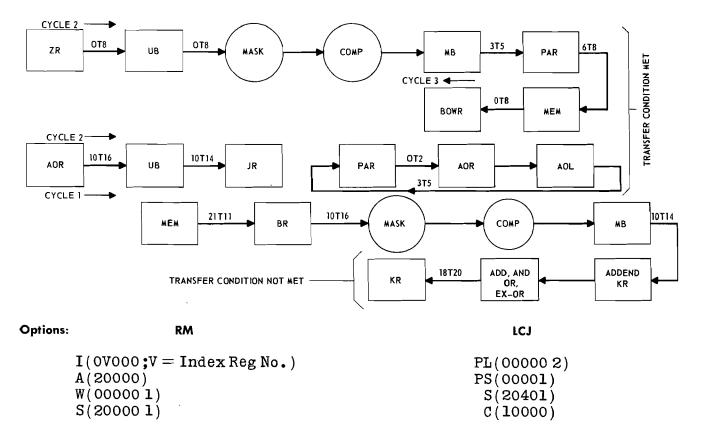

| I(00000; V = Index Reg No.) | PL(000002) |

|-----------------------------|------------|

| A(20000)                    | PS(00001)  |

| W(000001)                   | S(20401)   |

| S(20000 1)                  | c(10000)   |

**Restrictions:** The following instruction must not be

- (1) AKR or SKR.

- (2) One of the following instructions with K in the R subfield: AWRP, CWR, TR instructions.

- (3) If MKII was the last instruction executed prior to an A through G interrupt, it must be repeated following the interrupt. The data buffer bus register B must not be used as an index register because it is destroyed on the first execution of MKII.

- **8.25 WB**(00600)—Word to BR: The resultant DAR number W, after possible product masking and/or complementing, sets the C control flip-flops, replaces the contents of the BR, or is insertion masked into the contents of the BR.

**8.26 WL**(00720)—Word to LR: The resultant DAR number W, after possible complementing, sets the C control flip-flops and replaces the contents of the LR.

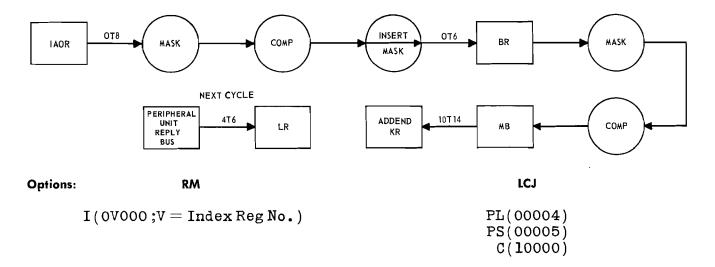

**8.27** WF(00622), WJ(00722), WX(00710), WY(00700), and WZ(00730)—Word to Register: The resultant DAR number W, after possible product masking and/or complementing, sets the C control flip-flops and replaces the contents of FR, JR, XR, YR, or ZR, whichever is specified in the operation code.

**8.28** WK(00750)—Word to Accumulator: The resultant DAR number W, after possible product masking and/or complementing, replaces the contents of the KR. The C control flip-flops are not set.

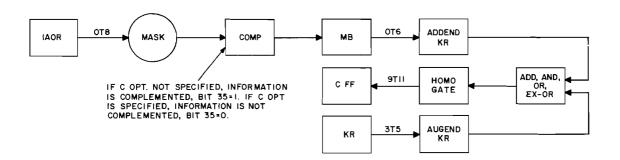

Options: RM LCJ  $I (0 \lor 000 \ ; \lor = Index Reg No.) \\ PL (00004) \\ PS (00005) \\ S (00001) \\ C (10000)$

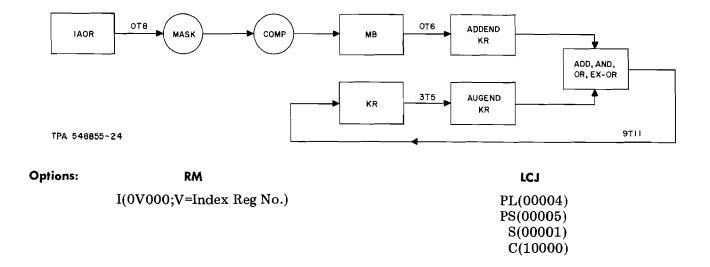

# **B.** Add Operations

**8.29** AWK(00752)—Add Word to Accumulator: The resultant DAR number W, after possible product masking and/or complementing, is added algebraically to the contents of the KR and the sum remains in the KR.

Options:

RM

LCJ

( I(0V000;V≃Index Reg No.)

PL(00004)

PS(00005)

S(00001)

C(10000)

C(10000)

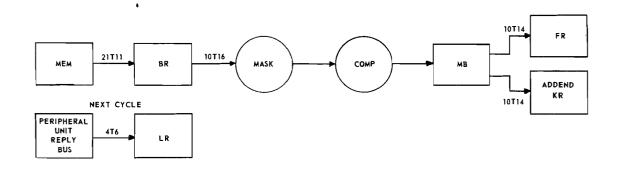

**8.30** AMK(00352)—Add Memory to Accumulator: The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, are added algebraically to the contents of the KR; the sum remains in the KR. The C control flip-flops are not set.

**Options:** RM I(0V000;V=Index Reg No.)

A(20000) W(000001)

LCJ

PL(00000 2)

PS(00001)

S(20401)

C(10000)

S(20000 1)

Restrictions: The following instruction must not

- (1) Specify K in the R subfield

- (2) Be AKR or SKR.

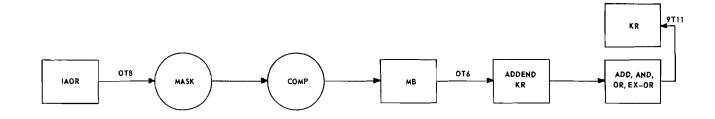

ABR(00522), AFR(00524), AJR(00526), AKR(00530), ALR(00520), AXR(00532), AYR(00534), and AZR(00536)—Add Contents of Registers Specified by Operation Field and R Subfield: The contents of the BR, FR, JR, KR, LR, XR, YR, or ZR, whichever is specified in the operation code, after possible product masking and/or complementing, are added algebraically to the contents of the register identified in the R subfield (BR, FR, JR, KR, XR, YR, or ZR). The sum sets the C control flip-flops and replaces the original contents of the register identified in the R subfield.

**Options:**

RM

I(0V000;V=Index Reg No.)

LCJ

PL(00000 2)

PS(00001)

C(10000)

8.32 AWRP(00432)—Add Word to Register if C Control Flip-Flops Are Positive: If the sign bit of the C control flip-flops is positive, the contents of the register identified in the R subfield (BR, FR, JR, KR, XR, YR, or ZR), after possible product masking and/or complementing, are added algebraically to the effective DA number. This sum replaces the contents of the identified register. The C control flip-flops are not affected. If the sign bit of the C control flip-flop is negative, no action takes place.

Options: RM LCJ  $I(0V000;V=Index\ Reg\ No.) \\ PL(00004) \\ C(10000)$

#### C. Subtract Operations

**8.33** SWK(10752)—Subtract Word from Accumulator: The resultant DAR number W, after possible product masking and/or complementing, is subtracted from the contents of the KR and the difference remains in the KR. The C control flip-flops are not set.

Options: RM LCJ

I(0V000;V=Index Reg No.) PL(00004)

PS(00005)

S(00001)

C(-10000)

**8.34** SMK(10352)—Subtract Memory from Accumulator: The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, are subtracted from the contents of the KR and the difference remains in the KR. The C control flip-flops are not set.

Restrictions: The following instruction must not

- (1) Specify K in the R subfield

- (2) Be AKR or SKR.

- 8.35 SBR(10522), SFR(10524), SJR(10526), SKR(10530), SLR(10520), SXR(10532), SYR(10534), and SZR(10536)—Subtract Contents of Register Specified by Operation Field from Register Specified by R Subfield: the contents of the BR, FR, JR, KR, LR, XR, YR, or ZR, whichever is specified in the operation code, after possible product masking and/or complementing, are subtracted from the contents of the register identified in the R subfield (BR, FR, JR, KR, XR, YR, or ZR). The difference sets the C control flip-flops and replaces the contents of the register specified in the R subfield.

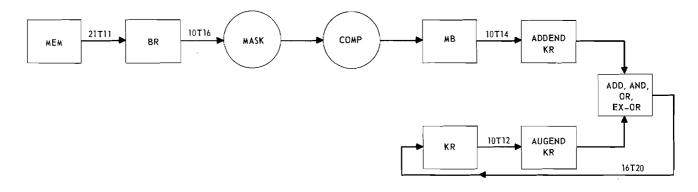

# D. Compare Operations

**8.36** CWK(10742)—Compare Word with Accumulator: The resultant DAR number W, after possible product masking and/or complementing, is subtracted from the contents of the KR. The contents of KR remain unchanged, but the C control flip-flops are set according to the difference.

Options: RM LCJ

I(0V000;V=Index Reg No.)

PL(00004)

PS(00005)

S(00001)

C(-10000)

**8.37** CMK(10342)—Compare Memory with Accumulator: The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, are subtracted from the contents of the KR. The contents of the KR remain unchanged, but the C control flip-flops are set according to the difference.

**Restrictions:** The following instruction must not be one of the early transfer instructions: TAULM, TAUMK, TUPMK, TCGMX, or TCMMF.

**8.38** CWKU(10740)—Compare Word with Accumulator; OR Homogeneity: This instruction is the same as the CMK instruction except that the C control homogeneity flip-flop is set to the logical union (OR) of its former state and the state corresponding to the difference. The homogeneity bit will be a 1 after the instruction of it were a 1 before the instruction or if the difference resulting from the interval subtraction is homogeneous (all ones or all zeros).

**8.39** *CMKU(10340)—Compare Memory with Accumulator; OR Homogeneity:* This instruction is the same as the CMK instruction except that the C control homogeneity flip-flop is set to the logical union (OR) of its former state and the state corresponding to the difference. The homogeneity bit will be a 1 after the instruction if it were a 1 before the instruction or if the difference resulting from the internal subtraction is homogeneous (all ones or all zeroes).

**Restrictions:** The following instruction must not be one of the early transfer instructions; TAULM, TAUMK, TUPMK, TCGMX, or TCMMF.

**8.40** CWR(10430)—Compare Word with Register: The contents of the register identified in the R subfield (B, F, J, K, X, Y, or Z) may be product-masked and, from this, the effective DA number is subtracted. The original contents of the identified register remain unchanged, but the C control flip-flops are set according to the difference.

**Note:** CWR differs from the other compare instructions (CWK, CMK, CWKU, CMKU) in the following ways.

- (1) It is R rather than W that is subject to masking.

- (2) When W equals R, the C control flip-flops are set to logical (plus) zero.

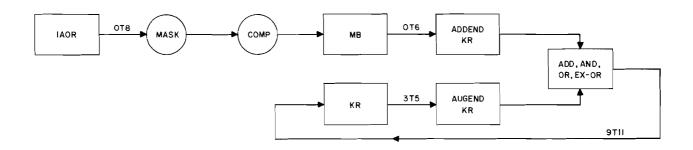

# E. Logical Operations

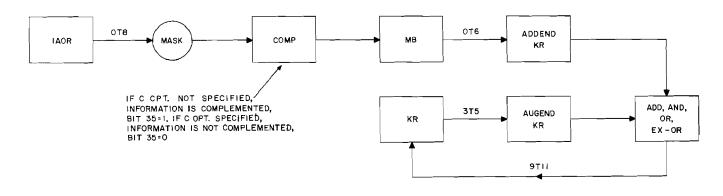

8.41 PWK(00642)—Logical Product (AND) of Word with Accumulator: The resultant DAR number W, after possible product masking and/or complementing, is combined by the logical product (AND) function with the contents of the KR; the result replaces the original contents of the KR.

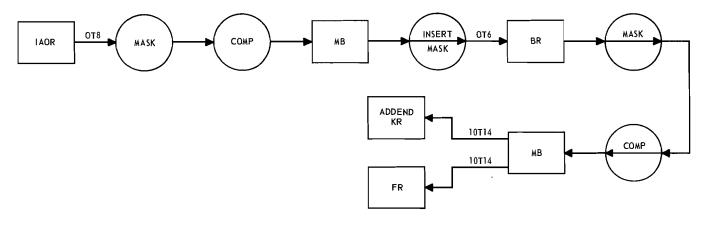

8.42 PMK(00242)—Logical Product (AND) of Memory with Accumulator: The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, are combined by the logical product (AND) function with the contents of the KR; the result replaces the original contents of the KR.

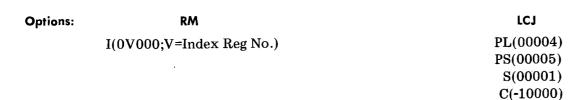

**Options:**

RM

LCJ

| I(0 V 0 0 0; V = Index Reg No.) | PL(000002) |

|---------------------------------|------------|

| A(20000)                        | PS(00001)  |

| W(000001)                       | S(20401)   |

| S(20000 1)                      | C(10000)   |

**Restrictions:** The following instruction must not

- (1) Specify K in the R subfield

- (2) Be AKR or SKR.

- **8.43** UWK(00670)—Logical Union (OR) of Word with Accumulator: The resultant DAR number W, after possible product masking and/or complementing, is combined by the logical union (OR) function with the contents of the KR, and the result replaces the original contents of the KR.

**Options:**

RM

LCJ

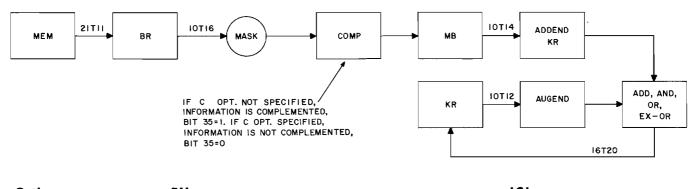

8.44 *UMK(00270)—Logical Union (OR) of Memory with Accumulator:* The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, are combined by the logical union (OR) function with the contents of the KR; the result replaces the original contents of the KR.

$\begin{array}{ll} I \ (0 \ V = Index \ Reg \ No_{\bullet}) & PL \ (00000 \ 2) \\ A \ (20000) & PS \ (00001) \\ W \ (00000 \ 1) & S \ (20401) \\ S \ (20000 \ 1) & C \ (10000) \end{array}$

Restrictions: The following instruction must not

- (1) Specify K in the R subfield

- (2) Be AKR or SKR.

- **8.45 XWK**(00650)—EXCLUSIVE OR of Word with Accumulator: The resultant DAR number W, after possible product masking and/or complementing, is combined by the EXCLUSIVE OR function with the contents of the KR; the result replaces the original contents of the KR.

**Options:**

RM

LCJ

I(0V000;

$$V = Index Reg No.)$$

PL(00004) PS(00005) S(00001) C(10000)

**8.46** XMK(00250)—EXCLUSIVE OR of Memory with Accumulator: The contents of location M replace the contents of the BR and, after possible product masking and/or complementing, are combined by the EXCLUSIVE OR function with the contents of the KR; the result replaces the original contents of the KR.

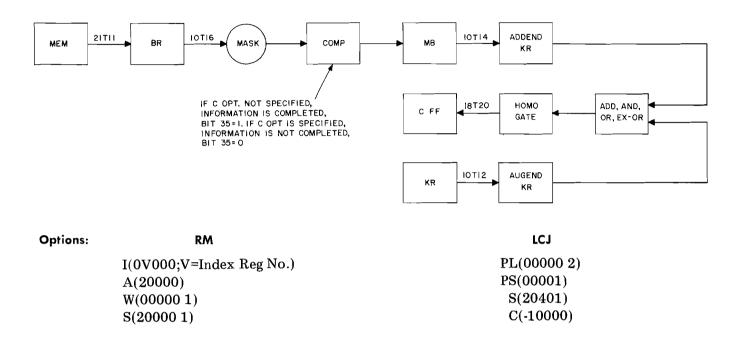

**Options:**

RM

LCJ

$$\begin{array}{ll} \text{I(0V000;V = Index Reg No.)} & \text{PL(00000 2)} \\ \text{A(20000)} & \text{PS(00001)} \\ \text{W(00000 1)} & \text{S(20401)} \\ \text{S(20000 1)} & \text{C(10000)} \end{array}$$

Restrictions: The following instruction must not

- (1) Specify K in the R subfield

- (2) Be AKR or SKR.

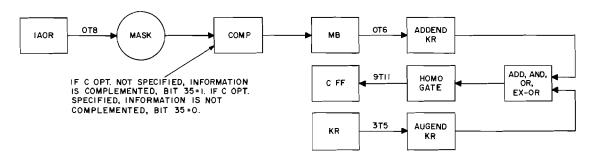

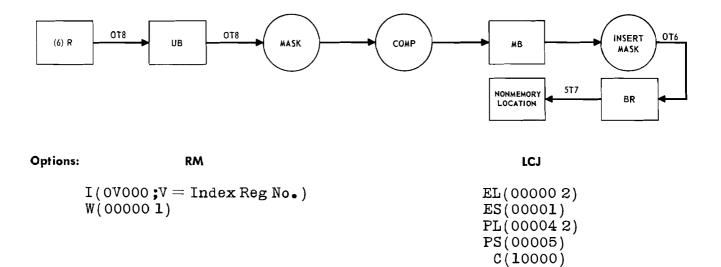

- 8.47 PWX(00716), PWY(00706), and PWZ(00736)—Logical Product (AND) of Word with Register:

The original contents of the XR, YR, or ZR, whichever is specified in the operation code, replace

the contents of the LR. The resultant DAR number W is combined by the logical product (AND) function with the original contents of the specified register now in the LR. The result, after possible complementing, sets the C control flip-flops and replaces the original contents of the specified register.

Options: RM LCJ

I (0V000; Index Reg No.) C(10000)

8.48 PMX(00312 2), PMY(00302 2), and PMZ(00332 2)—Logical Product (AND) of Memory with Register: The original contents of the XR, YR, or ZR, whichever is specified in the operation code, replace the contents of the LR. The contents of location M replace the contents of the BR and are combined by the logical product (AND) function with the original contents of the specified register now in the LR. The result, after possible complementing, sets the C control flip-flops and replaces the contents of the specified register.

Options: RM LCJ

I(0V000; V = Index Reg No.) C(10000)

A(20000)

W(000001)

S(200001)

**Restrictions:** If the register appearing in the R subfield is the same as the register specified in the operation code, option A, W, or S is not available.

**8.49** UWX(00712), UWY(00702), and UWZ(00732)—Logical Union (OR) of Word with Register: The original contents of the XR, YR, or ZR, whichever is specified in the operation code, replace the contents of the LR. The resultant DAR number W is combined by the logical union (OR) function with the original contents of the specified register now in the LR. The result, after possible complementing, sets the C control flip-flops and replaces the contents of the specified register.

Options: RM LCJ  $I(0 \lor 000 ; \lor = Index Reg No.)$  C(10000)

8.50 UMX(00312), UMY(00302), and UMZ(00332)—Logical Union (OR) of Memory with Register:

The original contents of the XR, YR, or ZR, whichever is specified in the operation code, replace the contents of the LR. The contents of location M replace the contents of the BR and are combined by the logical union (OR) function with the contents of the specified register now in the LR. The result, after possible complementing, sets the C control flip-flops and replaces the contents of the specified register.

**Restrictions:** If the register appearing in the R subfield is the same as the register specified in the operation code, option A, W, or S is not available.

8.51 H(00005 2)—Shift: The contents of the KR are shifted the number of places specified by the six least significant bits of the resultant DAR number. Bit position 5 (the most significant of the six bits) is treated as the sign bit of the number specified in the remaining five bits. For example, 101111 is as -16; note that the full 23-bit form of -16 is 17 ones followed by 101111. A positive number specifies a shift to the left; a negative number specifies a shift to the right. Bits shifted past position 0 or 22 of the KR are lost. Positions made vacant are filled with zeros. Any number that has an absolute value of 23 through 31, if used, will cause no change in the contents of the KR.

**Options:**

RM

I(0V000;V = Index Reg No.) A(20000)

**Restrictions:** If register K is specified in the R subfield, option A is not available.

**8.52** *HC(10005 2)—Shift Complemented:* The contents of the KR are shifted the number of places specified by the complement of the six least significant bits of the resultant DAR number. Bit position 5 (the most significant of the six bits) is treated as the sign bit of the number specified in the

remaining five bits. For example, 101111 is -16 and is complemented to 010000 or +16. The complement of a positive number is negative and specifies a shift to the right; the complement of a negative number is positive and specifies a shift to the left. Bits shifted past position 0 or 22 of the KR are lost. Positions made vacant are filled with zeros. Any number that has an absolute value of 23 through 31, is used, will cause no change in the contents of the KR.

**Options:**

RM

$$I(00000; V = Index Reg No.)$$

A(20000)

Restrictions: If register K is specified in the R subfield, option A is not available.

**8.53 Q(00001 2)—Rotate:** The contents of the KR are rotated the number of places specified by the six least significant bits of the resultant DAR number. Bit position 5 (the most significant of the six bits) is treated as the sign bit of the number specified in the remaining five bits. A positive number specifies a rotation to the left; a negative number specifies a rotation to the right. Bits rotated past position 0 or 22 of the KR enter the opposite end. Any number that has an absolute value of 23 through 31, if used, will cause no change in the contents of the KR.

**Options:**

RM

$$I(0V000;V = Index Reg No.)$$

A(20000)

Restrictions: If register K is specified in the R subfield, option A is not available.

**8.54 QC(10001 2)—Rotate Complemented:** The contents of the KR are rotated the number of places specified by the complement of the six least significant bits of the resultant DAR number. Bit position 5 (the most significant of the six bits) is treated as the sign bit of the number specified in the remaining five bits. The complement of a positive number specifies a rotation to the right; the complement of a negative number specifies a rotation to the left. Bits rotated past position 0 or 22 of the KR enter

the opposite end. Any number that has an absolute value of 23 through 31, if used, will cause no change in the contents of the KR.

**Options:**

RM

$$I(0V000;V = Index Reg No.)$$

A(20000)

Restrictions: If register K is specified in the R subfield, option A is not available.