# ANALYZING AND LOCATING TROUBLE IN THE 8K CALL STORE NO. 1 ELECTRONIC SWITCHING SYSTEM

|    | CONTENTS PA                                            | AGE | FIGURES PAGE                                  |   |

|----|--------------------------------------------------------|-----|-----------------------------------------------|---|

| 1. | GENERAL                                                | 2   | 1. Call Store Duplication and Bus Duplication | ; |

| 2. | REFERENCE DOCUMENTS                                    | 3   | 2. General Troubleshooting Flowchart 5        | 5 |

| 3. | CALL STORE TROUBLESHOOTING OVERVIEW                    | 4.  | 3. Normal Diagnosis Troubleshooting Flowchart | > |

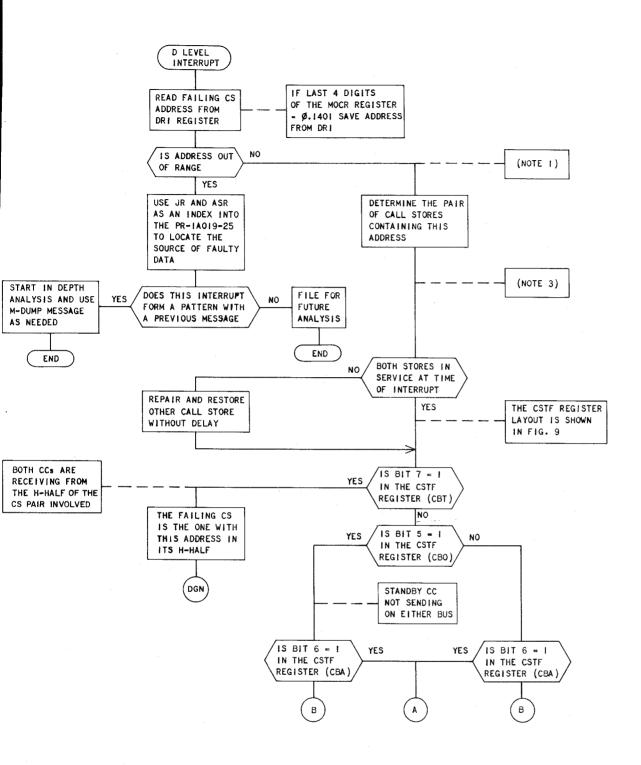

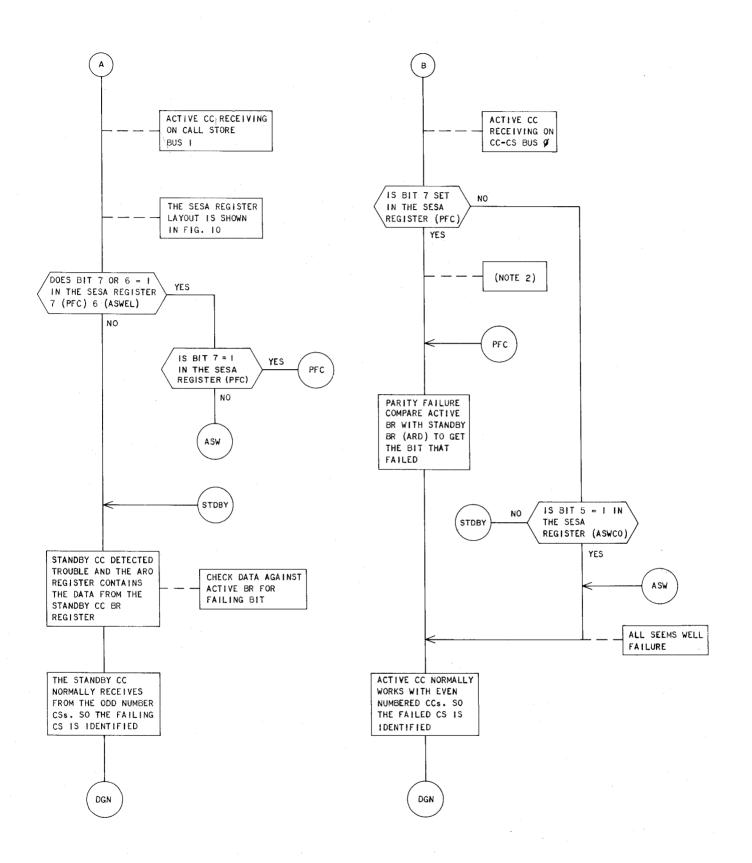

| 4. | DIAGNOSTIC FAILURES                                    | 4   | 4. Raw Data Analysis Flowchart 9              | ) |

|    | NORMAL DIAGNOSTIC FAILURE                              | 4   | 5. Shorted Diode Causing Blind CS 19          | > |

|    | RAW DIAGNOSTIC FAILURE                                 | 4   | 6. Data Sensitive Troubleshooting Aid 25      | 5 |

| 5. | CHECKERBOARD TEST                                      | 26  | 7. Matrix Access Aid                          | 7 |

|    | DATA=ADDRESS                                           | 29  | 8. D-Level Interrupt Register Locations 29    | > |

| 6. | D-LEVEL INTERRUPTS                                     | 29  | 9. CSTF Register Layout                       | ) |

|    | DETECTING FAILING CALL STORE FROM<br>D-LEVEL INTERRUPT | 39  | 10. SESA Register Layout                      | 1 |

| 7. | ERRORS                                                 | 43  | 11. MOCR Register Layout 32                   | 2 |

| 8. | MEMORY CURRENTS                                        | 43  | 12. D-Level Interrupt Analysis Flowchart 37   | 7 |

|    | A. General                                             | 45  | 13. Example of CC CS Error No. 1 39           | } |

|    | B. Types of Currents in the CS                         | 45  | 14. Example of SP CS Error 40                 | 0 |

|    | C. Amplitude Control of the Memory                     |     | 15. MACF Register Layout                      | 1 |

|    | Currents                                               | 46  | 16. Example of CC CS Error No. 2 42           | 2 |

|    | D. Correct Current Amplitudes                          | 49  | 17. Error Troubleshooting Flowchart 44        | 4 |

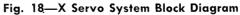

|    | E. Failures Affecting Memory Currents .                | 50  | 18. X Servo System Block Diagram 42           | 7 |

| 9. | BLOWING FUSES                                          | 55  | 19. Access Current Leads 44                   | 8 |

#### NOTICE

Not for use or disclosure outside the Bell System except under written agreement

#### SECTION 231-006-305

|     | CONTENTS                                   | PAGE |  |

|-----|--------------------------------------------|------|--|

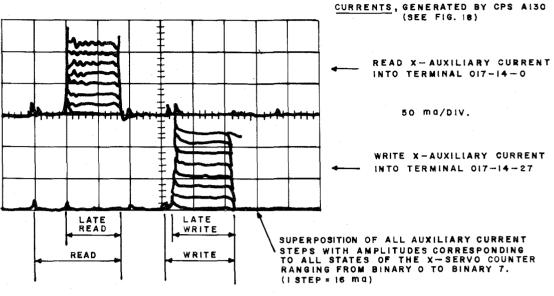

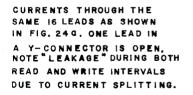

| 20. | Primary X Auxiliary Currents               | . 49 |  |

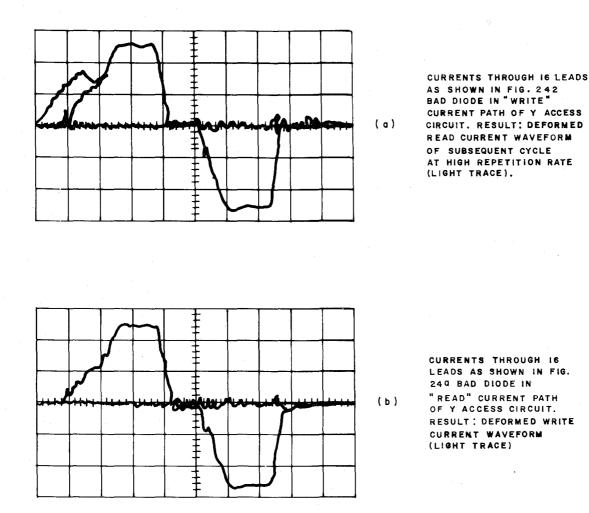

| 21. | Inhibit Currents                           | . 50 |  |

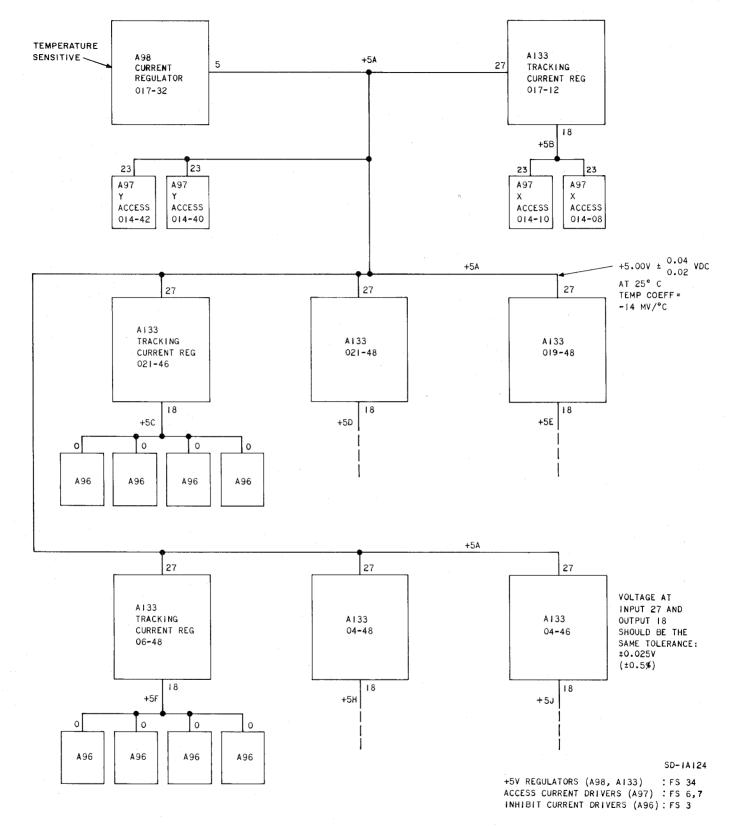

| 22. | Current Regulating Scheme Block Diagram    | า    |  |

|     |                                            | . 51 |  |

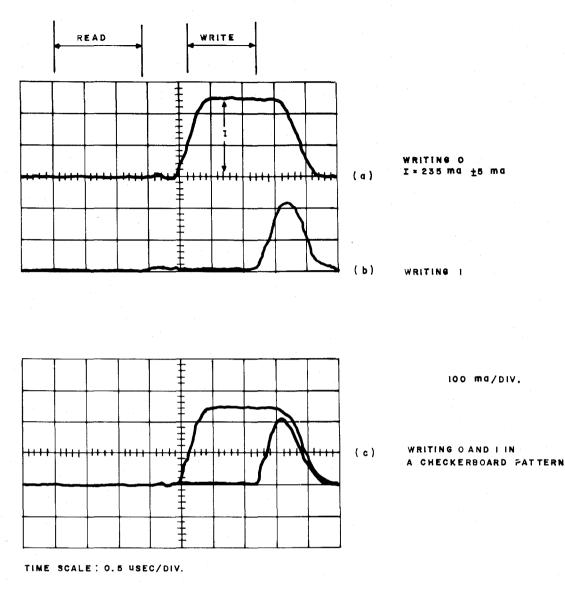

| 23. | X Access Currents                          | . 52 |  |

| 24. | Y Access Currents                          | . 53 |  |

| 25. | Bad Precharge Currents                     | . 54 |  |

| 26. | Bad Module Connector                       | 55   |  |

| 27. | Effects of Access Diodes with Large Revers |      |  |

|     | Storage Conduction                         | . 56 |  |

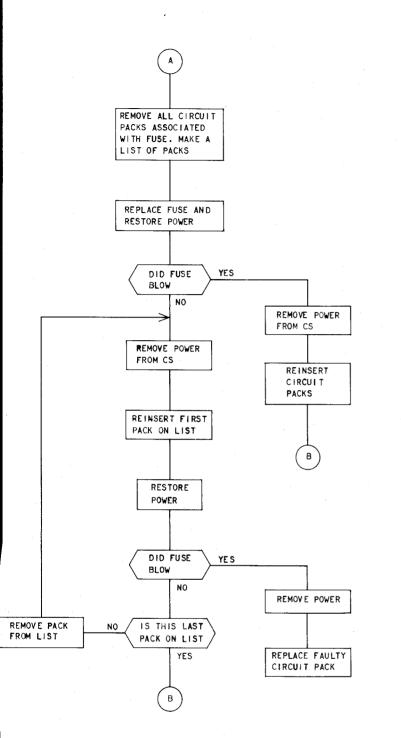

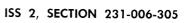

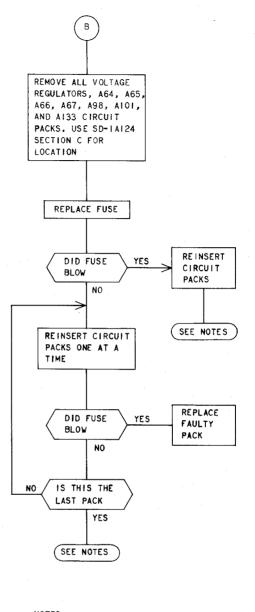

| 28. | Flowchart for Locating Faults of Blow      | n    |  |

|     | Fuses                                      | . 57 |  |

#### TABLES

| Α.              | Call Store Diagnostic                             | 7  |

|-----------------|---------------------------------------------------|----|

| B.              | Primary Hardware Tested by Phase 1<br>and Phase 5 | 11 |

| <b>C</b> .      | Test Run in Phase 1 and Phase 5 .                 | 12 |

| D.              | Call Store Private Scan Points                    | 14 |

| E.              | Primary Hardware Tested by Phase 2<br>and Phase 6 | 15 |

| F.              | Primary Hardware Tested by Phase 3<br>and Phase 7 | 21 |

| G.              | Primary Hardware Tested by Phase 4<br>and Phase 8 | 22 |

| Н.              | Phases 4 and 8 Interface Test Bit<br>Failures     | 33 |

| I. <sup>1</sup> | Delay Generator Circuit Pack Information          | 34 |

| J.              | CSEI Layout                                       | 35 |

## 1. GENERAL

1.01 This section provides an approach to locating and analyzing many of the malfunctions that can occur in the 8K call store used in 2W and 4W No. 1 ESS. Using a flowchart as a general procedure allows the detailed procedure to be referenced on the flowchart.

**1.02** This section is reissued to include CTX-6 Issue 8 and later generics and to make the following changes:

(a) To make changes to Fig. 4 and 17

(b) To add Tables H and I.

1.03 The call stores (CSs) are memory units that store information related mainly to the handling of calls as they are processed. The CS is used for short term scratch pad storage of events that occur in the No. 1 Electronic Switching System (ESS). Certain long term information is also stored temporarily in the CS until enough of such information accumulates to make it worthwhile to write it into the program store memory cards.

1.04 The CSs are erasable read-write temporary memories used by the central control (CC) and the signal processor (SP). The information contained in a CS is organized in words of 24 bits. The 24th bit of each word is used for parity checking. Each word occupies one location in the memory unit of the CS and is identified by a unique address. Inputs from a CC or an SP specify the operation (reading or writing), CS address, and data (writing only). The CS responds to the order and, in the case of reading, sends the word read to the CC or SP.

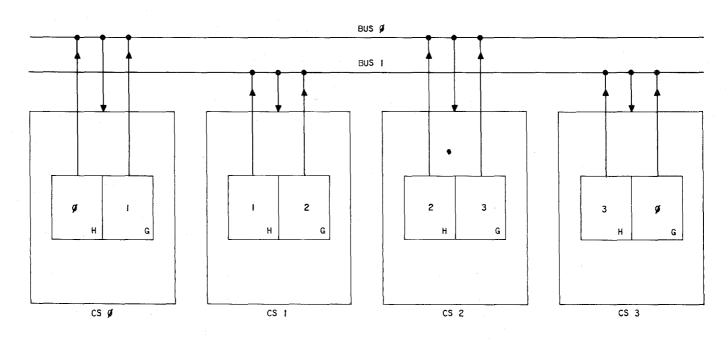

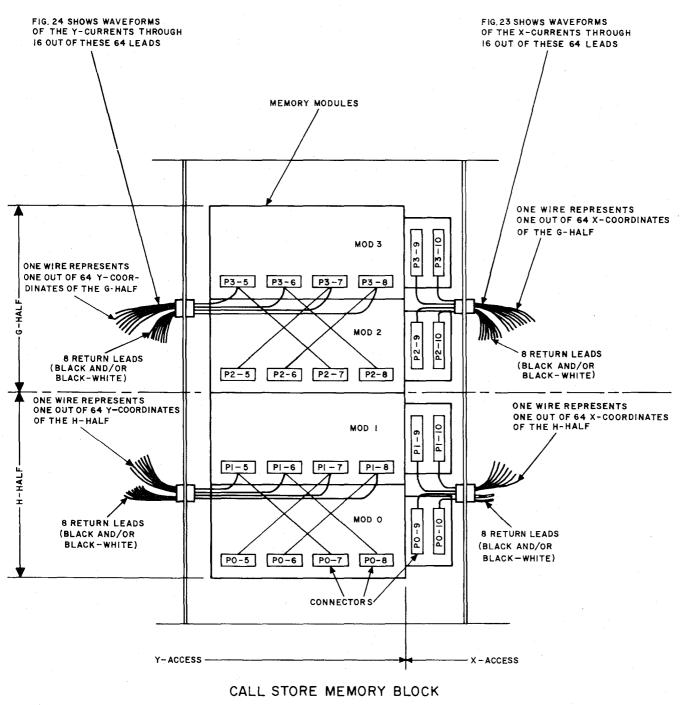

1.05 The memory unit of each CS consists of four memory modules. Two of these modules are connected to make the G-half of the memory unit. The other two modules are connected to make the H-half of the memory unit. Each half has a storage capacity of 4096 words (24 bits each), and each CS memory has 8192 storage addresses. In order to achieve maximum reliability, all information stored in the H-half of one CS is duplicated in the G-half of another CS and vice-versa

(Fig. 1). The CC or SP communicates with the CSs over duplicated buses.

1.06 The number of CSs needed in each No. 1 ESS depends on the office size. For example, in a 2-wire No. 1 ESS office, a maximum of 39 CSs (78 store halves) can be used with the pair of CCs and a maximum of 8 CSs (16-store halves) can be used with each duplicated pair of SPs.

**1.07** The following abbreviations are used in this section:

۴

MCC

| ASW | All Seems Well              |

|-----|-----------------------------|

| C   | Celsius Temperature         |

| CPD | Central Pulse Distributor   |

| CS  | Call Store                  |

| CW  | Control Write               |

| CR  | Control Read                |

| ESS | Electronic Switching System |

| FF  | Flip Flop                   |

|     |                             |

Master Control Center

SD Signal Distributor SP Signal Processor

#### 2. **REFERENCE DOCUMENTS**

| CD-1A124-01 | Circuit Description                                           |

|-------------|---------------------------------------------------------------|

| IM-1A001    | Input Message Manual                                          |

| OM-1A001    | Output Message Manual                                         |

| PA-591003   | Translation Specification                                     |

| PD-1A018    | Call Store Deferred Fault<br>Recognition Programs Description |

| PD-1A019    | Diagnostic Program Description                                |

| PD-1A120    | Translation Program Description                               |

| PF-1A019    | Program Flowchart                                             |

| PK-1A019    | Raw Data Analysis                                             |

| PR-1A019-26 | Program Listing                                               |

| SD-1A124-01 | Schematic Drawing                                             |

| TLM-1A124   | Trouble Locating Manual                                       |

Fig. 1—Call Store Duplication and Bus Duplication

#### SECTION 231-006-305

| 231-006-101   | 8K Call Store Description                                                         |

|---------------|-----------------------------------------------------------------------------------|

| 231-006-501   | 8K Call Store Margin Checks—Using<br>762A Tool                                    |

| 231-006-801   | 8K Call Store Memory Assembly<br>Replacement Procedure                            |

| 231-011-102   | Maintenance Program Organization<br>Description                                   |

| 231-109-301   | Analyzing Maintenance Interrupts                                                  |

| 231-125-301   | Master Control Center—Alarm,<br>Display, and Control Panel—Method<br>of Operation |

| 3. CALL STORE | TROUBLESHOOTING OVERVIEW                                                          |

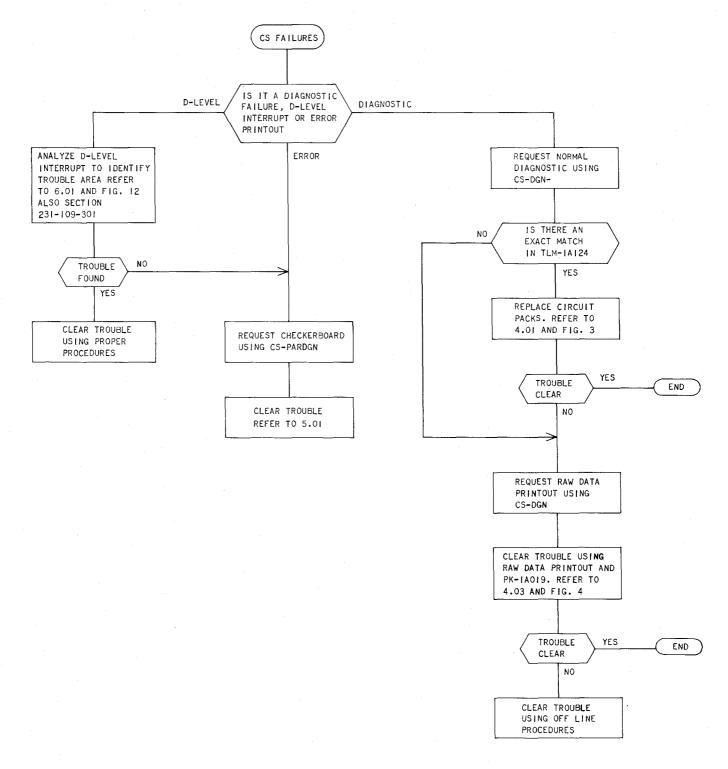

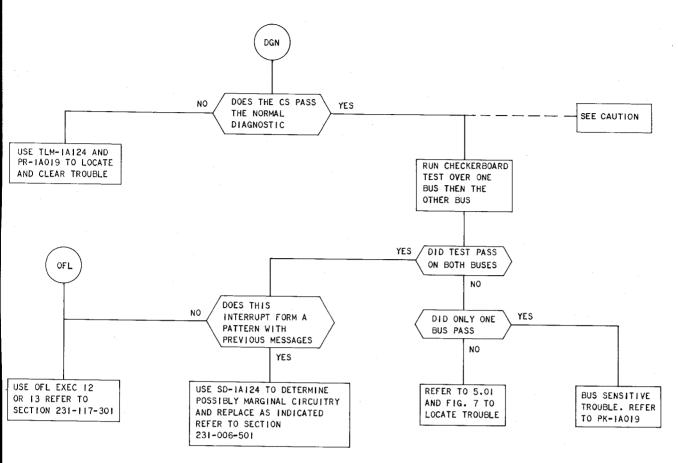

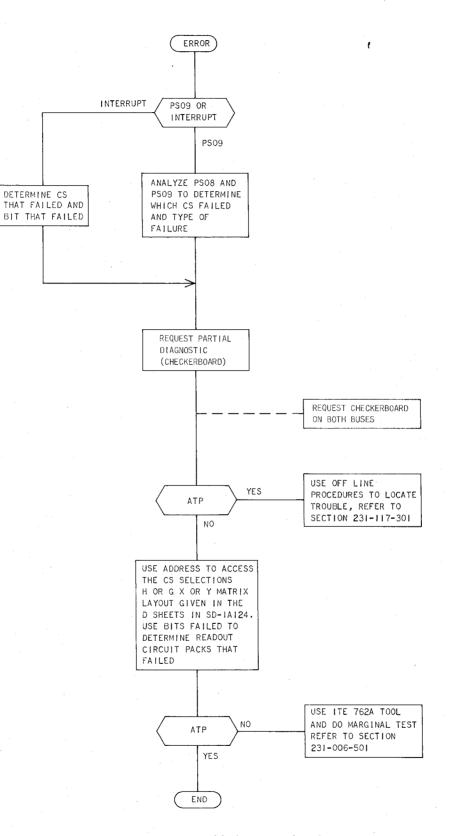

**3.01** The flowchart in Fig. 2 gives an overall indication of the types of CS troubles that can be encountered. The flowchart also references the procedure that can be used in troubleshooting.

**3.02** The basis of the flowchart layout is to deal with one type of trouble at a time.

#### 4. DIAGNOSTIC FAILURES

#### NORMAL DIAGNOSTIC FAILURE

**4.01** A normal diagnostic printout can be generated by the system. It can also be requested via the TTY with the CS-DGN input message (refer to IM-1A001 for complete message) or via the appropriate CS frame control. The output message is as follows:

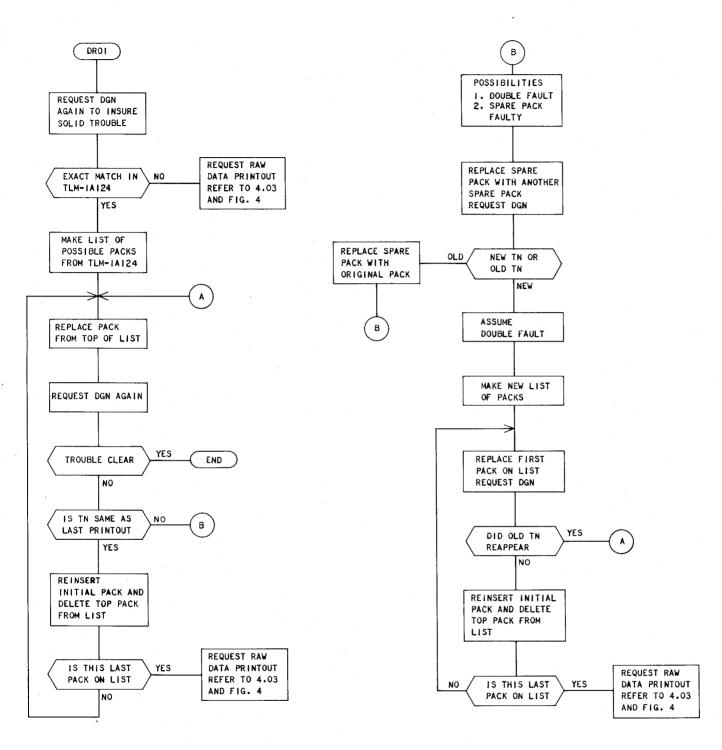

DR01 DGN RES CS 2 0577 0034 6600 = universal trouble number. 4.02 The first line of the above message identifies the failing unit as CS 2. Line two contains the 12-digit trouble number that may be found in TLM-1A124. First, however, the maintenance personnel should request another diagnosis to insure a solid fault. The flowchart procedure is given in Fig. 3. A step-by-step procedure is given in TLM-1A124, Section B.

#### RAW DIAGNOSTIC FAILURE

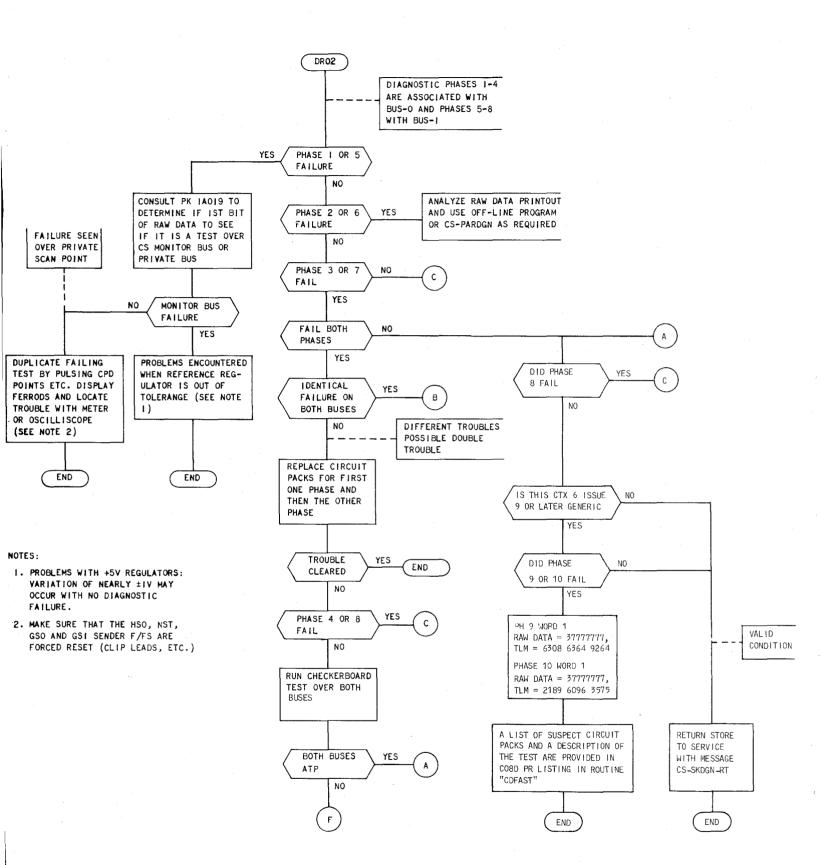

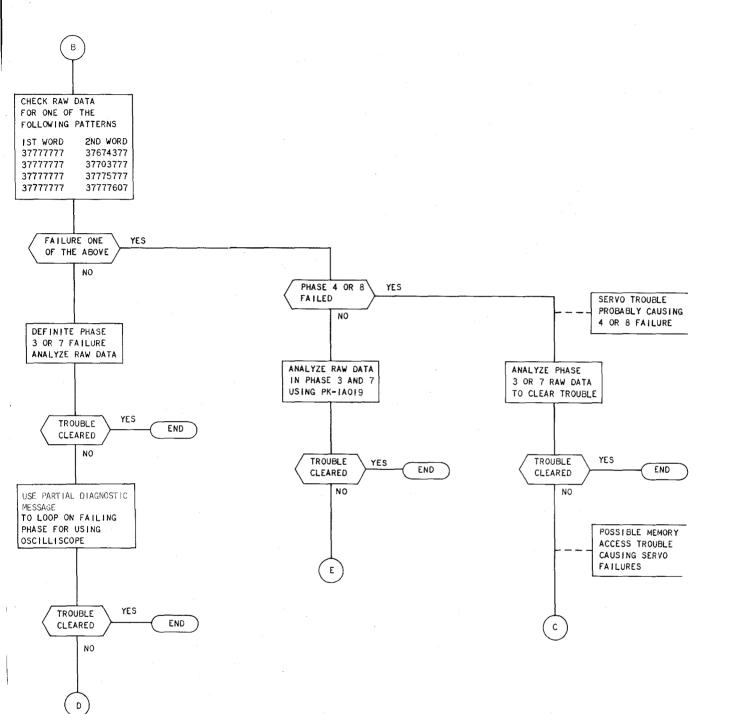

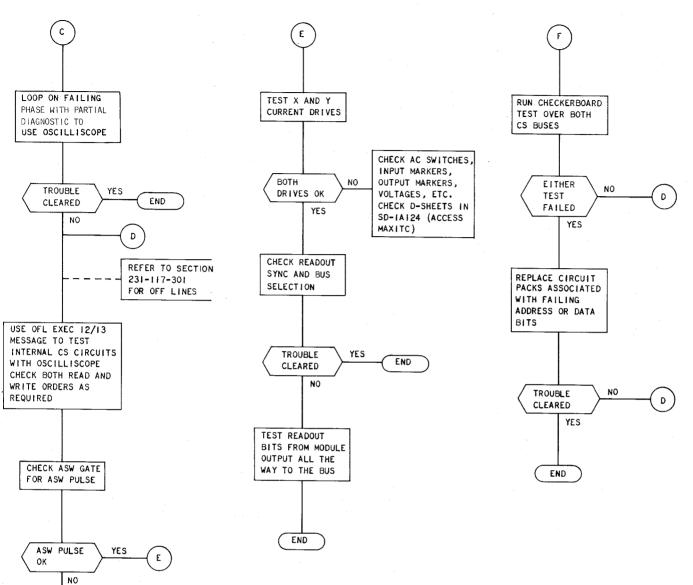

4.03 The CS diagnostic program is comprised of a series of diagnostic tests. Basically, it divides the CS into four functional hardware blocks. The tests are run first on bus 0, then on bus 1 (Table A). Figure 4 gives a flowchart approach to troubleshooting a CS using the raw data printout.

#### Phase 1 and Phase 5

4.04 Phase 1 and phase 5 are used to test basic internal CS circuitry associated with routing, lockout conditions, and voltage levels. Most of the tests in these phases are carried out by operating central pulse distributor (CPD) points or relays within the CS, and scanning either the CS monitor bus or private scan points to verify expected results. A list of primary hardware tested by these phases is shown in Table B. The tests that are run are shown in Table C.

4.05 The CS monitor bus consists of eight scan points having a fixed assignment on master scanner 00, row 50, ferrods 0 through 7. These scan points are connected to all the CSs in the office. However, only the store currently being diagnosed will have relays operated to connect the monitor bus leads to the internal CS circuitry.

#### Fig. 2—General Troubleshooting Flowchart

Fig. 3—Normal Diagnostic Troubleshooting Flowchart

## TABLE A

| PHASE | NO. OF WORDS<br>OF TEST DATA<br>GENERATED | PRIMARY HARDWARE<br>TESTED PER PHASE                    |

|-------|-------------------------------------------|---------------------------------------------------------|

| 1     | 29                                        | CPD, SD, and MS access to the call store via CS bus 0   |

| 2     | 40                                        | Control and maintenance logic circuitry via CS<br>bus 0 |

| 3     | 2                                         | CS X and Y servo counters via CS bus 0                  |

| 4     | 9                                         | Memory access and logic circuitry via CS bus 0          |

| 5     | 29                                        | CPD, SD, and MS access to the call store via CS bus 1   |

| 6     | 40                                        | Control and maintenance logic circuitry via CS<br>bus 1 |

| 7     | 2                                         | CS X and Y servo counters via CS bus 1                  |

| 8     | 9                                         | Memory access and logic circuitry via CS bus 1          |

## CALL STORE DIAGNOSTIC

Fig. 4—Raw Data Analysis Flowchart

## TABLE B

رسمر

يمحنني

¢

## PRIMARY HARDWARE TESTED BY PHASE 1 AND PHASE 5

| FS IN<br>SD-1A124                           | DESCRIPTION                                                                                                                |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| 33<br>33                                    | CS (i) lamp fuse<br>CS (i) manual control panel status<br>and fuse alarm                                                   |  |

| $\begin{array}{c} 24\\ 24\\ 21 \end{array}$ | Lockout conditions and circuitry<br>(a) Permanent RO sync<br>(b) Permanent precharge enable<br>(c) Permanent H code enable |  |

| 22                                          | TBL0 FF, TBL1 FF, RO FF                                                                                                    |  |

| 35                                          | CS monitor bus<br>(a) Verify all CS disconnected<br>from the CS monitor bus<br>(b) Check for false currents                |  |

| 35                                          | <ul> <li>(c) Check for false grounds</li> <li>(d) CS (i) relays (primary and secondary)</li> </ul>                         |  |

| 34                                          | (e) CS (i) voltage regulator                                                                                               |  |

## TABLE C

## TEST RUN IN PHASE 1 AND PHASE 5

| TEST RUN                                                                                                                                                  | RESULTS                                                                                                                                                                                                                                                                                              | REFERENCE                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 1. Lamp Fuse                                                                                                                                              | The lamp fuse scan point is read and the result recorded. Curent should flow; thus, the lamp fuse scan point (SC2) should read 0.                                                                                                                                                                    | PD-1A019-01 (Page 53)<br>SD-1A124 (FS 33 Power<br>Control LF Lead)              |

| 2. Manual Control<br>Panel Status and<br>Fuse Alarm Circuit                                                                                               | The manual control panel status scan<br>points SC0 and SC1 are scanned and<br>recorded. If the manual control panel<br>is in the <i>normal</i> state, both scan points<br>should read 0. Any non-normal state,<br>inhibit request, manual power off, or fuse<br>alarm will yield a non-zero reading. | PD-1A019-01 (Page 53)<br>SD-1A124 (FS 33 Power<br>Control SC0 and SC1<br>leads) |

| 3. Permanent RO<br>Sync, Precharge<br>Enable, or H-code<br>Enable Lockout<br>Condition                                                                    | Test the permanent RO output sync and<br>precharge enable lockout conditions. Scan<br>points 0TB and 1TB are scanned; if no<br>lockout condition exists, scan points<br>should read 0.                                                                                                               | PD-1A019-01 (page 54)<br>SD-1A124 (FS 22<br>System Control)                     |

| 4. TBL0, TBL1,<br>and RO FFs                                                                                                                              | Test the ability of the RO, TBL0, TBL1<br>FFs to be set and reset via the CPD. FFs<br>are scanned via scan point RO0, RO1,<br>OTB, and 1TB. Set state will cause the<br>scan point to read A1, reset A0.                                                                                             | PD-1A019-01 (Page 54)<br>SD-1A124-01 (FS 22<br>System Control)                  |

| <ul> <li>5. CS Monitor Bus<br/>for:</li> <li>A. A clear<br/>monitor bus<br/>(verify all<br/>CSs are<br/>disconnected<br/>from monitor<br/>bus)</li> </ul> | A. SD point VPT0 is released in every CS<br>in the office, disconnecting each CS<br>from the monitor bus. This is verified<br>by reading the VT scan point; if<br>disconnected, VT scan point should<br>read 0.                                                                                      | <b>PD-1A019-01 (Page 54)</b><br>SD-1A124-01 (FS 35<br>Voltage Regulator Test)   |

| B. All Voltage<br>Regulators                                                                                                                              | B. SFC 12 checks the CS voltage regulators<br>by activating appropriate relays via SD<br>operations, and scanning the voltage<br>regulator monitoring scan points (CSM 0<br>through CSM 7).                                                                                                          | PD-1A019-01 (Page 55-59)                                                        |

4.06 In addition to the eight common scan points of the CS monitor bus, each CS has nine private scan points. To determine the scan points associated with a particular CS, use the TTY input message VFY-UNTY-1503XX. (Refer to input message manual IM-1A001 for the complete message.) The TR13 output message received from this request will yield not only the private scan point for a given CS, but the CPD and signal distributor (SD) assignments as well. The TR13 output message is shown below. (Refer to OM-1A001 for complete message format.) CS private scan points and their significance are shown in Table D.

| TR13 30  | 3 = Unit type  0 = CS00         |

|----------|---------------------------------|

| 04236400 | Convert octal numbers to binary |

| 05004151 | Use PA-59103, Section 030, unit |

| 02000254 | type 3 for complete breakdown   |

| 07001500 | of translators.                 |

4.07 Phase 1 and phase 5 failures can be located by using one of the following test methods, assuming TLM-1A124 does not aid in finding the trouble. DC test procedures can be used. This consists of displaying the CS monitor bus ferrods at the master control center (MCC) and duplicating the failing test. (Refer to Section 231-125-301 for procedures.) First. consult the raw data printout and PK-1A019 to determine the state of the hardware Next, block/operate the indicated components. relays and observe the ferrod condition. From here, the trouble can be pursued by using either a meter or an oscilloscope.

4.08 Similar steps can be followed when the trouble is detected over one of the CS private scan points. Consult the raw data printout and PK-1A019 to obtain all the circuitry involved. Using the VFY-UNTY message, obtain scanner, CPD, and SD assignments. Refer to IM-1A001 for complete input message. By displaying the proper scan row at the MCC and pulsing the CPD or SD points using the TTY input message T-CPD or T-MISD, the suspected ferrod point can be observed. Use DC test procedures to clear the trouble.

#### Phase 2 and Phase 6

**4.09** Phase 2 and phase 6 are carried out by using control read (CR) and control write (CW)

orders. These control orders have the facility of testing most internal CS circuitry without accessing the memory area. There are twelve control orders, six CR and six CW orders. Control instructions can be recognized by the nonmemory mnemonic N (NX, BN, NBTA, etc).

**4.10** Data register can be written into and can also be read. This operation verifies that the CS can receive each bit from the bus and also the ability to send 24 bits of data back to the CC.

**4.11** Name and Answer Flip Flops (FFs) can be both written and read. The name FFs are used to establish the K code for the G-half of a CS. The answer FFs control selection of the bus to be used for sending data back to the CC (GS0, GS1, HS0, and HS1 FFs).

**4.12** Accumulate timing 1 and 2 can only be written. In each case a CS FF is set. This will start the timing sequences. At proper intervals, designated timing points are interrogated and the results gated into the data register. Either of these orders will normally be followed by a CR order of the data register.

4.13 Servo counters can be read or control written to either the set or reset states. The servo counters are 3-bit binary counters designed to regulate the X and Y current drives. These counters can be control written to either all ones or all zeroes, and not to any value in between.

**4.14 DC** switches and parity: These 16 Y access switches and 16 X access switches can be control read. The dc switches provide the access into the memory module. They are activated by decoding bits in the address register. In addition to the dc switches, there are five points in the parity check circuit which are checked by this control read order.

**4.15** Fault test points are tested with a control read of several semi-dc gate conditions which are fixed during a cycle and can be gated onto the bus. This test group includes the fault FFs.

#### TABLE D

| SCAN               | POINT                   | PURPOSE                                                                                                                                           |

|--------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| SC0<br>0<br>1<br>1 | SC1<br>0<br>1<br>0<br>1 | CS control panel keys normal<br>Manual power off<br>Inhibit request<br>Fuse alarm                                                                 |

|                    | SC2                     | ${f LF}$ scan point — current flows if the lamp fuse is good                                                                                      |

|                    | SC3                     | m DC0- m Reset only via CPD operation                                                                                                             |

|                    | SC4                     | TBL1 scan point<br>Set — Inhibits CS communication via CC-CS Bus 1<br>Reset — Allows CS to communicate with CC via<br>bus 1 if the RO FF is reset |

|                    | SC5                     | TBL0 scan point<br>Set — Inhibits use of CC-CS Bus 0<br>Reset — Allows use of CC-CS Bus 0 if RO FF is set                                         |

|                    | SC6                     | RO1 scan point – RO FF set allows CS to receive over<br>Bus 0 if the TBL0 FF is reset                                                             |

|                    | SC7                     | RO0 Scan point – RO FF reset allows CS to receive<br>from BUS 1 if the TBL0 FF is reset                                                           |

|                    | SC8                     | VT scan point — saturated indicates that the<br>CS is disconnected from the CS monitor bus                                                        |

#### CALL STORE PRIVATE SCAN POINTS

**4.16** Any failure in either phase 2 or phase 6 will result in omitting the remainder of the diagnostic phases usually run on the same CS bus. For example, if phase 2 fails, phase 3 and phase 4 will not be run. The primary hardware tested by phase 2 and phase 6 is given in Table E.

4.17 Failures in phase 2 or phase 6 can be located by using the input message CS-PARDGN and analyzing the printout. (Refer to IM-1A001 for complete message.) Also use the ØFL-EXEC message to loop on a section of the program which will duplicate the first failure in the raw data printout. (Refer to Section 231-117-301.) To accomplish this, use PF-1A019 to locate the global that can serve as a reference into PR-1A019. Once the specific test has been identified in PR-1A019, the address can be applied to the ØFF-LINE

message. The trouble can be located with an oscilloscope.

## Caution: The following procedure requires additional analysis and should not be considered until all other methods have failed.

4.18 The appropriate CR and CW orders can be written on a program store card and executed by means of the ØFL-EXEC-03 program (Section 231-117-301 for 2-wire and Section 231-417-301 for 4-wire). The orders to be written can be determined from analysis of the raw data and PK-1A019.

#### Example of Phase 2 and Phase 6 Failure

**4.19** The following is a step-by-step procedure used for locating one fault in phase 2. This

## TABLE E

## PRIMARY HARDWARE TESTED BY PHASE 2 AND PHASE 6

| FS IN<br>SD-1A124 | DESCRIPTION                                                           |

|-------------------|-----------------------------------------------------------------------|

| 6                 | Y access dc switches                                                  |

| 7                 | X access dc switches                                                  |

| 10                | *Bus 0 receiver cores                                                 |

| 12                | *Code register                                                        |

|                   | (a) Bus 0 inputs and sync                                             |

| 13                | *Mode register (C,G,H,R,W,PKA)                                        |

|                   | (a) Bus 0 inputs and syncs                                            |

| 14                | *Address register                                                     |

|                   | (a) Bus 0 inputs and sync                                             |

| 15                | *Bus 0 data inputs (pulse directors)                                  |

|                   | and syncs                                                             |

| 16                | Enable decoder (H and G name)                                         |

| 17                | Mode decoder (C,G,H)                                                  |

| 18                | Order decoder (CR,CW,NBTA,NBTB,                                       |

|                   | GMR,GMW,HMR,HMW,NR,NW)                                                |

| 19                | Control address decoder                                               |

| 20                | Test register (TT FFs and control                                     |

|                   | and normal or MTCE data reg FFs                                       |

|                   | reset)                                                                |

| 21                | Fault register (ASW,GH,MUM,TCF,DC0                                    |

|                   | FFs)                                                                  |

| 22                | System control (code, mode, and                                       |

|                   | address register bus inhibit gates                                    |

| 23                | and O.5T4.5 cycle lockout gates)<br>*Answer control (bus 0 routing of |

| 20                | control and MTCE order info onto                                      |

|                   | output bus 0)                                                         |

| 24                | Sequence control (CS timing chain)                                    |

| 25                | Data register                                                         |

| 26                | Parity check (code, address, PKA                                      |

|                   | parity check circuit)                                                 |

| 27                | *Bus 0 bus sending transformers                                       |

|                   | (SP0) (Control mode sending                                           |

|                   | only)                                                                 |

| 15                | Variable G name FFs and normal                                        |

|                   | mode answer routing FFs                                               |

|                   | *FOR PHASE 6 CHANGE BUS 0 TO BUS 1                                    |

procedure will show the logic used in finding the fault.

#### CS-DGN-RCS03.PF

| 08 DR02 RAW    | CS 3        |

|----------------|-------------|

| PH 1 ATP       | PH 5 ATP    |

| PH 2 STF       | PH 6 STF    |

| 0000000        | 00000000    |

| 00160000       | 00160000    |

| 0000000        | 00000000    |

| 0000000        | 0000000     |

| 0000000        | 0000000     |

| 0000000        | 0000000     |

| 0000000        | 0000000     |

| 0000000        | 00000000    |

| 0000000        | 0000000     |

| 0000000        | 00000000    |

| 0000000        | 00000000    |

| 0000000        | 00000000    |

| 0000000        | 00000000    |

| 0000000        | 00000000    |

| 00000052       | 00000052    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 3777777     |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 37777777       | 37777777    |

| 5514 4943 0422 |             |

|                | 5972 1409 2 |

|                |             |

**4.20** The DR02 printout shows that phase 2 and phase 6 failed the same on both buses. It also shows that bits 13, 14, and 15 failed in word 2.

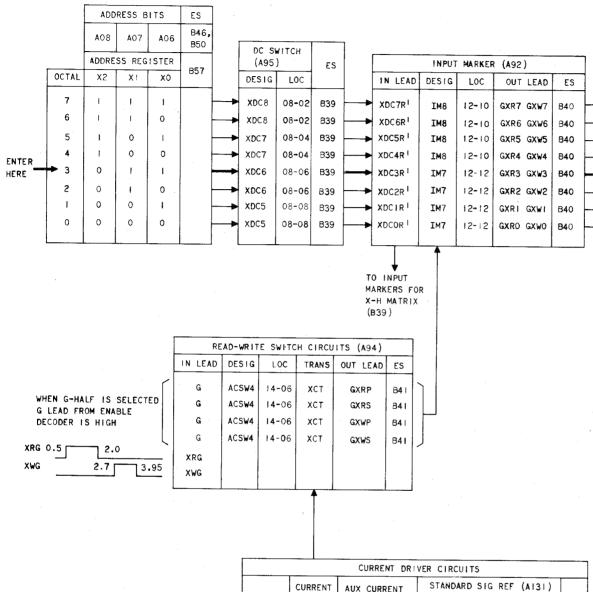

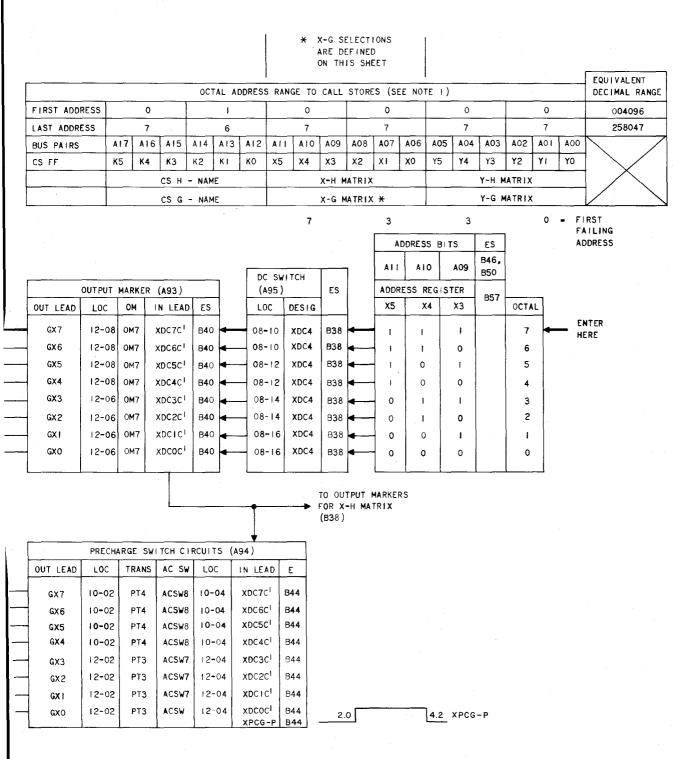

**4.21** Use PK-1A019 to analyze failing word and bits. Word 2 in this case is testing the X dc switches. The first bit to fail was bit 13, which is looking at the state of gate XDC5C'.

**4.22** Use SD-1A124, sheet index, to locate the X access FS. The sheet index shows that the X access is in FS7. The XDC5C' gate is shown on sheet B38 and is from circuit pack 08-12, a dc switch.

**4.23** Another possible failure might be circuit pack 08-10. The printout shows bits 14 and 15 failing. These two bits are gates XDC6C' and XDC7C'.

4.24 The DR02 printout also gives a universal trouble number at the end of the printout. Use TLM-1A124 by finding the exact match; it shows circuit pack 08-12 could be the trouble.

#### Example of Fault in Phase 2 and Phase 6

**4.25** The following is a step-by-step procedure used for locating one fault in phase 2. This procedure will show the logic used in finding the fault.

**4.26** The following messages were received on the TTY. Some were machine generated and some were requested at the TTY.

5972 1409 2404 UNIV TBL NO. 3295 7391 2760

## 27 MA14A 00000000 01102333 01024345 01026532 21254750 **0**1572000

27 MA14 CC INT 01165440 01165440 10300000 01165432 00000000 00000000 00011400 01163671 03777777 00000000 36612337 01165440 00010510 00020503 02000040 03101401 00010550 00002010

27 DR01 TBL NOS CS 1 PH 2 STF 4742 3416 7205 PH 6 STF 2502 6109 3750 UNIV TBL NO. 7245 1525 8141

**4.27** The TLM approach does not yield a solution, so the next step would be to request a cell data printout as follows:

#### CS-DGN-CCS01.PF

## \*\*29 DR01 TBL NOS CS 1 CELL NOS 4295 1883 1497 7413 4839 1617 6998 5021 1710 1018 6316 1755 0107 6811 1039 2815 3052 1280 4485 5184 1656 4794 0010 1130 7549 1314 1620 7881 2127 1940

**4.28** Using TLM-1A124, look for an exact match in section E. In this case, there is no match that yields a solution to this fault. The next step would be to request a raw data printout as follows:

## The system responds with the following printout:

#### CS-DGN-RCS01.

Page 17

| 32 DR02 RAW CS | 1      |       |

|----------------|--------|-------|

| PH 1 ATP       | PH 5   |       |

| PH 2 STF       | PH 6   |       |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 0000000        | 00000  | 000   |

| 34036303       | 34036  | 303   |

| 04036303       | 04036  |       |

| 37777777       | 37777  |       |

| 37777777       | 37777  |       |

| 37777777       | 37777  | • • • |

| 37777763       | 37777' |       |

| 00000100       | 00000  |       |

| 00000100       | 00000  |       |

| 26374040       | 26374  |       |

| 26365076       | 26365  |       |

| 26305044       | 26305  |       |

| 26074044       | 26074  |       |

| 26374076       | 26374  |       |

| 26374076       | 26374  |       |

| 26374076       | 26374  |       |

| 26374076       | 26374  |       |

| 26374076       | 26374  |       |

| 26374076       | 26374  |       |

| 26374074       | 26374  |       |

| 26374074       | 26374  |       |

| 05416317       | 05416  |       |

| 05411477       | 05411  |       |

| 0000000        | 00000  |       |

| 01360000       | 01360  |       |

| 00000100       | 01300  |       |

| 00260000       | 00000  |       |

| 00200000       | 00260  |       |

| 4742 3416 7205 | 00000  | 100   |

| 4142 3410 7203 |        |       |

2502 6109 3750 UNIV TBL NO. 7245 1525 8141 4.29 The following procedure is used to analyze

the raw data and to locate the fault. It should be noted that several documents are used in analyzing the failure.

4.30 Raw data: word 14, phase 2 and phase 6, is the first failing word. Phase 2 and phase 6 fail exactly the same. The fault is probably not in circuits associated with only one bus. PK-1A019 shows that word 14 is the result of testing address parity checker outputs PAR 1 and PAR 2.

4.31 PF-1A019 A sheets show that phase 2 and phase 6 are in SFC 13, and the E sheets show that the parity checker test begins at CDPARS. CDPARS can be found in PR-1A019-26. Using the B sheets of PF-1A019, it is found that ADRKK is the CS location where word 14 of phase 2 and phase 6 is stored. Finding ADRKK in the symbol table of PR-1A019-26 will give the page that CDPARS starts on.

**4.32** Word 15 also fails: PR-1A019-26 and PD-1A019 state that if both words 14 and 15 fail, the fault is not in the parity checker circuit. The circuits for PAR 1 and 2 are independent of the circuits for PAR 3 and 4. A single fault in the parity check circuits will make one word or the other fail, but never both. If both fail, the fault must be in a circuit other than the parity checker.

**4.33** The test of the next 3 raw data words (16,

17, 18) is omitted and the raw data is faked in as all 1s. The test resumes at word 19 at CDCMIT in PR-1A019-26. Word 19 points toward gates CR6', CR5', and CR1' in the control address decoder. These gates are on circuit packs 26-07 and 26-09.

4.34 Words 20 and 21 point towards failure of

the CS to return an all seems well (ASW) signal. Word 22 points towards no CS response to control mode operations. At this point, it might indicate a faulty mode register. Words 23 through 40 failures do not match any patterns given in PK-1A019. The list of possible circuit packs has grown quite large at this point.

**4.35** Using ØFF-LINE methods to locate the fault, the following procedure was used (Section 231-117-301 for 2-wire and Section 231-417-301

for 4-wire).

-Failing address from D-Level interrupt

4.36 Using an oscilloscope, it soon becomes apparent that nothing is happening in the store. Both TBL0 and TBL1 FFs are set. This cuts the store off from both buses. By trying to reset the TBL0 FF, it is found that it sets right away.

Caution: Do not reset the TBL1 FF. As shown in the D-level interrupt, this is the active bus and will put the store back on-line.

**4.37** With the oscilloscope connected to the PD0-P'

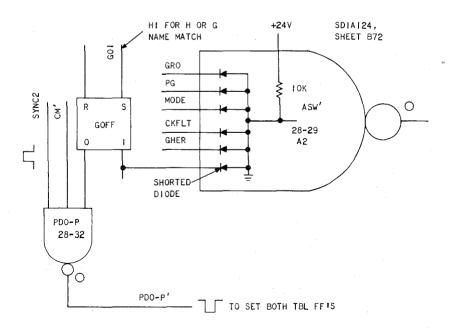

lead (30-26 pin 20) with the TBL0 FF reset, the set pulse appears every cycle on the PD0-P' lead. Tracing back to the GO FF with the oscilloscope, a low is found feeding back to the 1 output from the PG lead. The low was from a shorted diode on pin 4 of gate ASW'. This is an A2 pack at location 28-29. Figure 5 shows the shorted diode in the circuit.

4.38 What the shorted diode does: At

the end of the CS cycle, the code mode and address registers are reset by RST1-P'. This makes leads PG and GR0' go low. Even though GO1 also goes low at the same time, the 1 output of GO FF is locked low through the shorted diode. The 0 side is then locked high. If the next CS operation is **not** a control mode operation (CM' high), the sync 2 (the sync that accompanies R, W, and PKA at 19T21) will fire the gate and set both TBL0 and TBL1. The GO FF circuit is supposed to fire in the event the CS gets a fault which makes it recognize a permanent name match.

**4.39** The CS will run okay as long as a string of control mode operations is received. A normal, G, or H maintenance mode will set both TBL0 and TBL1. With both FFs set, the store is blind to anything on the buses.

4.40 The diagnostic program carefully resets both TBL0 and TBL1 FFs at the beginning of each segment. The fault does not show up as a test failure until the parity circuit test of CDPARS. The program takes a segment break and does a couple of BMAPs (normal mode). Then the program

Fig. 5—Shorted Diode Causing Blind CS

does the parity circuit test. The BMAPs set TBL0 and TBL1 FFs, so the test fails whenever a 1 is expected from the CS.

#### Phase 3 and Phase 7

4.41 Phase 3 and phase 7 test the servo circuitry over each of the two CS address buses.Since the address bus should have no effect on the servo system, the results of phase 3 and phase 7 should be identical. If the results of these two phases differ, refer to Fig. 4 to determine some of the possible trouble causes.

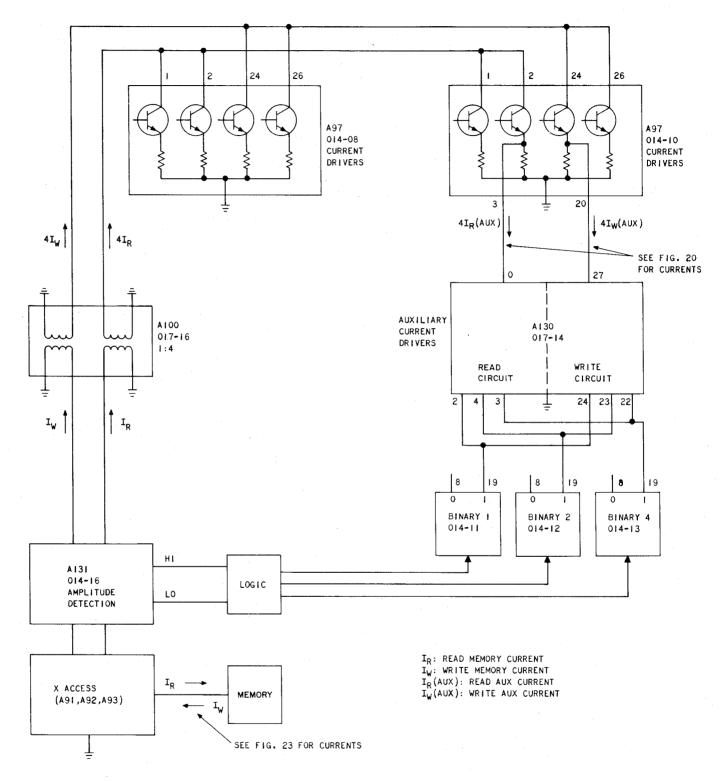

4.42 Two binary counters of three bits each comprise the servo control system. These counters are used to alter the current in the X and Y current drives. During each CS cycle, the read current is monitored, and either increments or decrements the servo binary counter when the current deviates up or down from a predetermined level. This change in the binary counter causes a 4 ma change in the read current during the next CS cycle.

4.43 Under ideal conditions the three-bit servo binary counters should be stabilized at a setting of 3 or 4. This phase tests the servo circuitry by setting or resetting the binary counters to one of two extremes. Following a series of test orders, the servo counters are tested to verify that the CS circuitry has caused the binary counter to step from the extreme to a new state. Additionally, each binary counter is tested for 64 consecutive cycles to verify that an oscillation condition does not exist which \_will cause a change on each operation.

**4.44** Since the servo system is directly related to the X and Y current drives, troubles in either of these drives can result in any invalid trouble indication in phase 3 or phase 7. In some instances, a failure in phase 3 or phase 7 does not warrant the CS being left out of service. These failures may be caused by the servo binary counter operating at one of the extremes, while the operation of the CS is not otherwise affected. Such a

condition could be the result of temperature or component changes and, in some programs, is commonly encountered during the midnight routines. The primary hardware tested by phase 3 and phase 7 is shown in Table F.

## Phase 4 and Phase 8

4.45 Phase 4 and phase 8 consist of testing the CS memory modules. These phases generate nine words of test data. Unlike the other CS diagnostic, these phases produce raw data which must be considered as a nine-word entity and not as individual failure bits. This means that to locate a failure point in PK-1A019, an exact match must be found for all nine words of the raw data printout.

#### Test Word

- 1. H-half addresses Ø.0000 through Ø.0077 are written first with a test word of  $\emptyset.14631463$ and then read to verify the proper data. Next, the same procedure is followed using test word Ø.23146314. These tests are repeated four times at each address, with any failing bit positions being marked in the test results. For example, if the first word of raw data equals Ø.00002400, it indicates that bits 8 and 10 failed at least one of the 512 tests performed by this series. If no failures are detected in the 23 bits of data, the 24th bit is checked for any parity failure. This bit is the PFC FF in CC buffer bus B8SESA.

- 2. H-half addresses Ø.4400 through Ø.4477 are tested by the same methods used in test word 1.

- 3. G-half addresses Ø.0000 through Ø.0077 are tested identically to test word 1.

- 4. G-half addresses Ø.4400 through Ø.4477 are tested identically to test word 1.

**<sup>4.46</sup>** The tests which are used to derive each of the nine test result words are as follows:

## TABLE F

## PRIMARY HARDWARE TESTED BY PHASE 3 AND PHASE 7

| FS IN<br>SD-1A124 | DESCRIPTION                                           |

|-------------------|-------------------------------------------------------|

| 7                 | X servo three cell FF binary counter                  |

| 7                 | Logic stepping circuitry to X servo<br>binary counter |

| 6                 | Y servo three cell FF binary counter                  |

| 6                 | Logic stepping circuitry to Y servo binary counter    |

| 19                | Control read servos gating                            |

| 6, 7              | Control read servos readout<br>circuitry              |

| 19                | Control write set servos                              |

| 19                | Control write reset servos                            |

| 24                | Normal and MTCE order servos<br>enable                |

5. The 64 addresses shown below are tested in the H-half of CS. Each address is tested four times, with the same test words used in test one. 6. This test is the same as test word 5, but with the addresses listed below.

| TEST<br>DATA BITS | TEST ADDRESSES              | TEST<br>DATA BITS | TEST ADDRESSES              |

|-------------------|-----------------------------|-------------------|-----------------------------|

| 0                 | 0000 1010 2020 3030         | 0                 | 0077 1067 2057 3047         |

| 1                 | 4040 5050 6060 7070         | 1                 | 4037 5027 6017 7007         |

| 2                 | $0101 \ 1111 \ 2121 \ 3131$ | 2                 | $0176 \ 1166 \ 2156 \ 3146$ |

| 3                 | 4141 5151 6161 7171         | 3                 | 4136 $5126$ $6116$ $7106$   |

| 4                 | 0202 1212 2222 3232         | 4                 | $0275 \ 1265 \ 2255 \ 3245$ |

| 5                 | 4242 5252 6262 7272         | 5                 | 4235 $5225$ $6215$ $7205$   |

| 6                 | 0303 1313 2323 3333         | 6                 | 0374 1 <b>364</b> 2354 3344 |

| 7                 | 4343 5353 6363 7373         | 7                 | $4334 \ 5324 \ 6314 \ 7304$ |

| 8                 | 0404 1414 2424 3434         | 8                 | 0473 $1463$ $2453$ $3443$   |

| 9                 | $4444 \ 5454 \ 6464 \ 7474$ | 9                 | 4433 $5423$ $6413$ $7403$   |

| 10                | 0505 1515 2525 3535         | 10                | 0572 1562 2557 3542         |

| 11                | 4545 5555 6565 7575         | 11                | 4532 $5522$ $6512$ $7502$   |

| 12                | 0606 1616 2626 3636         | 12                | 0671 1661 2651 3641         |

| 13                | 4646 5656 6666 7676         | 13                | 4631 5621 6611 7601         |

| 14                | 0707 1717 2727 3737         | 14                | 0770 1760 2750 3740         |

| 15                | 4747 5757 6767 7777         | 15                | 4730 5720 6710 7700         |

- 7. G-half addresses are tested using the same procedures and test addresses listed in test word 5.

- 8. G-half addresses are tested using the same procedures and test addresses listed in test word 6.

- 9. Routing of both the H- and G-half of CS to the active bus is tested. This includes both sending and inhibiting CS readouts.

4.47 Failures in either phase 4 or phase 8 have to be considered in conjunction with any failures that may have been indicated in phase 3 or phase 7. This is necessary because of the relationship between the servo system and the X and Y current drives. A circuitry failure in phase

3 or phase 7 can result in meaningless data being received for phase 4 or phase 8, or vice versa. The primary hardware tested by phase 4 and phase 8 is shown in Table G.

4.48 For offices with CTX-6 Issue 8 and later generic except CTX-8, Issues 2.1 and 2.2, phases 4 and 8 have a test to detect interference on the CS answer bus. This test is run only if all previous tests have passed.

The raw data is stored in the last raw data word for phase 4 or phase 8. The raw data pattern for bits 0 through 22 will have a 1 in the bit position corresponding to the interfering bit on the A74 circuit board. No new trouble number will be produced. See Table H for pack location and corresponding raw data values.

#### TABLE G

#### PRIMARY HARDWARE TESTED BY PHASE 4 AND PHASE 8

| FS IN<br>SD-1A124 | DESCRIPTION                                 |

|-------------------|---------------------------------------------|

| 1                 | Preamplifiers                               |

| 2                 | Discriminators                              |

| $2,\!24$          | Associated discr logic                      |

| 3                 | H and G inhibit generators                  |

| 24                | Associated inhibit gen logic                |

| 25                | Regenerate gates in data reg                |

| 27                | Normal and MTCE mode SPO (bus 0<br>outputs) |

| 4,5               | H and G diode matrices                      |

| 6,7               | H and G input markers                       |

| 6,7               | H and G output markers                      |

| 6,7               | H and G ac switches                         |

| 6,7               | X and Y access current drivers,             |

|                   | cur driver trnsf, std sig ref<br>SR3        |

| 23                | H and G normal mode answer bus              |

| 04.04             | routing onto output bus 0                   |

| 24,34             | Discr strobes STB0-P', STBE-P',<br>STB2-P   |

| 18                | Data reg logic gates WDC1', WDC2'           |

#### Example of Phase 4 or Phase 8 Failure

**4.49** The following is an example of a phase 4 or phase 8 failure, with possible ways for finding the fault.

## 23 MA14A 00000000 01630164 01024345 01152306 01152726 00000000

\*\*23 MA14 CC INT 00506605 11051105 00014273 01074556 00506605 0000000 00012317 00506632 17777777 00506605 00506405 01051105 00010510 00014273 0000000 12201401 00010550 00002010

\*\*24 DR01 TBL NOS CS 3 PH 4 STF 5276 6940 6650 PH 8 STF 1614 7132 6793 UNIV TBL NO. 6891 7151 6098

**4.50** From these messages, the following can be determined.

**4.51** The TLM approach yields no match, so the next step is to request a cell data printout as follows:

#### CS-DGN-CCS03.PF

(1) The failing instruction

(2) The failing CS address

(3) The configuration of CS, CS buses, and CSs in effect at the time of the failure.

#### SECTION 231-006-305

**4.52** The cell data does not yield a match, so in this case it cannot be used. The next step would be to request a raw data diagnostic as follows:

**4.54** The DR02 analysis, using the PK approach, shows that the following conditions exist.

CS-DGN-RCS03.PF

1614 7132 6793 UNIV TBL NO. 6891 7151 6098

**4.53** The following procedure is used to analyze the raw data and locate the fault. It should be noted that several documents are used in analyzing the failure.

(1) Word 1 failed bits 15, 13, 11, 09, 07, 05, 03, and 01 at one time or another in the first 100 (octal) H-half locations (name +0000) through name +7777).

(2) Word 2 failed in the same manner as word 1, H-locations 4400 through 4477.

(3) Words 3 and 4 failed with the same results in G-half as failed in H-half.

(4) Phase 8 failed the same as phase 4.

4.55 The conclusions reached at this point are

(1) The fault is not bus-sensitive. Any circuitry assosciated with only one bus should be OK.

(2) The fault is not G- or H-half sensitive (affects both G- and H-half the same). Any circuitry associated with only the H-half or only the G-half should be OK.

(3) Only odd-numbered bits 15 through 01 failed. The fault appears to be a bit-associated

trouble; but it is not yet possible to tell if the failure is on a write or the subsequent read, or whether it is in the accessing, writing, or readout circuits.

| _         |           | _         |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |           |      |                       |    | _             |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------|-----------------------|----|---------------|

| 23        | 22        | 21        | 20        | 19        | 18        | 17        | 16        | 15        | 14        | 13        | 12        | 11        | 10        | 9         | 8         | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         | C.P. | FUNCTION              | FS | ]             |

| _         |           | 34-       | -40       |           |           |           |           | 34-       | -39       |           |           |           |           | 34-       | -38       |           |           |           |           | 34        | -45       |           |           | A18  | CA. RCV. BUS 0        | 11 | BU            |

| _         |           | 34-       | -48       |           |           |           |           | 34-       | -47       |           |           |           |           | 34-       | -46       |           | _         |           |           | 34-       | -37       |           |           | A18  | CA. RCV. BUS 1        | 11 | S             |

|           |           | 28-       | -24       |           |           |           |           | 28        | -20       |           |           |           |           | 28-       | -16       |           |           |           |           | 28-       | -14       |           |           | A72  | PULSE DIR. BUS-0      | 15 | - S<br>E<br>N |

|           |           | 28-       | -26       |           |           |           |           | 28-       | -22       |           |           |           |           | 28-       | -18       |           |           |           |           | 28-       | -12       |           |           | A72  | PULSE DIR. BUS-1      | 15 |               |

|           |           |           |           | .32-      | -24       |           |           | 32-       | -20       |           |           |           |           | 32-       | -16       |           |           |           |           | 32-       | -14       |           |           | A72  | PULSE DIR. BUS-0      | 15 |               |

|           |           |           |           | 32-       | -26       |           |           | 32-       | -22       |           |           |           |           | 32-       | -18       |           |           |           |           | 32-       | -12       |           |           | A72  | PULSE DIR. BUS-1      | 15 | ΪE.           |

|           |           |           | 32-<br>36 | 24-<br>48 | 24-       | 47        | 24-<br>46 |           | 26-       | -32       |           |           | 26-       | -31       |           |           | 26-       | -30       |           |           | 26-       | -29       |           | A06  | CONTROL WRITE GATES   | 25 |               |

| 24-<br>48 | 24-<br>47 | 24-<br>46 | 24-<br>45 | 24-<br>40 | 24-<br>39 | 24-<br>38 | 24-<br>37 | 24-<br>32 | 24-<br>31 | 24-<br>30 | 24-<br>29 | 24-<br>24 | 24-<br>23 | 24-<br>22 | 24-<br>21 | 24-<br>16 | 24-<br>15 | 24-<br>14 | 24-<br>13 | 24-<br>08 | 24-<br>07 | 24-<br>06 | 24-<br>05 | A06  | DATA REGISTER         | 25 |               |

| 06-<br>30 | 21-<br>30 | 06-<br>26 | 21-<br>26 | 06-<br>24 | 21-<br>24 | 06-<br>20 | 21-<br>20 | 06-<br>18 | 19-<br>30 | 06-<br>14 | 19-<br>26 | 04-<br>30 | 19-<br>24 | 04-<br>26 | 19-<br>20 | 04-<br>24 | 17-<br>30 | 04-<br>20 | 17-<br>26 | 04-<br>18 | 17-<br>22 | 04-<br>14 | 17-<br>18 | A89  | READOUT PREAMP        | 01 |               |

| 21-<br>41 | 21-<br>42 | A08  | UNCLAMP GATES         | 02 |               |

|           | 21-<br>28 | 06-<br>28 | 21-<br>28 | 06-<br>22 | 21-<br>22 | 06-<br>22 | 21-<br>22 | 06-<br>16 | 19-<br>28 | 06-<br>16 | 19-<br>28 | 04-<br>28 | 19-<br>22 | 04-<br>28 | 17-<br>28 | 04-<br>22 | 17-<br>28 | 04-<br>22 | 17-<br>28 | 04-<br>16 | 17-<br>20 | 04-<br>16 | 17-<br>20 | A90  | DISCR                 | 02 |               |

| 17—       | 48        | 19-       | -46       | 17-       | -46       | 19-       | -44       | 17-       | -44       | 19-       | -42       | 17-       | -42       | 19-       | -40       | 17-       | -40       | 19-       | -38       | 17-       | -38       | 19-       | -36       | A96  | H. INHIBIT GEN.       | 03 | 1             |

| 06—       | 46        | 04-       | -44       | 06-       | -44       | 04-       | -42       | 06-       | -42       | 04-       | -40       | 06-       | -40       | 04-       | -38       | 06-       | -38       | 04-       | -36       | 06-       | -36       | 06-       | -34       | A96  | G. INHIBIT GEN.       | 03 | 1.            |

|           | 24-       | -42       |           |           | 24-       | -34       |           |           | 24-       | -26       |           |           | 24-       | -18       |           |           | 24-       | -10       |           |           | 24-       | -02       |           | A74  | SENS. PULS. ORIG. B-0 | 27 |               |

|           | 24-       | -44       |           |           | 24-       | -36       |           |           | 24-       | -28       |           |           | 24-       | -20       |           |           | 24-       | -12       |           |           | 24-       | -04       |           | A74  | SENS. PULS. ORIG. B-1 | 27 | B             |

|           |           |           | 26-       | -44       |           |           |           |           |           |           | 26-       | -40       |           |           |           |           |           |           | 26-       | -36       |           |           |           | A21  | C.D. BUS 0            | 27 | Ī             |

|           |           |           | 26-       | -46       |           |           |           |           |           | ·         | 26-       | -42       |           |           |           |           |           |           | 26-       | -38       |           |           | Ì         | A21  | C.D. BUS 1            | 27 | 1             |

BIT POSITION

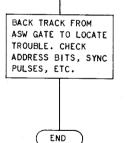

Fig. 6—Data Sensitive Troubleshooting Aid

ISS 2, SECTION 231-006-305

Page 25

4.56 One method for finding the fault is to use the ØFL-EXEC-09 message and the failing address from the D-level interrupt. Refer to Section 231-117-301 for 2-wire and Section 231-417-301 for 4-wire for off-line procedures.

**4.57** This method is a write order, but the CS performs a readout/write-in operation. This will allow observing a readout fault in action even though the store is receiving only *write* commands from CC.

**4.58** The scope sync should be on the sync 1 input (SD-1A019) to the CS and the probing should start at the readout circuits and work backwards towards the ferrite module.

4.59 Compare a good bit (bit 00) with a bad one having the same value (bit 01) on the 2 scope channels. It will be found in this fault where address bit X5 does not equal address bit Y5 that bit 01 never gets its unclamp signal for address. Gate UCB4-P' on sheet B26 in SD-1A019 has 2 highs on its inputs and one high on its output; also, the output should be low. This circuit pack is an A8 in location 21-41.

**4.60** Another method for locating a fault of this type is to use the bit sensitive trouble-shooting aid shown in Fig. 6. Using the failing word in the phase 4/8 raw data printout, convert the octal number to binary. Put this data into the bit position on the chart. The only pack common to all the odd failing bits and none of the even bits is the **Unclamp Gates**, an A8 circuit pack at location 21-41.

4.61 Since it is known that the fault is not bus-sensitive, the circuit packs listed on the first six lines and the last four lines are ruled out. It could also possibly be more than the discriminator circuit pack (A90). It could not be the A96 inhibit generators since the trouble is common to both H- and G-halves.

#### Phase 9 and Phase 10 (CTX-6, Issue 8)

**4.62** For offices with CTX-6 Issue 8 and later generics except CTX-8, Issues 2.1 and 2.2,

phases 9 and 10 detect access rate dependent faults in CC or XP call stores. This functional access test run over BUS 0 (phase 9) and BUS 1 (phase 10), is primarily directed at faults in the CS timing chain and bus lockout circuitry. Depending upon the complex, either the CC or SP will be used to verify that the CS under diagnosis can be accessed at a 5.5 microsecond rate without CS errors re-read failures.

4.63 Because these tests are functional rather than diagnostic in nature, there is no meaningful raw data produced by phases 9 and 10. A test failure causes a constant raw data word (37777777) to be generated and a TLM# of 6308 6364 4264 (PH9) or 2189 6096 3575 (PH10) to be produced. Phases 9 and 10 are run only if all other tests pass.

**4.64** When phases 9 or 10 fails, the faulty circuit pack can be isolated by looping on phase 9 or 10 and checking the outputs of the delay generator circuit packs with an oscilloscope. The location of these packs and their normal output pulse width are given in Table I.

#### 5. CHECKERBOARD TEST

5.01 This test consists of multiple write-read operations at each CS address. Basically, this test walks a 1 or 0 through a field of opposite bits, and extensively exercises the CS circuitry to detect noise problems. However, when this test is requested, all checks are made over the presently active CS bus. The full value of this test can only be realized if it is run over both buses. Therefore, once a checkerboard test has been run over one bus, switch the active CS bus and request a new checkerboard test.

7 2.0

2.0

2.7

2.95

XRE 0.5

1.0

XRL

XWE

XWL

|      | CURRENT DRIVER CIRCUITS |         |               |              |             |      |  |  |

|------|-------------------------|---------|---------------|--------------|-------------|------|--|--|

|      |                         | CURRENT | AUX CURRENT   | STANDARD SIG |             |      |  |  |

|      | IN LEAD                 | DRIVER  | DRIVER (A130) | TIMING (B36) | SERVO (B41) | ES   |  |  |

|      |                         | DESIG   | LOC 17-14     | LOC 17-24    | LOC 14-16   |      |  |  |

|      | XRE                     | CD3     |               | SRI          | SR3         | B4 I |  |  |

|      | XRL                     | CD4     | XAUX          | SRI          | SR3         | 841  |  |  |

| 3.95 | XWE                     | CD3     |               | SRI          | SR3         | B4 I |  |  |

| 3.95 | XWL                     | CD4     | XUAX          | SRI          | SR3         | B4 I |  |  |

# ۵ CALL STORE SELECTIONS IN G-HALF X MATRIX (SEE NOTE 2)

#### ISS 1, SECTION 231-006-305

NOTES:

- I. K-CODES AND OCTAL NUMBERS DEFINED BY

- BITS AIT-AIZ ARE SHOWN ON SHEET D25.

- 2. CHOOSE THE ADDRESS STATES. THEN FOLLOW THE ARROWS TO THE MATRIX INTERSECTION.

Fig. 7—Matrix Access Aid

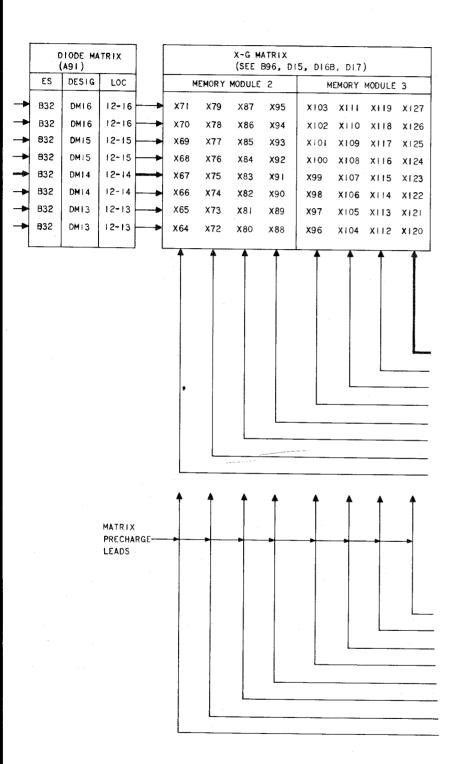

5.02 Use the address that failed in CS03 printout to access sheets D21 through D24 in SD-1A124to determine access circuits that failed. See the example below and in Fig. 7. Use bits that failed to determine readout circuit packs that failed.

CS03 CHKBD CC 3

| 00007330 | 0000001               |

|----------|-----------------------|

| 00007323 | 0000001               |

| 00007152 | 00000001              |

| 00007142 | 00000200 Bit 1 Failed |

| 00007142 | 00000400              |

| 00007020 | 0000001               |

| 00006774 | 0000001               |

| 00006752 | 0000001               |

| 00006647 | 0000001               |

| 00006611 | 0000001               |

| 00006375 | 0000001               |

| 00005372 | 0000001               |

| 00005113 | 0000001               |

| 00004521 | 0000001               |

| 00002462 | 0000001               |

| 00001403 | 0000001               |

| 00007137 | 0000000               |

| 00004157 | 0000000               |

$$-Bit 15 = 0 = G-Half$$

**5.03** The printout should be analyzed to determine the possible trouble; for example, more than one bit failing might be a voltage pack, or bits failing next to each other might be a readout pack.

ARO = B REG OF STANDBY CC DRO = PA ADDRESS AT TIME OF INTERRUPT

DRI = FAILING CALL STORE ADDRESS

CSEI = ERROR INDICATORS

#### Fig. 8—D-Level Interrupt Register Locations

#### DATA=ADDRESS

5.04 For offices with CTX 6 Issue 8 and later generics except CTX-8, Issues 2.1 and 2.2, a demand exercise has been added to verify CS memory integrity. This test is done by initialzing and then verifying every word in the call store under test with DATA=ADDRESS and DATA=ADDRESS complemented test patterns. This test can be requested via the CS partial diagnostic message. This test can be used with the checkerbord test to locate faults.

#### 6. D-LEVEL INTERRUPTS

6.01 A D-level maintenance interrupt occurs when a reread or rewrite failure of a CS word is encountered or an invalid transfer to a CS address rather than to a PS address. When one of these failures is detected and the interrupt request is made by the system, the address that the failure occurred at is saved in the CC match registers.

6.02 The system prints out the MA14 registers for D-level interrupts as shown in Fig. 8. This layout shows the following registers:

| B register    | Z register                                           |

|---------------|------------------------------------------------------|

| ASR register  | L register                                           |

| F register    | addend K register                                    |

| J register    | ARO register (contains the complement of the B reg.) |

| K register    | DRO register (contains the interrupted PS address)   |

| X register    | AR1 register (contains CSTF before the interrupt)    |

| Y register    | DR1 register (contains failing CS address)           |

| MOCR and MACF | register                                             |

SESA register (store error summary FFs)

ILAF register

| BUFFER<br>REGISTER<br>BIT POSITION | NAME OF BIT | COMMENTS                                |

|------------------------------------|-------------|-----------------------------------------|

| 0                                  | AU          | Defines active CC                       |

| 1                                  | TCC         | Marks standby CC in trouble             |

| 2                                  | РВО         |                                         |

| 3                                  | PBA         | PS bus control                          |

| 4                                  | PBT         |                                         |

| 5                                  | СВО         |                                         |

| 6                                  | CBA         | CS bus control                          |

| 7                                  | CBT         |                                         |

| .8                                 | CW          | Control word bus selection              |

| 9                                  | CWC         | Enable standby to receive control words |

PROGRAM STORE AND CALL STORE BUS SELECTION

| PS BUS | РВО                  | РВА | PBT                                   | ACTIV | E CC                       | STANDBY CC |     |  |

|--------|----------------------|-----|---------------------------------------|-------|----------------------------|------------|-----|--|

| CS BUS | СВО                  | СВА | СВТ                                   | SEND  | REC                        | SEND       | REC |  |

|        | 0                    | 0   | 0                                     | 0     | 0                          | 1          | 1   |  |

|        | 0                    | 1   | 0                                     | 1     | 1                          | 0          | 0   |  |

|        | 0                    | 0   | 1                                     | 0     | 0                          | X          | 0   |  |

|        | 0                    | 1   | 1                                     | 1     | 1                          | X          | 1   |  |

|        | 1                    | 0   | 0                                     | 0+1   | 0                          | X          | 1   |  |

|        | 1                    | 1   | 0                                     | 0+1   | 1                          | X          | 0   |  |

|        | 1                    | 0   | 1                                     | 0+1   | 0                          | X          | 0   |  |

|        | 1                    | 1   | 1                                     | 0+1   | 1                          | X          | 1   |  |

|        | = FF Res<br>= FF Set | et  | · · · · · · · · · · · · · · · · · · · |       | 0 = Bu<br>1 = Bu<br>X = Ne |            |     |  |

#### Fig. 9—CSTF Register Layout

6.03 The data contained in the CSTF (Fig. 9), SESA (Fig. 10), and the MOCR/MACF determines the validity of the information contained in the other registers. If (1) CBT (bit 7 of CSTF) is reset and (2) MOCR (Fig. 11) indicates routine matching by having HM, I, and X set (1401 in least significant bits), the parity failure PFC and the ASWC of the active CC and active bus determine the CS at fault. If either PFC or ASWC for the active CS bus is set and the system was in normal configuration before the interrupt occurred, the active CC recognized the problem and the even-numbered CS that contains the address specified in the DR1 register is at fault. Comparing the B registers of the two CCs (the standby CC B registers complement is in the ARO) or, depending on the instruction being performed at the time of the interrupt, the active B register and the data or the complement of the standby B register should produce the bit in error. It is the bit that disagrees in the active register. If no mismatch is present and PFC is set, the parity bit (bit 23) is at fault. (Check instruction for possible masking.) If, under the same condition of CSTF and MOCR, SESA does not have PFC or ASWC set, the failing address belongs to an odd-numbered CS. Since the standby CC recognized the mismatch, the standby B register (ARO) should contain the failing bit. If there is no mismatch, parity bit 23 is the fault.

6.04 In the case where the CSTF CBT bit is set, both CCs receive from the active bus. The

failing address given in the DR1 register would belong to the H-half of the CS specified. The B register and the ARO register would not indicate the bit in error.

**6.05** The signal processor (SP) CSs in the normally

functioning office are configured in the same manner as the CC CSs. This means that the even-numbered CSs are on the active bus. The active CC CS bus and the SP CS bus do not have to be the same. For D-level interrupts that indicate an SP CS address in the DR1 register of the MA14 message, the same conditions apply that were previously explained with the following exceptions. D-level interrupts on write into SP CS implies that the SP saw the failure and not the SP CS. It would imply that the SP CS saw the failure on a read. If the SP CS failure is on a write, the system will generate an F-level interrupt.

6.06 In some cases, bit 11 of ILAF register is set on an interrupt, indicating an internal

| BUFFER REGISTER<br>BIT POSITION | NAME OF BIT                                            | COMMENTS                      |                                                                    |  |  |  |  |

|---------------------------------|--------------------------------------------------------|-------------------------------|--------------------------------------------------------------------|--|--|--|--|

| 0                               | ASWPF-0                                                | ASW failure from<br>PS Bus 0  | PS error summary flip-<br>flops have inputs from                   |  |  |  |  |

| 1                               | ASWPF-1                                                | ASW failure from<br>PS Bus 1  | error detection and cor-<br>rection circuits — gated               |  |  |  |  |

| 2                               | ADEF                                                   | Address Error                 | on interrupt request<br>or on maintenance                          |  |  |  |  |

| 3                               | DBEF                                                   | Double Error                  | orders                                                             |  |  |  |  |

| 4                               | PF                                                     | Single Error                  |                                                                    |  |  |  |  |

| 5                               | ASWC-0                                                 | ASW failure from<br>CS Bus 0  |                                                                    |  |  |  |  |

| 6                               | ASWC-1                                                 | ASW failure from<br>CS Bus 1  | Call store summary<br>group, inputs controlled<br>similar to above |  |  |  |  |

| 7                               | PFC Parity failure of<br>CS word at buffer<br>register |                               |                                                                    |  |  |  |  |

| 8                               | X23—1                                                  | Bit 24 of Kaddend<br>register |                                                                    |  |  |  |  |

Fig. 10—SESA Register Layout

| BUFFER<br>REGISTER<br>BIT<br>POSITION | NAME OF BIT | ACCESS<br>(SEE NOTE) |   |   |                                               |                                       |

|---------------------------------------|-------------|----------------------|---|---|-----------------------------------------------|---------------------------------------|

|                                       |             | R                    | w | с | COMMENTS                                      | LOCATION IN SD                        |

| 00                                    | X           | X                    | X | X |                                               | · · · · · · · · · · · · · · · · · · · |

| 01                                    | Y           | X                    | X | X |                                               |                                       |

| 02                                    | MS          | X                    | X | x |                                               | i                                     |

| 03                                    | TD          | X                    | X | X |                                               |                                       |

| 04                                    | СВ          | X                    | X |   | These bits establish matching mode            |                                       |

| 05                                    | PB          | X                    | x | X |                                               | FS 85<br>Maintenance                  |

| 06                                    | TR          | X                    |   | X |                                               | Control<br>System M                   |

| 07                                    | IC          | X                    | X | X |                                               |                                       |

| 08                                    | . I .       | Х                    | X | X | Interrupt on abnormality                      |                                       |

| 09                                    | HM          | X                    | X | X | Stop match on abnormality                     |                                       |

| 10                                    | Е           | X                    | x | X | Stop standby with execute-stop on abnormality |                                       |

| 11                                    | F           | X                    | X | x | Stop standby with fast-stop on abnormality    |                                       |

*Note:* R — Bit position can be read with read-memory orders.

W — Bit position can be written into with write-memory orders.

C - Bit position can be written into with control-write orders.

#### Fig. 11-MOCR Register Layout

CS failure (CSFI). This means the CC suspected an error on the storage of the registers in the interrupt bins. The printout may or may not contain valid information and should be analyzed carefully.

- **6.07** To analyze a D-level maintenance interrupt printout, use the following procedure.

- Determine the matching mode of the CCs by examining the MOCR. This register should indicate routine matching with interrupts in effect at the time of interrupt. (The four

rightmost octal digits printed out in MOCR should be Ø.1401.)

(2) Determine the status of the send bus (CBO, bit 5), the bus that is active (CBA, bit 6), and the status of the standby bus (CBT, bit 7), using CSTF in the MA14 printout. Bus information can also be obtained from CSEI (Table J).

(3) Determine if the active CC recognized the problem by examining the status of PFC (parity bit 7) bit in SESA register.

## TABLE H

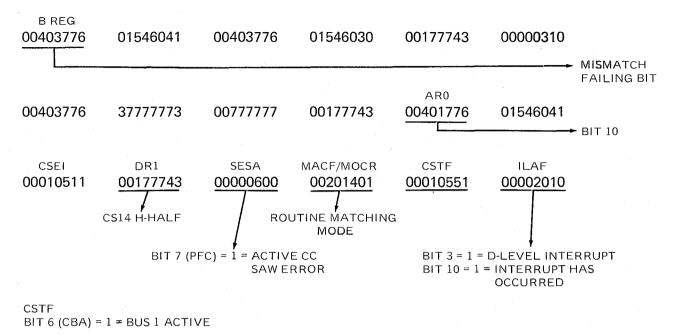

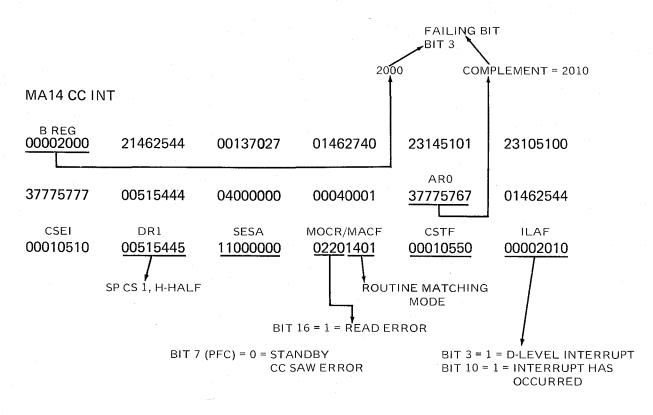

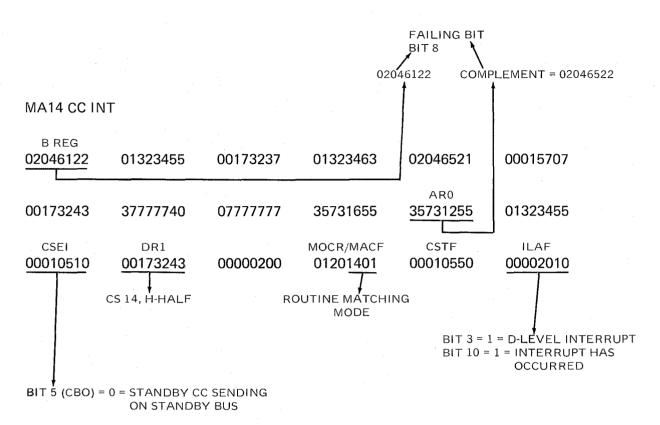

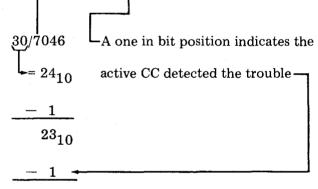

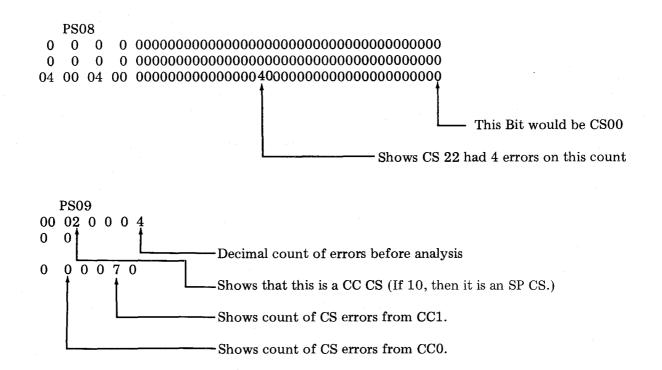

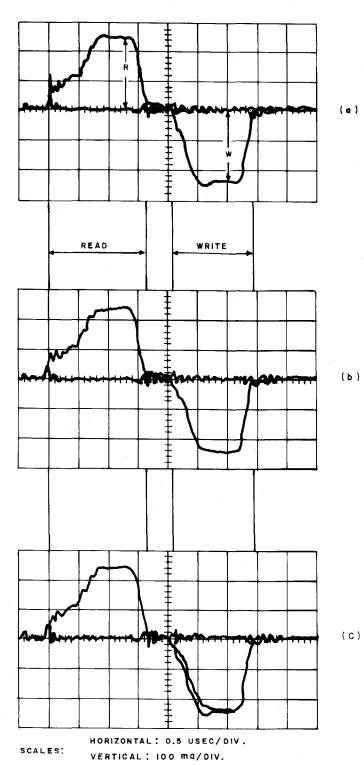

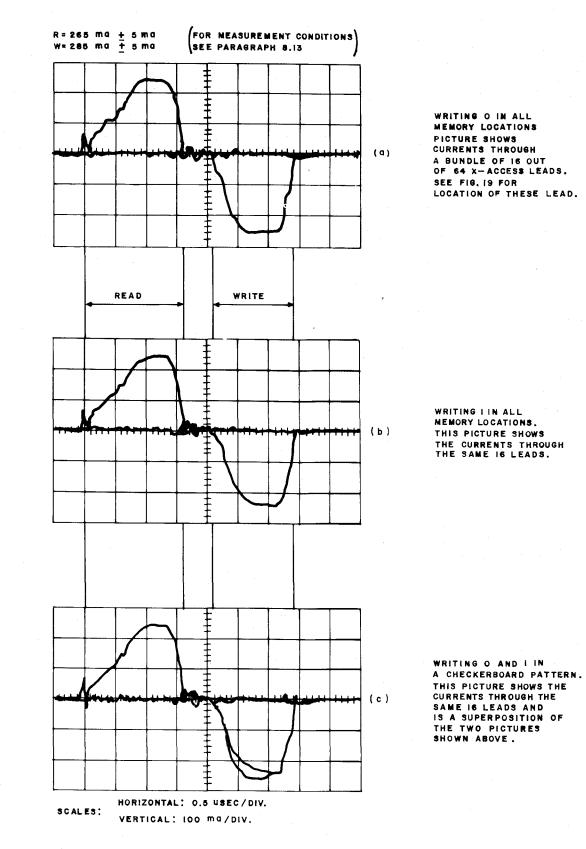

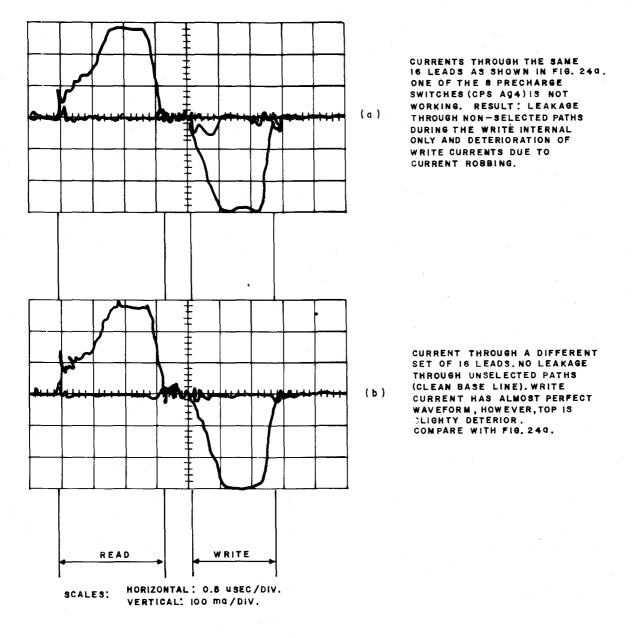

| PHASES 4 AND 8 INTERFERENCE T | TEST BIT FAILURES |