# **DS1283** Watchdog Timekeeper Chip

#### **FEATURES**

- Keeps track of hundredths of seconds, seconds, minutes, hours, days, date of the month, months, and years; valid leap year compersation up to 2100

- Watchdog timer restarts an out-of-control processor

- Alarm function provides notice of real time related occurrences

- Designed for battery operation

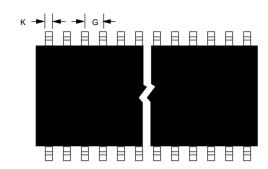

- Programmable interrupts and square wave outputs maintain 28-pin JEDEC footprint

- All registers are individually addressable via the address and data bus

- Accuracy is better than ±2 minutes/month at 25°C

- 50 bytes of user nonvolatile RAM

- Optional 28-pin SOIC surface mount package

- $\bullet$  Low–power CMOS circuitry is maintained on less than 1  $\mu A$  in standby mode

- Optional industrial temperature range -40°C to +85°C

### **DESCRIPTION**

The DS1283 Watchdog Timekeeper Chip is a self–contained real time clock, alarm, watchdog timer, and interval timer in a 28–pin JEDEC DIP or 28–pin SOIC surface mount package. The DS1283 is specifically designed to maintain internal operations from a single low voltage supply. In fact, the only two external components required by the DS1283 are a battery and crystal. For a complete description of operating conditions, electrical characteristics, bus timing, and pin descriptions other than X1, X2,  $V_{\rm BAT},\,V_{\rm CC},\,\overline{\rm RCLR},\,\overline{\rm INTB},$  and  $\overline{\rm INTP}$  see the DS1286 Watchdog Timekeeper data sheet.

#### **PIN ASSIGNMENT**

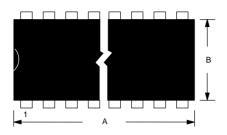

DS1283 28-PIN DIP (600 MIL)

DS1283S 28-PIN SOIC (330 MIL)

NOTE: Pin 4 must be left disconnected.

#### **PIN DESCRIPTION**

| FIN DESCRIPTION |                  |     |                                           |  |  |

|-----------------|------------------|-----|-------------------------------------------|--|--|

| PIN#            | NAME             | I/O | DESCRIPTION                               |  |  |

| 1               | ĪNTA             | 0   | Interrupt Output A (open drain)           |  |  |

| 2–3             | X1,X2            | I   | 32.768 KHz Crystal                        |  |  |

| 4               | NC               | -   | No Connection                             |  |  |

| 5-10            | A0-A5            | I   | Address Inputs:<br>A5=Pin 5;<br>A0=Pin 10 |  |  |

| 11              | DQ0              | I/O | Data Input/Output                         |  |  |

| 12              | DQ1              | I/O | Data Input/Output                         |  |  |

| 13              | DQ2              | I/O | Data Input/Output                         |  |  |

| 14              | GND              | _   | Ground                                    |  |  |

| 15              | DQ3              | I/O | Data Input/Output                         |  |  |

| 16              | DQ4              | I/O | Data Input/Output                         |  |  |

| 17              | DQ5              | I/O | Data Input/Output                         |  |  |

| 18              | DQ6              | I/O | Data Input/Output                         |  |  |

| 19              | DQ7              | I/O | Data Input/Output                         |  |  |

| 20              | CE               | I   | Chip Enable                               |  |  |

| 21              | ĪNTP             | 0   | Interrupt Output P<br>(open drain)        |  |  |

| 22              | ŌĒ               | I   | Output Enable                             |  |  |

| 23              | SQW              | 0   | Square Wave Output                        |  |  |

| 24              | RCLR             | I   | RAM Clear                                 |  |  |

| 25              | V <sub>BAT</sub> | ı   | Battery Input                             |  |  |

| 26              | INTB<br>(INTB)   | 0   | Interrupt Output B (open drain)           |  |  |

| 27              | WE               | I   | Write Enable                              |  |  |

| 28              | V <sub>CC</sub>  | I   | V <sub>CC</sub> Input                     |  |  |

## **PIN DESCRIPTIONS**

**X1, X2** – Connections for a standard 32.768 KHz quartz crystal. The internal oscillator circuitry is designed for operation with a crystal having a load capacitance ( $C_L$ ) of 6 pF. The crystal is connected directly to the X1 and X2 pins. There is no need for external capacitors or resistors. For more information on crystal selection and

crystal layout considerations, please consult Application Note 58, "Crystal Considerations with Dallas Real Time Clocks."

VBAT, VCC - Inputs for batteries or power supplies between 5.5 and 2.5 volts. The V<sub>CC</sub> supply voltage should never exceed  $V_{BAT}$  + 0.3 volts. The  $V_{BAT}$  input is used to maintain all internal functions while the  $V_{CC}$ input is used to keep all inputs and outputs functional. Therefore, to keep the device fully functional, V<sub>BAT</sub> and V<sub>CC</sub> must be at the same voltage potential. As long as the supply voltages are between 4.5 and 5.5 volts, the timing and the input/output levels are guaranteed. In this mode, the active current drain is 2 mA (CE=V<sub>II</sub>) and the standby current drain is 0.5 mA (CE=VIH). Data retention mode occurs when the VBAT supply is between 5.5 and 2.5 volts and the V<sub>CC</sub> supply is grounded. In the data retention mode the current drain is less than 1 µA maximum at 5.5 volts (CE=V<sub>BAT</sub>-0.2 volts). The current drain specifications are stated with all outputs unloaded.

RCLR – The RCLR pin is used to clear (set to logic 1) all 50 bytes of user nonvolatile RAM but does not affect the registers involved with time, alarm, and watchdog functions. In order to clear the RAM, RCLR must be forced to an input logic 0 (–0.3 to +0.8 volts). The RCLR function is designed to be used via human interface (shorting to ground manually or by switch) and not to be driven with external buffers. This pin is internally pulled up and should be left floating when not in use.

$\overline{\text{INTB}}$  – Interrupt B on the DS1283 operates identical to interrupt B on the DS1286 except that the sink and source current is limited to 500  $\mu\text{A}$ . This pin should be pulled up or down if not used.

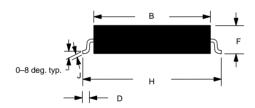

INTP – Interrupt P on the DS1283 was a missing or no connection pin on the DS1286. This interrupt works in the same manner as INTA as programmed by the IPSW bit. However, INTP is also logically ORed with the MSB of the date register (see Figure 1). This bit is called the INP bit on the DS1283 and is forced to zero on the DS1286. When the INP bit (interrupt P bit) is set to logical one, interrupt P will be held active low. When INP is set to logical zero, INTP is always at the same logic state as INTA. This pin is an open drain capable of sinking 4 mA.

# **DS1283 WATCHDOG TIMEKEEPER REGISTERS** Figure 1

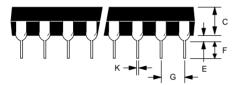

# **DS1283 28-PIN DIP**

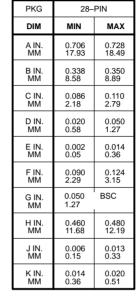

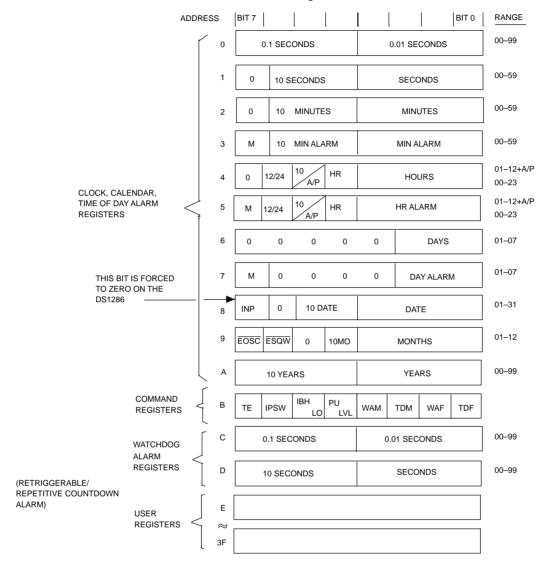

| PKG         | 28-PIN |       |  |

|-------------|--------|-------|--|

| DIM         | MIN    | MAX   |  |

| A IN.<br>MM | 1.445  | 1.470 |  |

| B IN.<br>MM | 0.530  | 0.550 |  |

| C IN.<br>MM | 0.140  | 0.160 |  |

| D IN.<br>MM | 0.600  | 0.625 |  |

| E IN.<br>MM | 0.015  | 0.040 |  |

| F IN.<br>MM | 0.120  | 0.145 |  |

| G IN.<br>MM | 0.090  | 0.110 |  |

| H IN.<br>MM | 0.625  | 0.675 |  |

| J IN.<br>MM | 0.008  | 0.012 |  |

| K IN.<br>MM | 0.015  | 0.022 |  |

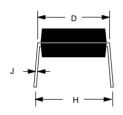

## **DS1283 28-PIN SOIC**