# **DS1602** Elapsed Time Counter

### **FEATURES**

- Two 32-bit counters keep track of real time and elapsed time

- Counters keep track of seconds for over 125 years

- Battery powered counter counts seconds from the time battery is attached until V<sub>BAT</sub> is less than 2.5 volts

- V<sub>CC</sub> powered counter counts seconds while V<sub>CC</sub> is above 4.25 volts and retains the count in the absence of V<sub>CC</sub> under battery backup power

- Clear function resets selected counter to zero

- Read/Write serial port affords low pin count

- Maximum current drain of less than 1 μA from V<sub>BAT</sub> pin when serial port is disabled

- One byte protocol defines read/write, counter address and software clear function

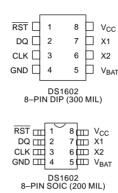

- 8-pin DIP or optional 8-pin SOIC

- Operating temperature range of -40°C to +85°C

- Reduced performance operation down to V<sub>CC</sub> = 2.5V

### **PIN ASSIGNMENT**

### **PIN DESCRIPTION**

| RST       | <ul><li>Reset</li></ul>               |

|-----------|---------------------------------------|

| CLK       | <ul><li>Clock</li></ul>               |

| DQ        | <ul> <li>Data input/output</li> </ul> |

| GND       | <ul><li>Ground</li></ul>              |

| X1, X2    | <ul> <li>Crystal inputs</li> </ul>    |

| $V_{BAT}$ | <ul> <li>+ Battery input</li> </ul>   |

| $V_{CC}$  | <ul> <li>+5 volts</li> </ul>          |

### **DESCRIPTION**

The DS1602 is a real time clock/elapsed time counter designed to count seconds when  $V_{CC}$  power is applied and continually count seconds under battery backup power with an additional counter regardless of the condition of  $V_{CC}$ . The continuous counter can be used to derive time of day, week, month, and year by using a software algorithm. The  $V_{CC}$  powered counter will automatically record the amount of time that  $V_{CC}$  power is applied. This function is particularly useful in determining the operational time of equipment in which the

DS1602 is used. Alternatively, this counter can also be used under software control to record real time events. Communication to and from the DS1602 takes place via a 3–wire serial port. A one byte protocol selects read/write functions, counter clear functions and oscillator trim. A low cost 32.768 KHz crystal attaches directly to the X1 and X2 pins. If battery powered only operation is desired, the  $V_{BAT}$  pin must be grounded and the  $V_{CC}$  pin must be connected to the battery.

#### **OPERATION**

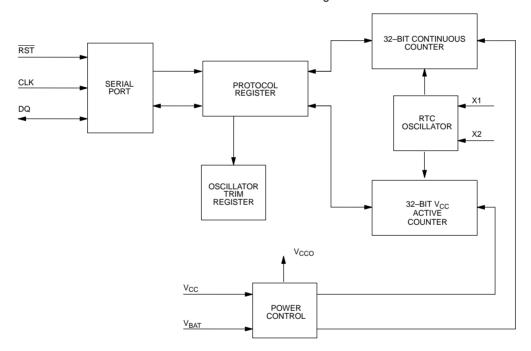

The main elements of the DS1602 are shown in Figure 1. As shown, communications to and from the elapsed time counter occur over a 3-wire serial port. The port is activated by driving RST to a high state. With RST at high level 8 bits are loaded into the protocol shift register providing read/write, register select, register clear, and oscillator trim information. Each bit is serially input on the rising edge of the clock input. After the first eight clock cycles have loaded the protocol register with a valid protocol additional clocks will output data for a read or input data for a write. V<sub>CC</sub> must be present to access the DS1602. If  $V_{CC} < V_{BAT}$  the DS1602 will go into a battery backup mode which disables the serial port to conserve battery capacity. For battery only operations, the V<sub>BAT</sub> pin must be grounded and the V<sub>CC</sub> pin must be connected to the battery. This will keep the DS1602 out of battery backup mode. Battery powered operation down to 2.5V is possible with reduced speed performance on the serial port.

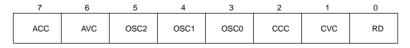

### **PROTOCOL REGISTER**

The protocol bit definition is shown in Figure 2. Valid protocols and the resulting actions are shown in Table 1. Each data transfer to the protocol register designates what action is to occur. As defined, the MSB (bit 7 which is designated ACC) selects the 32-bit continuous counter for access. If ACC is a logical 1 the continuous counter is selected and the 32 clock cycles that follow the protocol will either read or write this counter. If the counter is being read, the contents will be latched into a different register at the end of protocol and the latched contents will be read out on the next 32 clock cycles. This avoids reading garbled data if the counter is clocked by the oscillator during a read. Similarly, if the counter is to be written, the data is buffered in a register and all 32 bits are jammed into the counter simultaneously on the rising edge of the 32nd clock. The next bit (bit 6 which is designated AVC) selects the 32-bit V<sub>CC</sub> active counter for access. If AVC is a logical 1 this counter is selected and the 32 clock cycles that follow will either read or write this counter. If both bit 7 and bit 6 are written to a logic high, all clock cycles beyond the protocol are ignored and bit 5, 4, and 3 are loaded into the oscillator trim register. A value of binary 3 (011) will give a clock accuracy of +120 seconds per month at 25°C. Increasing the binary number towards 7 will cause the real time clock to run faster. Conversely, lowering the binary number towards zero will cause the clock to run slower. Binary 000 will stop the oscillator completely. This feature can be used to conserve battery life during storage. In this mode the IRAT current is reduced to 100 nA maximum. In applications where oscillator trimming is not practical or not needed, a default setting of 011 is recommended. Bit 2 of protocol (designated CCC) is used to clear the continuous counter. When set to logic 1, the continuous counter will reset to zero when RST is taken low. Bit 1 of protocol (designated CVC) is used to clear the V<sub>CC</sub> active counter. When set to logical 1, the  $V_{CC}$  active counter will reset to zero when RST is taken low. Both counters can be reset simultaneously by setting CCC and CVC both to a logical 1. Bit zero of the protocol (designated RD) determines whether the 32 clocks to follow will write a counter or read a counter. When RD is set to a logical 0 a write action will follow when RD is set to a logical 1 a read action will follow. When sending the protocol, eight bits should always be sent. Sending less than 8 bits can produce erroneous results. If clearing the counters or trimming the oscillator, the data transfer can be terminated after the 8-bit protocol is sent. However, when reading or writing the counters, 32 clock cycles should always follow the protocol.

### **RESET AND CLOCK CONTROL**

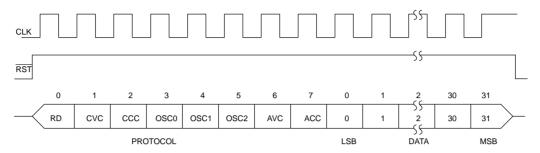

All data transfers are initiated by driving the RST input high. The RST input has two functions. First, RST turns on the serial port logic which allows access to the protocol register for the protocol data entry. Second, the RST signal provides a method of terminating the protocol transfer or the 32-bit counter transfer. A clock cycle is a sequence of a falling edge followed by a rising edge. For write inputs, data must be valid during the rising edge of the clock. Data bits are output on the falling edge of the clock when data is being read. All data transfers terminate if the RST input is transitioned low and the DQ pin goes to a high impedance state. RST should only be transitioned low while the clock is high to avoid disturbing the last bit of data. All data transfers must consist of 8 bits when transferring protocol only or 8 + 32 bits when reading or writing either counter. Data transfer is illustrated in Figure 3.

### **DATA INPUT**

Following the 8-bit protocol that inputs write mode, 32 bits of data are written to the selected counter on the rising edge of the next 32 CLK cycles. After 32 bits have been entered any additional CLK cycles will be ignored until  $\overline{RST}$  is transitioned low to end data transfer and then high again to begin new data transfer.

### **DATA OUTPUT**

Following the eight CLK cycles that input read mode protocol, 32 bits of data will be output from the selected counter on the next 32 CLK cycles. The first data bit to be transmitted from the selected 32–bit counter occurs on the falling edge after the last bit of protocol is written. When transmitting data from the selected 32–bit counter, RST must remain at high level as a transition to low level will terminate data transfer. Data is driven out the DQ pin as long as CLK is low. When CLK is high the DQ pin is tristated.

### **CRYSTAL SELECTION**

A standard 32,768 KHz quartz crystal can be directly connected to the DS1602 via pins 1 and 2 (X1, X2). The

crystal selected for use should have a specified load capacitance ( $C_L$ ) of 6 pF. For more information on crystal selection and crystal layout considerations, please consult Application Note 58, "Crystal Considerations with Dallas Real Time Clocks".

### **BATTERY SELECTION**

The battery selected for use with the DS1602 should have an output voltage between 2.5 and 3.5 volts. A lithium battery of 35 mAh or greater will run the elapsed time counter for over 10 years in the absence of power. Small lithium coin cell batteries produce both the proper output voltage and have the capacity to supply the DS1602 for the useable lifetime of the equipment where they are installed.

### **DS1602 ELAPSED TIME COUNTER BLOCK DIAGRAM** Figure 1

### **PROTOCOL BIT MAP** Figure 2

### VALID PROTOCOLS Table 1

|                                         | PROTOCOL |     |      |      |      |     |     |    |                                                                                                                                                  |

|-----------------------------------------|----------|-----|------|------|------|-----|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| ACTION                                  | ACC      | AVC | OSC2 | OSC1 | OSC0 | ccc | cvc | RD | DESCRIPTION                                                                                                                                      |

| Read Continuous<br>Counter              | 1        | 0   | Х    | х    | х    | Х   | Х   | 1  | Output continuous<br>counter on the 32<br>clocks following proto-<br>col. Oscillator trim<br>register is not updated.<br>Counters are not reset. |

| Write Continuous<br>Counter             | 1        | 0   | Х    | Х    | Х    | Х   | Х   | 0  | Input data to continuous counter on the 32 clocks following protocol. Oscillator trim register is not updated. Counters are not reset.           |

| Read V <sub>CC</sub> Active<br>Counter  | 0        | 1   | X    | X    | X    | Х   | Х   | 1  | Output V <sub>CC</sub> active counter on the 32 clocks following protocol, oscillator trim register is not updated. Counters are not reset.      |

| Write V <sub>CC</sub> Active<br>Counter | 0        | 1   | Х    | Х    | Х    | Х   | Х   | 0  | Input data to continuous counter on the 32 clocks following protocol. Oscillator trim register is not updated. Counters are not reset.           |

| Clear Continuous<br>Counter             | 0        | 0   | Х    | Х    | Х    | 1   | Х   | Х  | Resets the continuous counter to all zeroes at the end of protocol. Oscillator trim register is not updated.                                     |

| Clear V <sub>CC</sub> Active<br>Counter | 0        | 0   | Х    | Х    | Х    | Х   | 1   | X  | Resets the V <sub>CC</sub> active counter to all zeroes at the end of protocol. Oscillator trim register is not updated.                         |

| Set Oscillator Trim Bits                | 1        | 1   | А    | В    | С    | Х   | Х   | 0  | Sets the oscillator trim register to a value of ABC. Counters are unaffected.                                                                    |

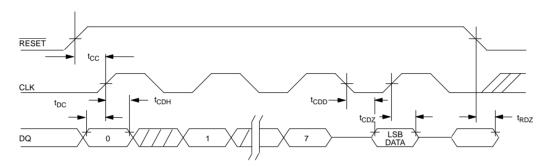

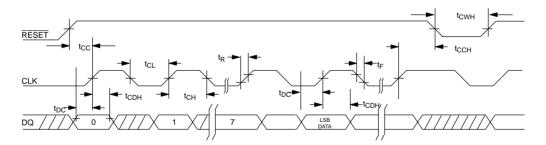

## **DATA TRANSFER** Figure 3

### TIMING DIAGRAM: READ/WRITE DATA TRANSFER

### READ DATA TRANSFER

### WRITE DATA TRANSFER

NOTE:  $t_{CL}$ ,  $t_{CH}$ ,  $t_{R}$ , and  $t_{F}$  apply to both read and write data transfer.

ABSOLUTE MAXIMUM RATINGS\* Voltage on Any Pin Relative to Ground -0.3V to +7.0V Operating Temperature Storage Temperature -40°C to +85°C -55°C to +125°C Soldering Temperature 260°C for 10 seconds

### **RECOMMENDED DC OPERATING CONDITIONS**

(-40°C to +85°C)

| PARAMETER              | SYMBOL           | MIN  | TYP | MAX                  | UNITS | NOTES |

|------------------------|------------------|------|-----|----------------------|-------|-------|

| Supply Voltage         | V <sub>CC</sub>  | 4.5  | 5.0 | 5.5                  | V     | 1     |

| Battery Supply Voltage | V <sub>BAT</sub> | 2.5  | 3.0 | 3.5                  | V     | 1     |

| Logic 1 Input          | V <sub>IH</sub>  | 2.0  |     | V <sub>CC</sub> +0.3 | V     | 1     |

| Logic 0 Input          | V <sub>IL</sub>  | -0.3 |     | 0.8                  | V     | 1     |

### DC ELECTRICAL CHARACTERISTICS

$(-40^{\circ}\text{C to } +85^{\circ}\text{C}; \text{V}_{\text{CC}} = 5\text{V} \pm 10\%)$

| PARAMETER             | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|-----------------------|-------------------|-----|-----|-----|-------|-------|

| Input Leakage         | ILI               | -1  |     | +1  | μΑ    |       |

| I/O Leakage           | I <sub>LO</sub>   | -1  |     | +1  | μΑ    |       |

| Logic 1 Output        | V <sub>OH</sub>   | 2.4 |     |     | V     | 2     |

| Logic 0 Output        | V <sub>OL</sub>   |     |     | 0.4 | V     | 3     |

| Active Supply Current | Icc               |     |     | 1   | mA    | 4     |

| Timekeeping Current   | I <sub>CC1</sub>  |     |     | 50  | μΑ    | 5     |

| Timekeeping Current   | I <sub>BAT</sub>  |     |     | 400 | nA    | 6     |

| Leakage Current       | I <sub>BATL</sub> |     |     | 100 | nA    | 11    |

#### **CAPACITANCE** $(t_A = 25^{\circ}C)$

| PARAMETER           | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|---------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance   | C <sub>I</sub>   |     | 5   |     | pF    |       |

| I/O Capacitance     | C <sub>I/O</sub> |     | 10  |     | pF    |       |

| Crystal Capacitance | C <sub>X</sub>   |     | 6   |     | pF    | 10    |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +5V \pm 10\%, -40^{\circ}C \text{ to } +85^{\circ}C)$

| PARAMETER              | SYMBOL                          | MIN | TYP | MAX | UNITS | NOTES   |

|------------------------|---------------------------------|-----|-----|-----|-------|---------|

| Data to CLK Setup      | t <sub>DC</sub>                 | 50  |     |     | ns    | 7       |

| CLK to Data Hold       | t <sub>CDH</sub>                | 60  |     |     | ns    | 7       |

| CLK to Data Delay      | t <sub>CDD</sub>                |     |     | 200 | ns    | 7, 8, 9 |

| CLK Low Time           | t <sub>CL</sub>                 | 250 |     |     | ns    | 7       |

| CLK High Time          | t <sub>CH</sub>                 | 250 |     |     | ns    | 7       |

| CLK Frequency          | f <sub>CLK</sub>                | DC  |     | 2.0 | MHz   | 7       |

| CLK Rise & Fall        | t <sub>F</sub> , t <sub>R</sub> |     |     | 500 | ns    |         |

| RST to CLK Setup       | t <sub>CC</sub>                 | 100 |     |     | ns    | 7       |

| CLK to RST Hold        | t <sub>CCH</sub>                | 60  |     |     | ns    | 7       |

| RST Inactive Time      | t <sub>CWH</sub>                | 1   |     |     | μs    | 7       |

| RST Low to I/O High Z  | t <sub>RDZ</sub>                |     |     | 70  | ns    | 7       |

| CLK High to I/O High Z | t <sub>CDZ</sub>                |     |     | 20  | ns    | 7       |

### NOTES:

- 1. All voltages are reference to ground.

- 2. Logic one voltages are specified at a source current of 1 mA.

- 3. Logic zero voltages are specified at a sink current of 4 mA.

- 4. I<sub>CC</sub> is specified with the DQ pin open.

- 5.  $I_{CC1}$  is specified with  $V_{CC}$  at 5.0V and  $\overline{RST}$  = GND.

- 6.  $I_{BAT}$  is specified with  $V_{CC} < V_{BAT}$  and  $V_{BAT}$  within DC recommended operating conditions.

- 7. Measured at  $V_{IH} = 2.0V$  or  $V_{IL} = 0.8V$ .

- 8. Measured at  $V_{OH} = 2.4V$  or  $V_{OL} = 0.4V$ .

- 9. Load capacitance = 50 pF.

- 10. Specified as the load capacitance for which the crystal frequency is guaranteed (see crystal manufacturer's data sheet).

- 11. Leakage current is the amount of current consumed from the battery when V<sub>CC</sub> is not present and the oscillator is turned off.

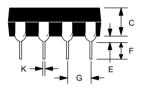

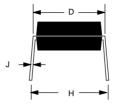

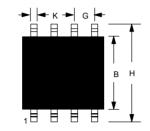

### **DS1602 8-PIN DIP 300 MIL**

| PKG   | 8-P   | IN    |

|-------|-------|-------|

| DIM   | MIN   | MAX   |

| A IN. | 0.360 | 0.400 |

| MM    | 9.14  | 10.16 |

| B IN. | 0.240 | 0.260 |

| MM    | 6.10  | 6.60  |

| C IN. | 0.120 | 0.140 |

| MM    | 3.05  | 3.56  |

| D IN. | 0.300 | 0.325 |

| MM    | 7.62  | 8.26  |

| E IN. | 0.015 | 0.040 |

| MM    | 0.38  | 1.02  |

| F IN. | 0.120 | 0.140 |

| MM    | 3.04  | 3.56  |

| G IN. | 0.090 | 0.110 |

| MM    | 2.29  | 2.79  |

| H IN. | 0.320 | 0.370 |

| MM    | 8.13  | 9.4   |

| J IN. | 0.008 | 0.012 |

| MM    | 0.20  | 0.30  |

| K IN. | 0.015 | 0.021 |

| MM    | 0.38  | 0.53  |

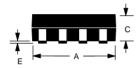

### **DS1602 8-PIN SOIC 200 MIL**

| PKG   | 8-P       | IN    |  |  |

|-------|-----------|-------|--|--|

| DIM   | MIN       | MAX   |  |  |

| A IN. | 0.203     | 0.213 |  |  |

| MM    | 5.16      | 5.41  |  |  |

| B IN. | 0.203     | 0.213 |  |  |

| MM    | 5.16      | 5.41  |  |  |

| C IN. | 0.070     | 0.074 |  |  |

| MM    | 1.78      | 1.88  |  |  |

| E IN. | 0.004     | 0.007 |  |  |

| MM    | 0.102     | 0.254 |  |  |

| F IN. | 0.074     | 0.84  |  |  |

| MM    | 1.88      | 2.13  |  |  |

| G IN. | 0.050 BSC |       |  |  |

| MM    | 1.27 BSC  |       |  |  |

| H IN. | 0.302     | 0.318 |  |  |

| MM    | 7.67      | 8.07  |  |  |

| J IN. | 0.006     | 0.010 |  |  |

| MM    | 0.152     | 0.254 |  |  |

| K IN. | 0.013     | 0.020 |  |  |

| MM    | 0.33      | 0.508 |  |  |

| L IN. | 0.19      | 0.030 |  |  |

| MM    | 4.83      | 0.762 |  |  |