**PRODUCT PREVIEW**

# Dual Inverting Log Gain/Attenuator

## FEATURES

- Ultra-low power consumption

- Operates from 3V or 5V supplies

- Two digitally controlled, 128–position potentiometers including mute

- Logarithmic Gain Characteristics

- Zero-crossing detection circuitry eliminates noise caused by discrete wiper position changes

- Two Control Interfaces

- 3-wire serial CPU control

- Push-button control

- 20-pin DIP (300 Mil), 20-pin SOIC (300 Mil), and 20-pin (173 Mil) TSSOP packaging available

- Operating Temperature:

- Commercial: 0°C to 70°C

- Industrial: -40°C to +85°C

- Software and hardware mute

- Resistance Available: 53KΩ

## **PIN ASSIGNMENT**

| GND                                                           |  | 1        | 20 |  | V <sub>CC</sub> |  |  |  |

|---------------------------------------------------------------|--|----------|----|--|-----------------|--|--|--|

| C <sub>OUT</sub>                                              |  | 2        | 19 |  | P1G             |  |  |  |

| CLK                                                           |  | 3        | 18 |  | P1A             |  |  |  |

| D                                                             |  | 4        | 17 |  | P0G             |  |  |  |

| RST                                                           |  | 5        | 16 |  | P0A             |  |  |  |

| ZCEN                                                          |  | 6        | 15 |  | MUTE            |  |  |  |

| MODE                                                          |  | 7        | 14 |  | AGND            |  |  |  |

| W0                                                            |  | 8        | 13 |  | IN1             |  |  |  |

| OUT0                                                          |  | 9        | 12 |  | OUT1            |  |  |  |

| IN0                                                           |  | 10       | 11 |  | W1              |  |  |  |

| 20–PIN DIP (300 MIL)<br>20–PIN SOIC (300 MIL)<br>20–PIN TSSOP |  |          |    |  |                 |  |  |  |

|                                                               |  | Saa Mach |    |  |                 |  |  |  |

See Mech. Drawings Section

## **PIN DESCRIPTION**

| OUT0,OUT1        | - | Low–end of resistor            |

|------------------|---|--------------------------------|

| INO, IN1         | _ | High-end of resistor           |

| W0,W1            | _ | Wiper Terminal                 |

| V <sub>CC</sub>  | _ | 3V or 5V Power Supply Input    |

| RST              | _ | Serial Port Reset Input        |

| CLK              | _ | Serial Port Clock Input        |

| D                | — | Serial Port Data Input         |

| C <sub>OUT</sub> | _ | Cascade Data Output            |

| P0G,P1G          | _ | Gain Input Pot Controls        |

| P0A,P1A          | _ | Attenuation Input Pot Controls |

| ZCEN             | _ | Zero–Crossing Detect Input     |

| MUTE             | _ | Hardware Mute Control Input    |

| AGND             | _ | Analog Ground                  |

| GND              | _ | Ground                         |

|                  |   |                                |

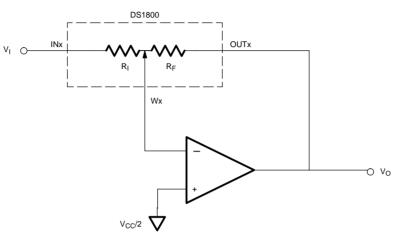

#### DESCRIPTION

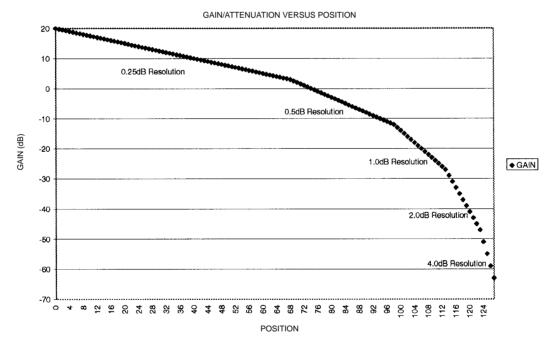

The DS1800 is a dual audio–taper potentiometer designed specifically for use in the feedback path of the inverting configuration of an operational amplifier (see Figure 2). In this configuration, the DS1800 provides a  $V_O/V_I$  relationship of –20log(R<sub>F</sub>/R<sub>I</sub>) giving a gain/attenuation range covering +20 dB to –63 dB. Each potentiometer has a total of 129 positions including mute. The DS1800 provides five areas of resolution which include 0.25 dB per step from +20 dB to +3 dB, 0.5 dB per step

from +3 dB to -12 dB, 1 dB from -12 dB to -27 dB, and from -27 dB to -47 dB; 2 dB per step, and from -47 dB to -63 dB; 4 dB per step. The mute position provides 100 dB of attenuation.

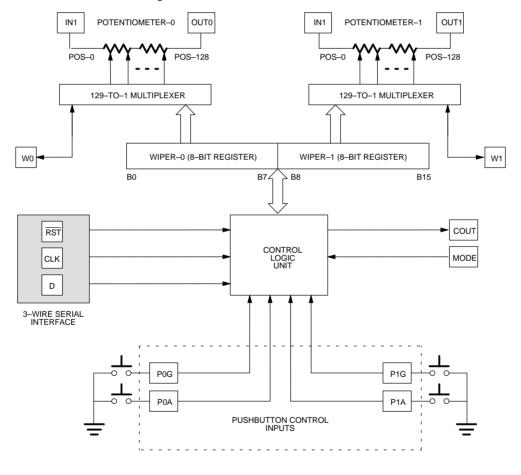

The DS1800 has two control interfaces (see Figure 1). The first is a 3-wire serial CPU interface consisting of  $\overline{RST}$ , CLK, and D. The second interface is a contactclosure interface, allowing easy push-button control without the need for external debounce or timing circuitry. The device also provides for software muting (via CPU) or hardware muting (MUTE control input). The hardware mute is a toggle type which returns the wiper positions to their prior states. Additional information on CPU and push–button control is described under the section entitled "OPERATION".

The DS1800 is available in 20–pin DIPs, SOICs, and TSSOPs. One standard resistance grade of  $53K\Omega$  is available for the device.

#### OPERATION

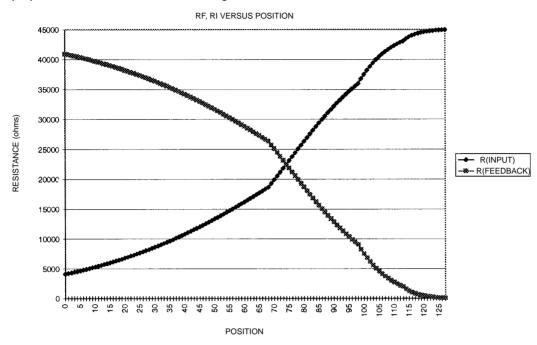

The DS1800 provides two 129–position 45K $\Omega$  potentiometers. These potentiometers are specifically designed to operate in the configuration shown in Figure 2. Under this configuration the V0/VI relationship provides the gain/attenuation function of –20log(R<sub>F</sub>/R<sub>I</sub>) over a range of +20 dB to –63 dB. This function is illustrated in Figure 3 as a graph of gain/attenuation versus position. Figure 4 provides the relationship between R<sub>F</sub> and R<sub>I</sub> as a function of position.

The DS1800 has a total of 129 positions including a mute position. Five areas of resolution are provided over the gain/attenuation range and are illustrated in Figure 3. From position 0 to position 68, a resolution of 0.25 dB per step is attained covering a gain/attenuation range of +20 dB to +3 dB. From position 68 to position 98, 0.5 dB per step of resolution is attained covering +3 dB to -12 dB of gain/attenuation. Positions 98 to 113 have 1 dB per step resolution and cover a gain/attenuation range of -12 to -27 dB. Positions 113 to 123 provide 2 dB per step and cover a gain/attenuation range of -27 dB to -47 dB. Positions 123 to 127 provide 4 dB per step and cover a gain/attenuation range of use a gain/attenuation range of -47 dB to 63 dB. Position 128 is the mute position and typically provides 100 dB of attenuation.

#### **PIN DESCRIPTIONS**

The DS1800 has a total of 20 pins which provide various functions for the device. This section provides a description of each pin's operation.

**V<sub>CC</sub>** – Power Supply Voltage Input. The DS1800 will support 3V or 5V power supply operation.

**GND** – Ground. The DS1800 has two ground pins. The GND supports the digital ground for the device.

**AGND** – Analog Ground. The DS1800 has two ground pins. The AGND supports analog ground for the device.

**IN0, IN1** – Input terminals for the two respective potentiometers as shown in Figure 2. These terminals should be connected to the analog signal,VI, to provide the gain/attenuation characteristics stated. These terminals are referenced as INx in the Figure 2 drawing.

**OUT0, OUT1** – Analog Outputs. These pins should be connected to the output terminal of the operational amplifier as shown in Figure 2. These inputs are referenced as OUTx in the Figure 2 drawing.

**W0, W1** – Wiper Terminals. The wiper terminals of each pot are connected to the inverting terminal of the operational amplifier. The position of the wiper terminal is selected either through CPU control or push–button control.

**P0A, P1A** – Attenuation Push–button Inputs. These push–button inputs are used to control wiper position of the part. Activity on these inputs will cause the position of the wiper to move towards the OUT0, and OUT1 terminals, respectively.

**P0G, P1G** – Gain Push–button Inputs. These push– button inputs control wiper position and are used to move the position of the wiper towards the IN0 and IN1 terminals, respectively.

**RST** – Serial Port Reset. The RST input deactivates the 3–wire serial interface. This input is active when in the low–state. All 3–wire communications must take place when this input is in a high state.

**CLK** – Serial Clock Input. The CLK input is the positive– edge clock signal input used for 3–wire timing synchronization.

**D** – Serial Data Input. The D input is used to input serial data for wiper position changes.

$C_{OUT}$  – Serial Cascade Output. The  $C_{OUT}$  is an output signal used to read the contents of the current settings of the wiper positions. As data is clocked into the D input, data corresponding to the wipers are shifted out of the  $C_{OUT}$  pin.

032098 2/13

**MODE** – Push–button Debounce Control. The MODE pin is used to choose between a fast and slow mode of push–button debouncing. When in a high state, push– button debounce is slow. When in a low–state, push– button debounce is faster. These timing differences are discussed in the section entitled "Push–button Interface Control". The state of this pin is determined only at device power–up.

#### **POWER-UP CONDITIONS**

The position of the wipers of the DS1800 on power up are internally set to position 127, which is the last position before mute. The user then has the responsibility of changing the wiper position to the desired attenuation/ gain levels.

Additionally, the serial port is stable and active within 10 microseconds. The contact closure control interface inputs are active after 50 ms.

#### INTERFACE CONTROL OPTIONS

Control of the DS1800 is provided via two types of interface ports. A 3-wire CPU control interface allows the exact wiper positions of the potentiometers to be written using two 8-bit words. A cascade output,  $C_{OUT}$ , is provided when controlling multiple devices via one CPU or when reading the wiper positions of each potentiometer.

The second interface is a contact closure interface that allows push–buttons to control movement of the wiper positions. Under push–button control no external debounce or timing circuitry is needed. A block diagram of the DS1800 is shown in Figure 1.

#### 3-WIRE SERIAL INTERFACE CONTROL

CPU control of the DS1800 is accomplished using the 3–Wire serial port of the device. This interface drives an internal control logic unit. Direct wiper positioning is accomplished by using this port which consist of three input signals:  $\overline{\text{RST}}$ , CLK, and D.

The RST control signal is used to enable 3–wire serial port write operations. The CLK terminal is an input that provides synchronization for data I/O. Data is input bit by bit via the D input signal pin.

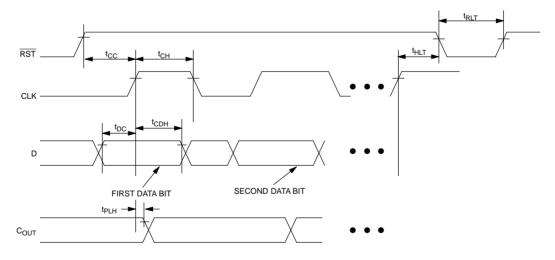

The 3–Wire serial timing diagrams are provided in Figure 5. Serial port operation or activity begins with the transition of the  $\overline{RST}$  signal from a low–state to a high–state. Once activated, data is clocked into the part on

the low to high transition of the CLK signal input. Data input via the D terminal is transferred in order of the desired potentiometer–0 wiper value, followed by the potentiometer–1 wiper position value.

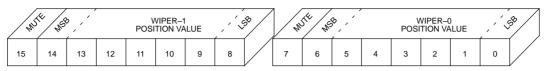

Two 8-bit values are used to store wiper position for each potentiometer during powered conditions. These 8-bit values are written to a 16-bit I/O shift register. A detailed diagram of the 16-bit I/O shift register is shown in Figure 6.

Bits 0 through 7 are reserved for the positioning of wiper–0 while bits 8 through 15 are reserved for control of wiper–1. Bits 0 through 6 are used for actual wiper positioning of potentiometer–0. Bit 7 is used to mute potentiometer–0. If this bit is set to a "1", the potentiometer–0 wiper will be connected to the OUT0 end of the resistor array regardless of the settings of bits 0 through 6.

Bits 8 through 15 are used for positioning the wiper of potentiometer–1. Bits 8 through 14 control wiper position on the resistor array. Bit 15 is used for muting potentiometer–1. Bit 15, like bit 7, when set to "1" will mute potentiometer 1, regardless of the settings of bits 8 through 14.

Data is transmitted LSB first starting with bit–0. A complete transmission of 16 bits of data is required to insure proper setting of each potentiometer's wiper. An incomplete transmission may result in undesired wiper settings.

Once the 16 bits of information has been transmitted and the  $\overline{RST}$  signal input transitions to a low-state, the new wiper positions are loaded into the part.

#### **PUSH-BUTTON INTERFACE CONTROL**

The DS1800 can be configured to operate from contact closure or push–button inputs. The push–button inputs consist of signals P0A, P0G, P1A, P1G and MUTE. P0A and P0G allow attenuation and gain control of the input signal to potentiometer–0, while P1A and P1G provide the same control for potentiometer–1. The MUTE input provides a toggle control for muting the potentiometers via pushbutton.

The P0A and P1A control inputs, based on the recommended circuit configuration, are used to attenuate the incoming signal by moving the wiper position towards the OUTx terminals. The P0G and P1G control inputs provide the opposite function; positioning the wiper(s) closer to the INx terminals, thus providing gain.

Each of these control inputs are internally pulled–up via a 50K $\Omega$  resistance. Additionally, these inputs require no external components for debouncing or timing which are provided internal to the part.

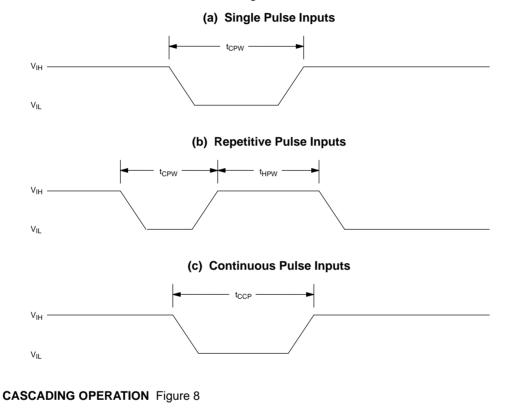

Contact closure is defined as the transition from a high level to a low level on these input terminals. The DS1800 interprets input pulse widths as the means of controlling wiper movement. A single pulse input over the PxA or PxG input terminals will cause the wiper to move one position. A transition from high to low on these inputs is considered the beginning of pulse activity or contact closure. The DS1800 has two timing modes for controlling the speed at which pushbuttons will operate. These modes are termed fast mode operation and slow mode operation.

In slow mode operation, a single pulse is defined as being greater than 1 ms but lasting no longer than 0.8 seconds. Correspondingly, in fast mode operation, a single pulse is defined as being greater than 50  $\mu$ s but lasting no longer than 0.8 second.

Repetitive pulsed inputs can be used to step through each resistive position of the device in a relatively fast manner. The timing requirements for repetitive pulsed inputs is that pulses must be separated by a minimum time of 1 ms for slow mode operation and 50  $\mu$ s for fast mode operation.

Pulse inputs lasting longer than 0.8 seconds will cause the wiper to move one position every 25 ms seconds after the initial 0.8 second hold time. This is true regardless of the mode input. The total time required to transcend the entire potentiometer using a continuous input pulse is given by the following formula:

0.8(seconds) + 127 x 25 ms = 3.975(seconds)

#### SLOW MODE AND FAST MODE OPERATION

Pushbutton operation, as mentioned, can be operated at two distinct speeds or modes; fast and slow. The mode or speed of pushbutton debounce is determined at device power–up by the state of the MODE pin. When MODE powers to a high–state, pushbutton debounce timing will operate at the slow mode rate. When powered and in the low–state, debounce timing operates at the fast rate. Timing specifications for pushbutton

032098 4/13

operation can be found in the AC Electrical Specification Table for pushbutton operation. Timing diagrams for push–button operation can be found in Figure 7.

#### ZERO CROSSING DETECTION

The DS1800 provides a zero-crossing detection capability when using the 3-Wire serial interface. Zerocrossing detection provides a means for minimizing unwanted audible noise that may result from sizable discrete wiper transitions when using the part in audio applications. The zero crossing detect feature allows independent wiper changes only when the two terminals of the potentiometer(s) have equal potentials and within a 50 ms time window from the fall of the RST signal. If at 50 ms the DS1800 has not detected a zero crossing, the wiper position of the potentiometer(s) will change regardless of the state of the input signal. Zerocrossing detection is activated when the ZCEN input is in a low-state. When high, the  $\overline{\text{ZCEN}}$  input deactivates both the 50 ms time requirement and zero-detection crossing.

Zero crossing detection is also available when using the part in push–button operation. When a push–button is activated, the part will change wiper position during the first detected zero–crossing or at the end of a 50 ms time window.

When operating in push–button operation with a continuous input pulse, the wiper position will change once during the initial 0.8 second time period. This change is dictated by a detected zero–crossing or 50 ms time window. Subsequent changes when operating with a continuous input pulse occur on 25 ms time intervals and are dependent on zero crossings or 50 ms time–outs.

#### **MUTE CONTROL**

The DS1800 provides a mute control feature which can be accessed by the user through hardware or software. Hardware control of the device is achieved through the MUTE input pin. This pin is internally pulled up through a 50K resistor and functions like the PxG and PxA pushbutton controls. When this input is driven low, the wiper outputs of both potentiometers will be internally connected to the OUTx terminal of their respective potentiometers. This input performs as a toggle input, with the first activity on this pin connecting the wiper terminals to the OUTx terminals (position 128) of the potentiometer. The next input activity on this pin will return the wiper position to the previous state before muting occurred. Also, if operating in push–button mode, MUTE will be deactivated if an input is received over any push–button input. This input, like the push–button inputs, is internally debounced and requires no external circuitry. When the device powers up, the first activity on the mute pin will move the wipers to position 128 or the OUTx end of the potentiometer(s).

Software muting was discussed in the 3–wire serial control section. Bits 7 and 15 are reserved for muting each respective potentiometer. If these bits have value "1", the wiper positions of the pot will be transferred to the mute position. Unlike hardware mute control, software muting allows the user individual control of each potentiometer. Additionally, the software mute requires that the complete wiper position setting be rewritten to establish a non muted position. Note that bits 7 and 15 of the I/O shift register must have value "0" to release the software mute position.

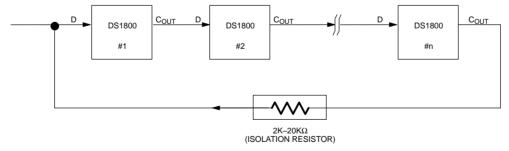

#### **CASCADE OPERATION**

A feature of the DS1800 is the ability to control multiple devices from a single processor. Multiple DS1800's can be linked or daisy chained as shown in Figure 8. As a data bit is entered into the I/O shift register of the DS1800, a data bit will appear at the C<sub>OUT</sub> output after a maximum delay of 50 nanoseconds.

The  $C_{OUT}$  output of the DS1800 can be used to drive the D input of another DS1800. When connecting multiple devices, the total number of bits sent is always 16 times the number of DS1800's is the daisy chain.

An optional feedback resistor can be placed between the  $C_{OUT}$  terminal of the last device and the D input of the first DS1800, thus allowing the controlling processor to circularly clock data through the daisy chain. The value of the feedback or isolation resistor should be in the range from 2K to 20K $\Omega$ .

When reading data via the  $C_{OUT}$  pin and the isolation resistor, the D input is left floating by the reading device. When  $\overline{RST}$  is driven high, bit–0 is present on the  $C_{OUT}$  pin, which is fed back to the D pin through the isolation resistor. When the CLK input transitions low to high, bit–0 is loaded into the first position of the I/O shift register and bit 1 becomes present on  $C_{OUT}$  and D of the next device. After 16 bits (or 16 times the number of DS1800s in the daisy chain), the data has shifted completely around and back to its original position. When RST transitions to the low state to end data transfer, the value (the same as before the read occurred is loaded into the wiper–0 and wiper–1 registers.

DS1800

## ABSOLUTE MAXIMUM RATINGS\* Voltage on Any Pin Relative to Ground

Voltage on Any Pin Relative to Ground Operating Temperature

Storage Temperature Soldering Temperature -1.0V to +7.0V 0°C to 70°C; commercial -40°C to +85°C; industrial -55°C to +125°C 260°C for 10 seconds

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| RECOMMENDED DC OPERAT | (-40°C to +85°C) |         |     |                      |       |       |

|-----------------------|------------------|---------|-----|----------------------|-------|-------|

| PARAMETER             | SYMBOL           | MIN     | ТҮР | MAX                  | UNITS | NOTES |

| Supply Voltage        | V <sub>CC</sub>  | 2.7     |     | 5.5                  | V     | 1     |

| Input Logic 1         | V <sub>IH</sub>  | 2.0     |     | V <sub>CC</sub> +0.5 | V     | 1, 2  |

| Input Logic 0         | V <sub>IL</sub>  | -0.5    |     | +0.8                 | V     | 1, 2  |

| Analog Ground         | AGND             | GND-0.5 |     | GND+0.5              |       | 14    |

| Resistor Inputs       | L,H,W            | GND-0.5 |     | GND+0.5              | V     | 1     |

## DC ELECTRICAL CHARACTERISTICS

(-40°C to +85°C; V<sub>CC</sub>=2.7V to 5.5V)

| PARAMETER          |                    | SYMBOL            | MIN | ТҮР      | MAX  | UNITS    | NOTES |

|--------------------|--------------------|-------------------|-----|----------|------|----------|-------|

| Supply Current     |                    | I <sub>CC</sub>   |     |          | 2000 | μA       | 10    |

| Input Leakage      |                    | ILI               | -1  |          | +1   | μA       |       |

| Wiper Resistance   |                    | R <sub>W</sub>    |     | 400      | 1000 | Ω        |       |

| Wiper Current      |                    | IW                |     |          | 1    | mA       |       |

| Logic 1 Output Cur | rent @ 2.4V        | I <sub>ОН</sub>   | -1  |          |      | mA       |       |

| Logic 0 Output Cur | rent @ 0.4V        | I <sub>OL</sub>   |     |          | 4    | mA       |       |

| Standby Current:   | 3 Volts<br>5 Volts | I <sub>STBY</sub> |     | 12<br>20 | 40   | μΑ<br>μΑ | 12    |

| Power Up Time      |                    | t <sub>PU</sub>   |     | 50       |      | ms       | 8     |

032098 6/13

## ANALOG RESISTOR CHARACTERISTICS

# $(-40^{\circ}C \text{ to } +85^{\circ}C; V_{CC}=2.7V \text{ to } 5.5V)$

| PARAMETER                                                                           | SYMBOL              | MIN          | ТҮР   | MAX           | UNITS    | NOTES |

|-------------------------------------------------------------------------------------|---------------------|--------------|-------|---------------|----------|-------|

| Total Resistance                                                                    |                     |              | 53    |               | KΩ       |       |

| End-to-End Resistor Tolerance                                                       |                     | -20          |       | +20           | %        |       |

| Absolute Tolerance                                                                  |                     | -0.5<br>-1.0 |       | +0.5<br>+1.0  | dB<br>dB | 9     |

| Tap-to-Tap Tolerance                                                                |                     | -0.5         |       | +0.5          | dB       | 7     |

| Interchannel Matching                                                               |                     | 0.25<br>0.5  |       | +0.25<br>+0.5 | dB<br>dB | 6     |

| -3 dB Cutoff Frequency                                                              | f <sub>cutoff</sub> |              | 1     |               | MHz      | 13    |

| Temperature Coefficient                                                             |                     |              | 650   |               | ppm/°C   |       |

| Total Harmonic Distortion<br>(V <sub>IN</sub> =1Vrms, 20 Hz to 20 KHz,<br>Tap=0 dB) | THD                 |              | 0.002 |               | %        | 13    |

| Output Noise (20 Hz to 20 KHz,<br>Grounded Input, Tap=0 dB)                         |                     |              | 2.2   |               | μVrms    | 13    |

| Digital Feedthrough (20 Hz to 20<br>KHz, Tap=0 dB)                                  |                     |              | -90   |               | dB       | 13    |

| Interchannel Isolation (1 KHz,<br>Tap=0 dB)                                         |                     |              | -100  |               | dB       | 13    |

| Mute Control Active                                                                 | MUTE                |              | -100  |               | dB       |       |

## CAPACITANCE

$(-40^{\circ}C \text{ to } +85^{\circ}C; V_{CC}=2.7V \text{ to } 5.5V)$

| PARAMETER          | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|--------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance  | C <sub>IN</sub>  |     |     | 5   | pF    |       |

| Output Capacitance | C <sub>OUT</sub> |     |     | 7   | pF    |       |

#### DS1800

| AC ELECTRICAL CHARACTERISTICS                                    |                  |     |     | (-40°C to +85°C; V <sub>CC</sub> =2.7V to 5.5V) |       |       |  |

|------------------------------------------------------------------|------------------|-----|-----|-------------------------------------------------|-------|-------|--|

| PARAMETER                                                        | SYMBOL           | MIN | ТҮР | MAX                                             | UNITS | NOTES |  |

| CLK Frequency                                                    | f <sub>CLK</sub> | DC  |     | 10                                              | MHz   |       |  |

| Width of CLK Pulse                                               | t <sub>CH</sub>  | 50  |     |                                                 | ns    |       |  |

| Data Setup Time                                                  | t <sub>DC</sub>  | 30  |     |                                                 | ns    |       |  |

| Data Hold Time                                                   | t <sub>CDH</sub> | 10  |     |                                                 | ns    |       |  |

| Propagation Delay Time<br>Low to High Level<br>High to Low Level | t <sub>PLH</sub> |     |     | 50                                              | ns    |       |  |

| RST High to Clock Input High                                     | t <sub>CC</sub>  | 50  |     |                                                 | ns    |       |  |

| RST Low from Clock Input High                                    | t <sub>HLT</sub> | 50  |     |                                                 | ns    |       |  |

| CLK Rise Time                                                    | t <sub>CB</sub>  |     |     | 50                                              | ns    |       |  |

| RST Inactive                                                     | t <sub>BLT</sub> | 200 |     |                                                 | ns    |       |  |

## **AC ELECTRICAL CHARACTERISTICS** PUSHBUTTON INPUTS

| PUSHBUTTON INPUTS                                          |                  |         |     | (-40°C to +85°C; V <sub>CC</sub> =2.7V to 5.5V) |          |          |  |

|------------------------------------------------------------|------------------|---------|-----|-------------------------------------------------|----------|----------|--|

| PARAMETER                                                  | SYMBOL           | MIN     | ТҮР | MAX                                             | UNITS    | NOTES    |  |

| Single Pulse Input<br>Slow Mode<br>Fast Mode               | t <sub>CPW</sub> | 1<br>50 |     | 800                                             | ms<br>μs | 3, 5, 11 |  |

| Repetitive Input Pulse High Time<br>Slow Mode<br>Fast Mode | t <sub>HPW</sub> | 1<br>50 |     | 800                                             | ms<br>μs | 3, 5, 11 |  |

| Continuous Input Pulse                                     | t <sub>CCP</sub> | 0.8     |     | DC                                              | S        | 3, 5, 11 |  |

## NOTES:

- 1. All voltages are referenced to ground

- 2. Valid for  $V_{CC} = 5V$  only.

- 3. Both PxA and PxG inputs are internally pulled up with a 50K $\Omega$  resistance.

- 4. Capacitance values apply at 25°C.

- 5. Input pulse width is the minimum time required for an input to cause an increment or decrement of wiper position. If the PxA or PxG inputs are held active for longer than 0.8 seconds, subsequent increments or decrements will occur at intervals of 25 ms. Timing tolerances for pushbutton control are specified at 35%.

- 6. Inter-Channel Matching is used to determine the relative voltage difference in dB between the same position on each potentiometer. The DS1800 is specified for ±0.25 dB inter channel matching from position 0 to position 112 (+20 dB to -27 dB) and  $\pm 0.5$  dB from position 113 to position 127.

- 7. Tap-to-Tap tolerance is used to determine the change in voltage between successive tap positions. The DS1800 is specified for ±0.5 dB tap-to-tap tolerance. From position 0 to position 112 (+20 dB to -27 dB). From position 113 to position 127, the DS1800 is specified for ±1 dB tap-to-tap tolerance.

032098 8/13

- 8. Power–up time is the time for all push–button inputs to be stable and active once power has reached a valid level, 2.7V min.

- 9. Absolute tolerance is used to determine wiper voltage versus expected wiper voltage as determined by wiper position. The DS1800 is bounded by a ±0.5 dB absolute tolerance from position 0 to position 112 and ±1 dB tolerance from position 113 to position 127.

- 10. Maximum current specifications are based on clock rate, active zero-crossing detection, and push-button activation.

- 11. Valid for  $V_{CC} = 3V$  or 5V.

- 12. Standby current levels apply when all inputs are driven to appropriate supply levels.

- 13. These parameters are characterized and not 100% tested.

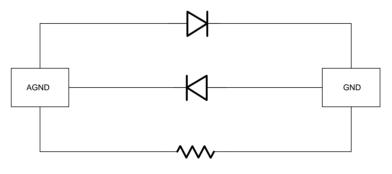

- 14. See Figure 9.

## DS1800 BLOCK DIAGRAM Figure 1

032098 9/13

## **RECOMMENDED CIRCUIT CONFIGURATION** Figure 2

## Vo/VI GAIN/ATTENUATION VS. POSITION RELATIONSHIP Figure 3

032098 10/13

R<sub>F</sub>/R<sub>I</sub> RELATIONSHIP VS. POSITION Figure 4

<sup>3-</sup>WIRE SERIAL TIMING DIAGRAM Figure 5

DS1800

# 16-BIT I/O SHIFT REGISTER Figure 6

# CONTACT CLOSURE TIMING DIAGRAMS Figure 7

032098 12/13

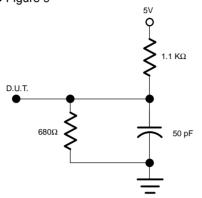

# DIGITAL OUTPUT LOAD Figure 9

# INTERNAL GROUND CONNECTIONS Figure 10

$100\Omega$  (TYPICAL)

NOTE: GND and AGND must be tied to the same voltage level.

032098 13/13