# DS21T06 SCSI Terminator

### **FEATURES**

- Fully compliant with SCSI-1, Fast SCSI and Ultra SCSI

- Functional drop in replacement for the DS2106

- Complimentary part to DS21T07 for wide SCSI

- Provides active termination for 18 signal lines

- 5% tolerance on termination resistors and voltage regulator

- 5% tolerance on termination current

- Low power down capacitance of 3 pF

- Onboard thermal shutdown circuitry

- SCSI bus hot plug compatible

- Fully supports actively negated SCSI signals

### **PIN ASSIGNMENT**

DS21T06S 28-PIN SOIC (300 MIL)

### **DESCRIPTION**

Fast SCSI and Ultra SCSI require the use of active terminations at both ends of every cable segment in a SCSI system with single–ended drivers and receivers. Ultra SCSI requires support of active negation and hot plugging. The DS21T06 is fully compliant with these standards.

The DS21T06 integrates a low dropout regulator and 18 precise switched 10  $\Omega$  termination resistors into a 28–pin 300 mil SOIC package.

Active termination provides greater immunity to voltage drops on the TERMPWR (TERMination PoWeR) line, enhanced high–level noise immunity, intrinsic TERMPWR decoupling, and very low quiescent current consumption. One DS21T06 can be used to terminate the Narrow SCSI bus, or a DS21T07 can be used with a DS21T06 for termination of a Wide SCSI bus.

#### REFERENCE DOCUMENTS

SCSI-2 (X3.131-1994) SCSI-3 Parallel Interface (X3T10/855D) SCSI-3 Fast-20 (X3T10/1071D)

#### **FUNCTION DESCRIPTION**

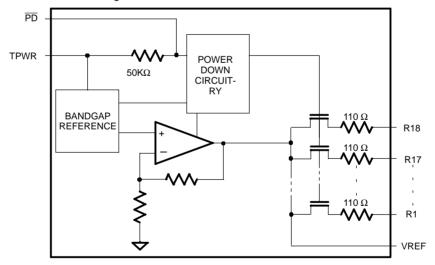

The DS21T06 is designed to be a single chip termination subsystem for use in Narrow SCSI systems. The DS21T06 consists of a bandgap reference, buffer amplifier, and 18 termination resistors (Figure 1). The voltage regulator circuitry (bandgap reference and class AB power amplifier) produces a precise laser trimmed 2.85 volt level and is capable of sourcing 25 mA into each of the terminating resistors when the signal line is low (active). When the external driver for a given signal line turns off, the active terminator will pull that signal line to 2.85 volts (quiescent state). When used with an active negation driver, the power amp can sink 22 mA per line while keeping the voltage reference in regulation; the terminating resistors maintain their 110  $\Omega$  value over the entire voltage range. When all lines settle in the quiescent state, the regulator will consume about 10 mA.

When the DS21T06 is put into power–down mode by bringing  $\overline{PD}$  low, the power–down circuitry will turn off the transistors on each signal line. This will isolate the DS21T06 from the signal lines and effectively remove it from the circuit. The power–down pin ( $\overline{PD}$ ) has an internal  $50K\Omega$  pull–up resistor. To place the DS21T06 into an

Available from: Global Engineering Documents

15 Inverness Way East Englewood, CO 80112–5704

Phone: (800) 854-7179,(303) 792-2181

Fax: (303) 792-2192

active state, the  $\overline{\text{PD}}$  pin should be tied higher left open circuited.

To ensure proper operation, the TPWR pin should be connected to the SCSI bus TERMPWR line. As with all analog circuitry, the TERMPWR lines should be bypassed locally. A 2.2  $\mu F$  capacitor and a 0.01  $\mu F$  high frequency capacitor is recommended between TPWR and ground and placed as close as possible to the DS21T06. The DS21T06 should be placed as close as possible to the connector to minimize signal and power trace length, thereby resulting in less input capacitance and reflections which can degrade the bus signals.

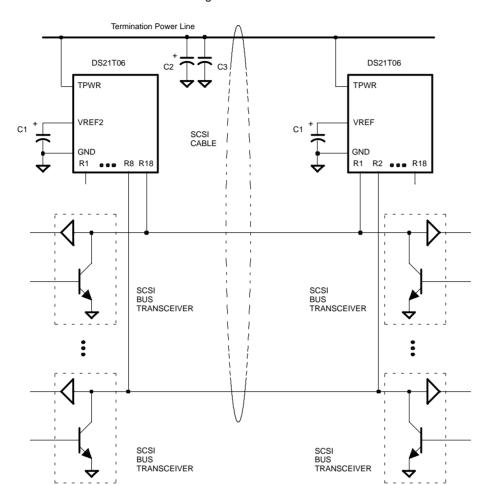

To maintain the specified regulation, a 4.7  $\mu$ F capacitor is required between the VREF pin and ground of each DS21T06. A high frequency cap (0.1  $\mu$ F ceramic recommended) can also be placed on the VREF pin in applications that use fast rise/fall time drivers. Figure 2 details a typical SCSI bus configuration. In an 8–bit data SCSI bus (Narrow SCSI), one DS21T06 is needed for proper termination of the 18 active signal lines. One DS21T06 and one DS21T07 can be used to terminate the 27 active signal lines in a 16–bit data SCSI bus (Wide SCSI).

## **DS21T06 BLOCK DIAGRAM** Figure 1

# **TYPICAL SCSI BUS CONFIGURATION** Figure 2

# NOTES:

- 1. C1 = 4.7  $\mu$ F tantalum C2 = 2.2  $\mu$ F tantalum or 4.7  $\mu$ F aluminum C3 = 0.01  $\mu$ F ceramic

- 2. If the DS21T06 is to be embedded into a peripheral that will act as a target on a SCSI bus, it is recommended that TERMPWR be derived from the SCSI cable, not generated locally. In this configuration, if a power failure occurs in the peripheral, it will not affect the bus.

- 3. A high frequency bypass capacitor (0.1  $\mu$ F recommended) can be added in parallel to C1 for applications using fast rise/fall time drivers.

# PIN DESCRIPTION Table 1

| PIN                                   | SYMBOL          | DESCRIPTION                                                                                                                                                                                                  |

|---------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                     | PD              | <b>Power Down.</b> When tied low, the DS21T06 enters power–down mode. Contains an internal $50K\Omega$ pull–up. Tie low to deactivate the DS21T06. Tie high or leave open circuited to activate the DS21T06. |

| 2 -6, 10 -<br>13, 16 - 19,<br>23 - 27 | R1R13<br>R14R18 | Signal Termination 1. 110 $\Omega$ termination. Connect to SCSI bus signal lines.                                                                                                                            |

| 7 – 9,<br>20 – 22                     | HS-GND          | <b>Heat Sink Ground.</b> Internally connected to the mounting pad. Should be either grounded or electrically isolated from other circuitry.                                                                  |

| 14                                    | TPWR            | Termination Power. Connect to the SCSI TERMPWR line. Bypass with a 2.2 $\mu\text{F}$ cap.                                                                                                                    |

| 15                                    | VREF            | Reference Voltage. 2.85 volt reference; must be decoupled with a 4.7 $\mu\text{F}$ capacitor.                                                                                                                |

| 28                                    | GND             | Ground. Signal ground; 0.0 volts.                                                                                                                                                                            |

### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on Any Pin Relative to Ground

Operating Temperature

Storage Temperature

Soldering Temperature

O°C to 70°C

-55°C to +125°C

260°C for 10 seconds

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

The Dallas Semiconductor DS21T06 is built to the highest quality standards and manufactured for long term reliability. All Dallas Semiconductor devices are made using the same quality materials and manufacturing methods. However, the DS21T06 is not exposed to environmental stresses, such as burn–in, that some industrial applications require. For specific reliability information on this product, please contact the factory in Dallas at (972) 371–4448.

#### RECOMMENDED OPERATING CONDITIONS

(0°C to 70°C)

| PARAMETER       | SYMBOL           | MIN  | TYP | MAX                  | UNITS | NOTES |

|-----------------|------------------|------|-----|----------------------|-------|-------|

| TERMPWR Voltage | V <sub>TP</sub>  | 4.00 |     | 5.25                 | V     |       |

| PD Active       | V <sub>PDA</sub> | -0.3 |     | 0.8                  | V     |       |

| PD Inactive     | V <sub>PDI</sub> | 2.0  |     | V <sub>TP</sub> +0.3 | V     |       |

## **DC CHARACTERISTICS**

(0°C to 70°C)

| PARAMETER                          | SYMBOL            | MIN   | TYP | MAX       | UNITS | NOTES        |

|------------------------------------|-------------------|-------|-----|-----------|-------|--------------|

| TERMPWR Current                    | I <sub>TP</sub>   |       | 10  | 500<br>14 | mA    | 1, 3<br>1, 4 |

| Power Down Current                 | I <sub>PD</sub>   |       | 500 |           | μΑ    | 1, 2, 5      |

| Termination Resistance             | R <sub>TERM</sub> | 107.5 | 110 | 119.5     | Ω     | 1, 2         |

| Die Thermal Shutdown               | TS <sub>D</sub>   |       | 150 |           | °C    | 1            |

| Power Down Termination Capacitance | C <sub>PD</sub>   |       | 3.0 | 3.5       | pF    | 1, 2, 5, 6   |

| Input Leakage High                 | I <sub>IH</sub>   | -1.0  |     |           | μΑ    | 1            |

| Input Leakage Low                  | I <sub>IL</sub>   |       |     | 1.0       | μΑ    | 1, 7         |

### **REGULATOR CHARACTERISTICS**

(0°C to 70°C)

| PARAMETER        | SYMBOL            | MIN | TYP  | MAX  | UNITS | NOTES |

|------------------|-------------------|-----|------|------|-------|-------|

| Output Voltage   | $V_{REF}$         | 2.7 | 2.85 | 3.0  | V     | 1, 2  |

| Drop Out Voltage | $V_{DROP}$        |     | 0.75 | 1.0  | V     | 3, 6  |

| Output Current   | I <sub>OUT</sub>  |     |      | 25.2 | mA    | 9     |

| Line Regulation  | LI <sub>REG</sub> |     | 1.0  | 2.0  | %     | 1, 4  |

| Load Regulation  | LO <sub>REG</sub> |     | 1.3  | 3.0  | %     | 1, 2  |

| Current Limit    | ΙL                |     | 700  |      | mA    | 1     |

| Sink Current     | I <sub>SINK</sub> |     | 400  |      | mA    | 1     |

## NOTES:

- 1. 4.00V < TERMPWR < 5.50V.

- 2. 0.0V < signal lines < TERMPWR.

- 3. All signal lines = 0.0V.

- 4. All signal lines open.

- 5. Power down enabled;  $\overline{PD} = 0.0V$ .

- 6. Guaranteed by design; not production tested.

- 7.  $V_{SIGNAL} = 0.2V$ .

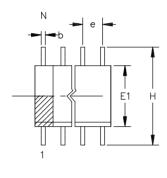

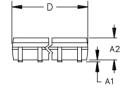

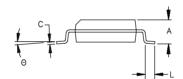

# 28-PIN SOIC (300 MIL)

The chamfer on the body is optional. If it is not present, a terminal 1 identifier must be positioned so that 1/2 or more of its area is contained in the hatched zone.

| PKG    | 28-PIN         |               |  |  |  |

|--------|----------------|---------------|--|--|--|

| DIM    | MIN            | MAX           |  |  |  |

| A IN.  | 0.094          | 0.105         |  |  |  |

| MM     | 2.39           | 2.67          |  |  |  |

| A1 IN. | 0.004          | 0.012         |  |  |  |

| MM     | 0.102          | 0.30          |  |  |  |

| A2 IN. | 0.089          | 0.095         |  |  |  |

| MM     | 2.26           | 2.41          |  |  |  |

| b IN.  | 0.013          | 0.020         |  |  |  |

| MM     | 0.33           | 0.51          |  |  |  |

| C IN   | 0.009<br>0.229 | 0.013<br>0.33 |  |  |  |

| D IN.  | 0.698          | 0.712         |  |  |  |

| MM     | 17.73          | 18.08         |  |  |  |

| e IN.  | 0.050 BSC      |               |  |  |  |

| MM     | 1.27 BSC       |               |  |  |  |

| E1 IN. | 0.290          | 0.300         |  |  |  |

| MM     | 7.37           | 7.62          |  |  |  |

| H IN   | 0.398          | 0.416         |  |  |  |

| MM     | 10.11          | 10.57         |  |  |  |

| L IN   | 0.016          | 0.040         |  |  |  |

| MM     | 0.40           | 1.02          |  |  |  |

| Θ      | 0°             | 8°            |  |  |  |