# **PRODUCT SPECIFICATION**

**Revision 1.3**

030598 1/185

### 1.0 OVERVIEW

### 1.1 DESCRIPTION

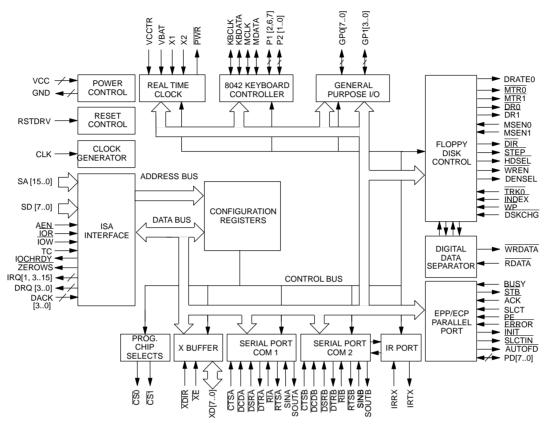

The DS83CH20 provides a complete solution for all of the desired functions in desktop PC I/O. It incorporates a complete floppy disk controller with a digital data separator, keyboard controller, real time clock, IEEE 1284 compliant parallel port, and two 16550A compatible UARTs with infrared communication support. Also provided are two programmable chip selects and 12 general purpose I/O pins. Full Plug and Play support and advanced power management features make the DS83CH20 an ideal choice for advanced green desktop PC designs.

The DS83CH20 meets or exceeds all Microsoft recommendations for the PC'95 Plug and Play system designs. The system interface supports a direct connection to the ISA bus that decodes all 16 address lines for the on-chip functions. All internal devices can be enabled and disabled independently. In addition, all non-static on-chip devices can be relocated within the I/O address map and assigned interrupt and DMA channels per the PC'95 recommendations.

The FDC is fully 82077SL compatible and supports the standard PC data rates of 250, 300, and 500 kbps, and 1 Mbps in MFM-encoded data mode. A perpendicular recording mode supports high density media. When used with the 1 Mbps data rate, this new mode allows the use of a 4 Mbyte floppy drives which format ED media to 2.88 Mbyte capacity. The FDC also supports power saving features that are software compatible with the 82077SL. These include clock disable, immediate auto-powerdown, low-latency awakening, and a power-saving state for the write precompensator. The high performance digital data separator needs no external components, and is compatible with the strict data separator requirements of floppy and floppy-tape drives. In software, the FDC can be located to one of two standard addresses within the ISA map, and can be assigned one of ten interrupt channels and one of 4 DMA channels.

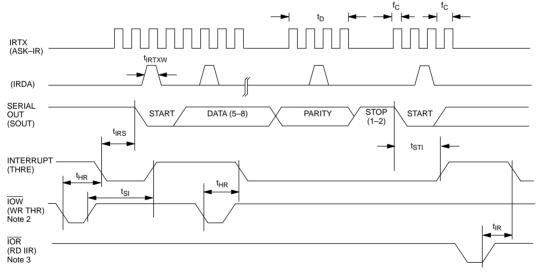

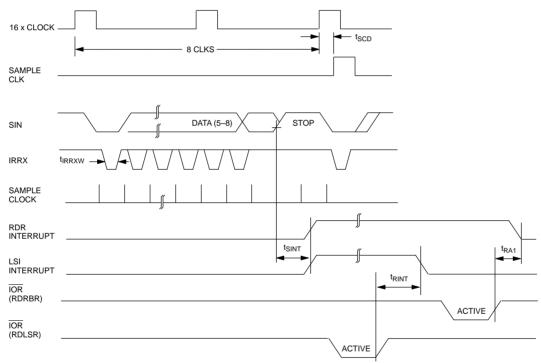

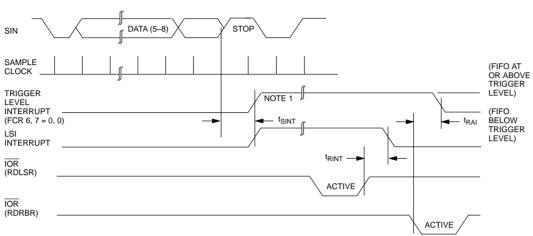

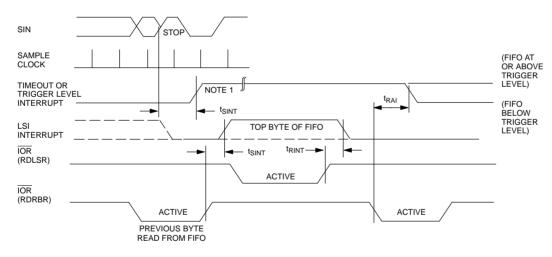

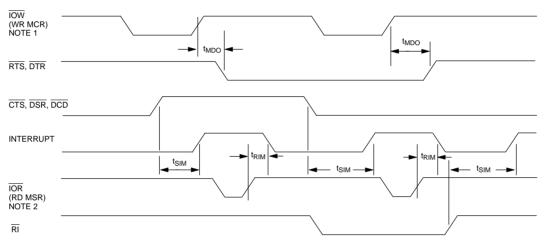

The two UARTs are fully 16550A compatible and support MIDI baud rates. One port also supports a full complement of infrared transmit and receive communication with IrDA 1.0, and Sharp ASK. The UARTs can be independently located to one of 256 possible locations within the ISA map, and independently assigned one of ten interrupt channels.

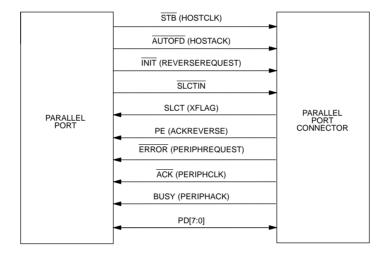

The IEEE 1284 parallel port is fully compatible with the IEEE 1284 standard, including level 2 support. This port supports Enhanced Parallel Port (EPP) including both V1.7 and V1.9 modes, and an Extended Capabilities Port (ECP). Full compatibility is maintained with ISA, EISA, and Micro Channel parallel ports. Software can locate the parallel port to one of 256 possible locations within the ISA map, and assign the port to one of ten interrupt channels and one of four DMA channels.

The keyboard controller is fully software and hardware compatible with the 8042AH. It incorporates 4K bytes of ROM as compared to the standard 2K byte amount to support additional firmware desired for advanced keyboard BIOS functions. A full 256 bytes of RAM are available for scratchpad storage. Nine programmable I/O lines support necessary dedicated control functions.

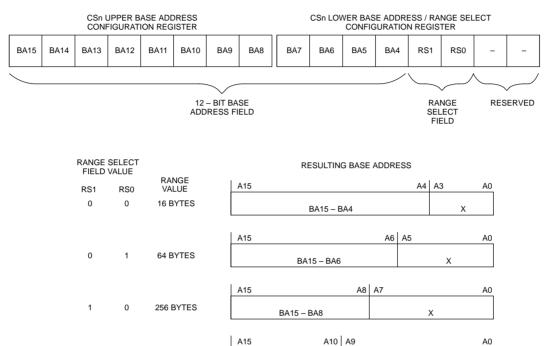

Two general purpose chip select pins can each be programmed to select a range of 16, 64, 256, or 1K bytes from any base ISA address that falls on a range boundary. Twelve general purpose I/O port pins are available that can be located to any even-byte boundary within the 64K byte ISA map.

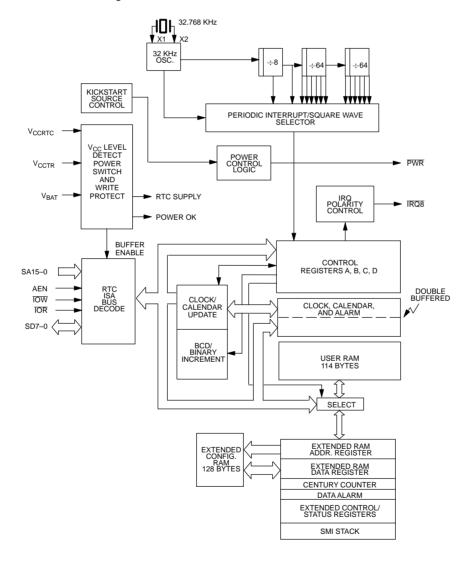

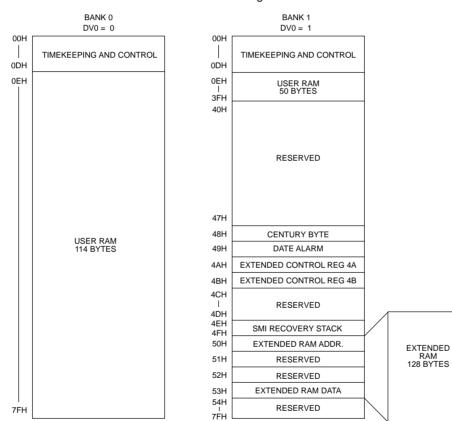

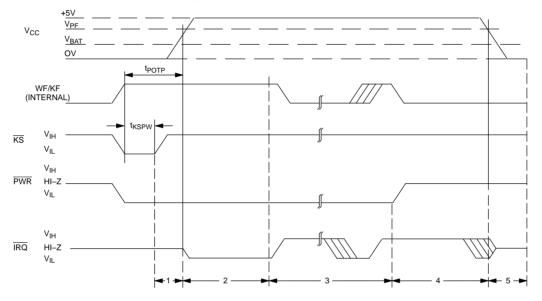

The real time clock is fully compatible with the DS1685 and supplies 242 bytes of configuration RAM. The RTC also provides advanced power control circuitry for soft power on by an external stimulus (kickstart) or by a time and date alarm (wake–up). The RTC's kickstart source can be a switch closure on the KBC P16 pin, a modem ring on UART A or B, infrared input activity on the IRRX pin, or a combination of the above. An independent supply pin powers the RTC that allows power down of the rest of chip along with the motherboard. This makes it possible to power the kickstart and wake up circuitry from a small trickle supply source while the main supply, and the rest of the system, are powered down.

In addition to the soft power on feature described above, the DS83CH20 supports individual power down of all devices with system power applied. This allows power down of an on-chip device during periods of inactivity. When enabled, an auto power down feature intelligently detects inactivity of selected on-chip devices and automatically removes power without software intervention. As an option, a device's inputs are disabled and its output pins placed in a high-Z condition whenever that device is powered down.

030598 2/185

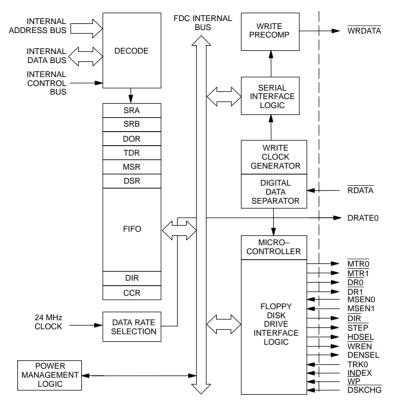

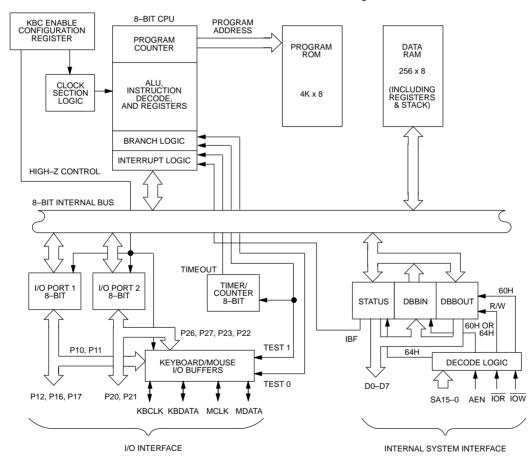

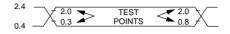

#### DS83CH20 BLOCK DIAGRAM Figure 1-1

# 1.2 DS83CH20 DETAILED FEATURE SUMMARY

#### ISA Bus Interface

- Direct interface to ISA bus

- All address decoding performed on-chip

- All 16 address lines decoded for all internal functions

- X–Bus buffer for BIOS memory interface (10 pins)

#### Real Time Clock

- DS12885, DS1685 compatible clock/calendar

- Calendar: day, date, months, years with leap year compensation

- Time: seconds, minutes, hours; 12–or 24–hour format

- Supports daylight savings time adjustment

- 242 bytes NV configuration RAM

- System wake-up and date alarms

- On-chip crystal oscillator

- < 1 μA battery backup current</li>

#### Keyboard Controller

- 8042AH software compatible

- 4K ROM for program storage

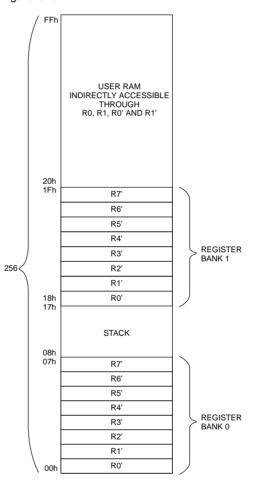

- 256 bytes data RAM

- Asynchronous access to two data registers and one status register

- Power saving modes

- Supports interrupt and polled access

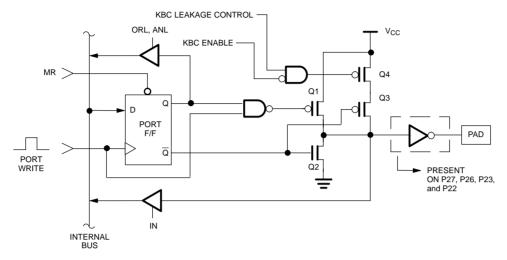

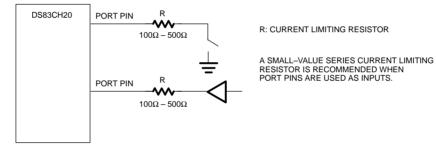

- Four dedicated open-drain bi-directional pins

- 10 programmable I/O pins

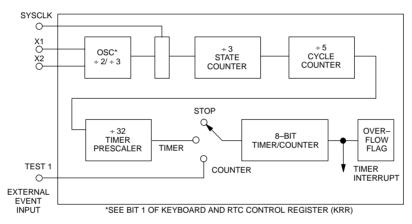

- 8-bit timer/counter

#### • Floppy Disk Controller

- 82077SL software compatible

- PC-AT and PS/2 operating modes

- High performance digital data separator

- Data rates up to 1 Mbps

- Perpendicular recording format support

- Low power CMOS with power down modes

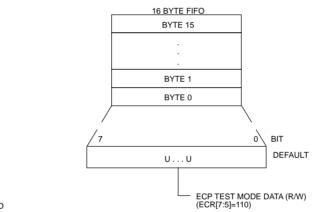

- 16 byte FIFO

#### • UARTs (2)

- 16550A software compatible

- 16-byte send/receive FIFO's

- Programmable baud rate generator

- Supports 115.2K baud

#### • Infrared I/O

- Supported via UART 2

- Transmit / receive for IRDA 1.0 and Sharp ASK

#### • IEEE 1284 Parallel Port

- Enhanced Parallel Port (EPP) compatible

- Extended Capabilities (ECP) compatible, including level 2 support

- Compatible with ISA, EISA, and Micro Channel architectures

- Includes protection circuit against damage caused when printer is powered up

#### • General Purpose Pins

- 12 general purpose I/O pins programmable as input / output or isolated

- Two general purpose chip select outputs

#### • Plug and Play Support

- Meets Microsoft PC'95 requirements

- Supports two address locations for FDC

- Supports 256 base address location for UARTs and Parallel Port

- Supports any even byte boundary base address locations for GP I/O

- Supports 16, 64, 256, or 1K byte range select for programmable chip selects on any range byte boundary

- Ten IRQ options for FDC, UARTs and Parallel Port

- Four DMA options for FDC and Parallel Port

#### Power Management

- Ability to power down individual modules

- Intelligent auto power management available to all modules

- Optional input disable and output high–Z on power down

- Full chip power down mode

- "Kickstart" soft power on from button, modem ring, or IR detect

- Wake-up on time, date

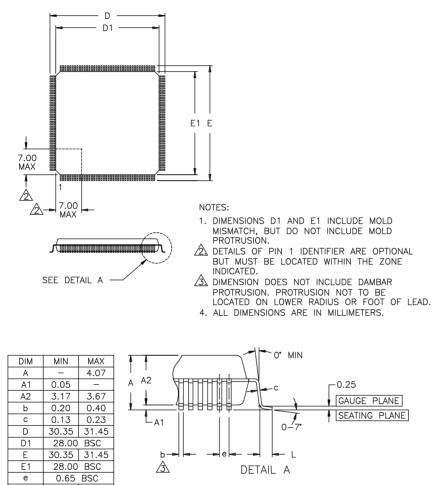

#### • 160-pin QFP package

030598 4/185

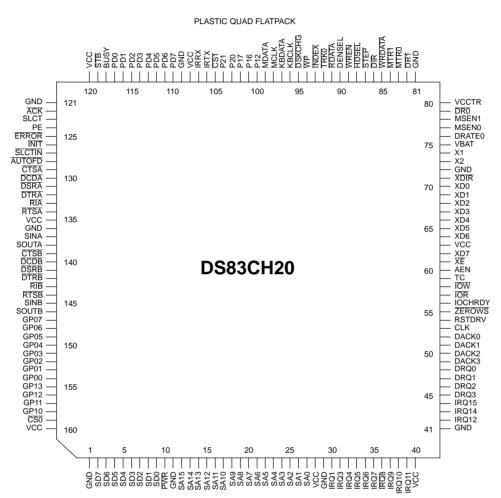

### 2.0 PIN CONFIGURATION

030598 5/185

# 2.1 PIN SUMMARY

Listed in the tables below are a summary of all of the pin functions for the DS83CH20.

| SYMBOL          | PIN                                      | TYPE | FUNCTION                                                                                                                                                                                          |

|-----------------|------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

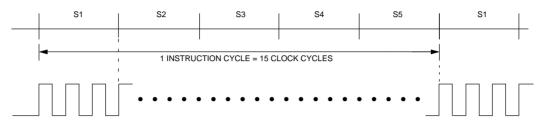

| CLK             | 53                                       | I    | <b>Clock Input.</b> This input should be connected to the 48 or 24 MHz system clock source. Frequency selection is made via the XD7 signal on reset; XD7 low selects 48 MHz; high selects 24 MHz. |

| GND             | 1,11,29,<br>41,72,81,<br>109,121,<br>136 | -    | <b>Digital Ground.</b> Connections for ground.<br>NOTE: All GND pins must be connected to ground.                                                                                                 |

| V <sub>CC</sub> | 28,40,63,<br>108,120,<br>135,160         | I    | <b>Digital Supply Voltage.</b> +5V supply voltage.<br>NOTE: All $V_{CC}$ pins must be connected to +5V supply voltage.                                                                            |

# CHIP LEVEL PIN SUMMARY Table 2–1

# ISA BUS PIN SUMMARY Table 2–2

| SYMBOL              | PIN                       | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                              |

|---------------------|---------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

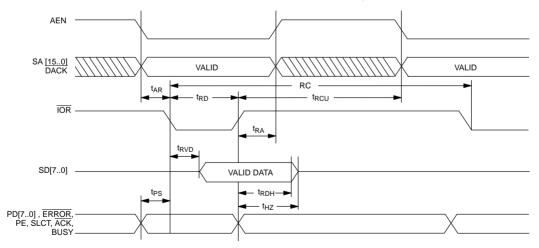

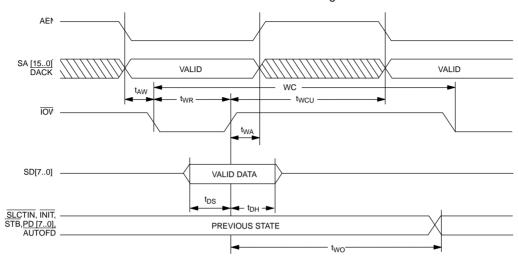

| AEN                 | 60                        | I    | Address Enable. This input disable function selection via SA15–SA0 when it is high. Access during DMA transfer is NOT affected by this pin.                                                                                                                                                                           |

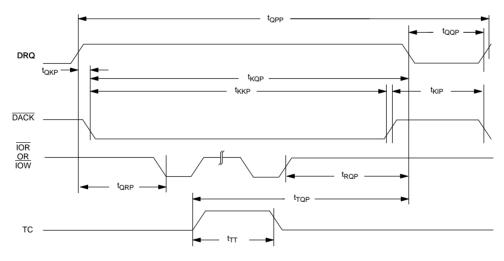

| DACK30              | 49–52                     | I    | <b>DMA Acknowledge Inputs.</b> These pins are used to acknowledge DMA requests and to enable the IOR and IOW lines during DMA transfers to the FDC or Parallel Port. These two devices can be assigned to any of the DMA channels via the configuration registers.                                                    |

| DRQ30               | 45–48                     | 0    | <b>DMA Request Outputs.</b> These pins are used to signal DMA service requests from the FDC and the Parallel Port. These two devices can be assigned to any of the DMA channels via the configuration registers. Unselected DRQ's will remain in a High–Z condition.                                                  |

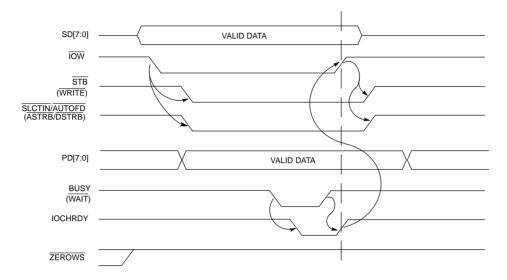

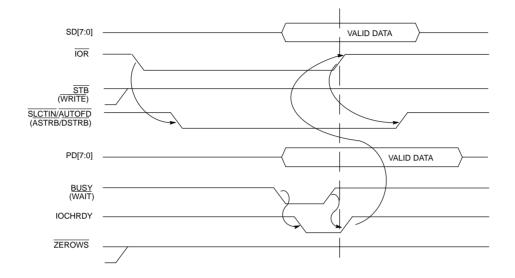

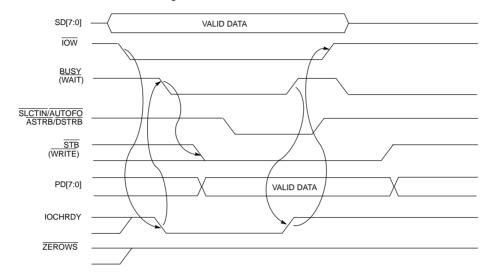

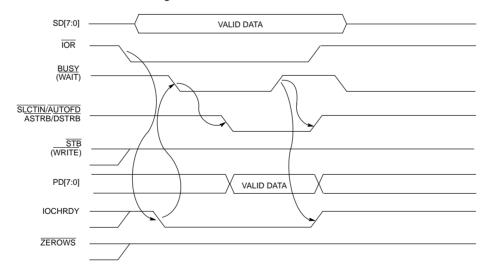

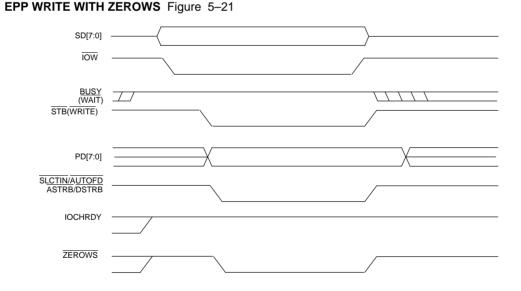

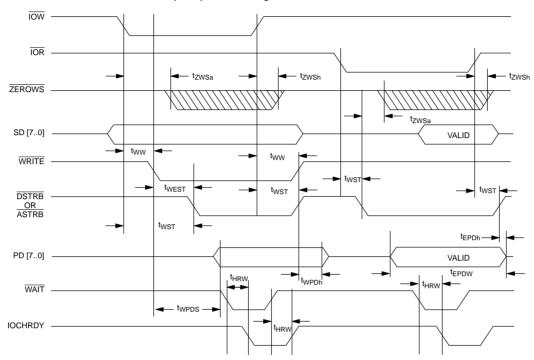

| IOCHRDY             | 56                        | 0    | <b>I/O Channel Ready.</b> When this signal is driven low and EPP mode is selected, the parallel port extends the ISA bus cycle. IOCHRDY is an open–drain output.                                                                                                                                                      |

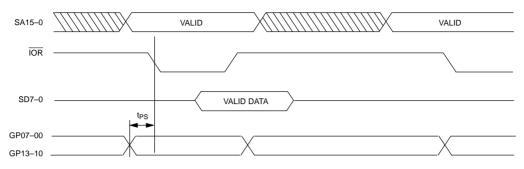

| IOR                 | 57                        | I    | I/O Read. Active low input to signal a data read by the microprocessor.                                                                                                                                                                                                                                               |

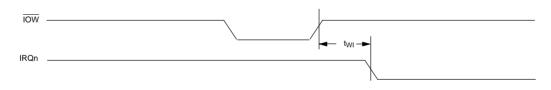

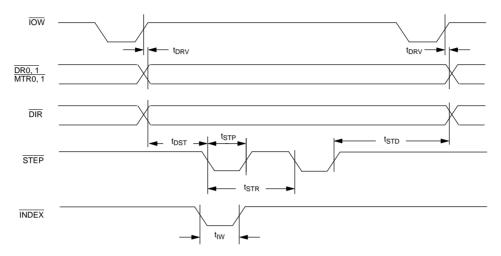

| ĪOW                 | 58                        | I    | Write. Active low input to signal an I/O write from the ISA bus.                                                                                                                                                                                                                                                      |

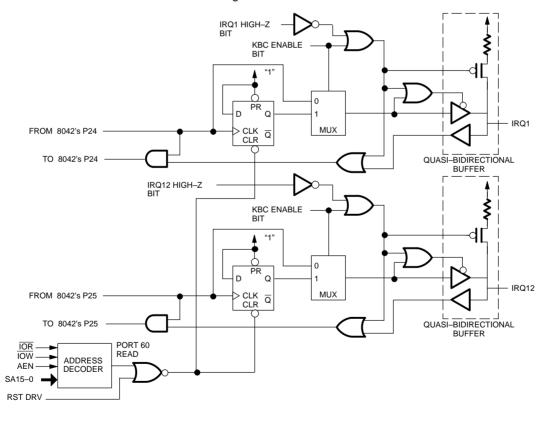

| IRQ1                | 30                        | I/O  | Interrupt Request 1. This pin is assigned as the keyboard interrupt gener-<br>ated from the internal P24 line of the Keyboard Controller.                                                                                                                                                                             |

| IRQ37,<br>911, 1415 | 31–35,<br>37–39,<br>43–44 | 0    | <b>Interrupt Request Outputs.</b> These interrupt outputs are used to signal interrupt requests from the on chip devices. The interrupt sources from the FDC, Parallel Port, and UARTs can be assigned via the configuration registers to any of these IRQ lines. Unselected IRQ's will remain in a High–Z condition. |

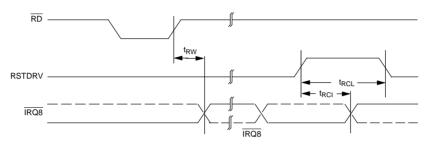

| IRQ8                | 36                        | 0    | <b>Interrupt Request 8.</b> This pin is assigned as the Real Time Clock interrupt request output. The polarity of $\overline{IRQ8}$ can be changed to active high via the configuration registers. $\overline{IRQ8}$ is in a High–Z state whenever the RTC is disabled.                                               |

030598 6/185

| SYMBOL    | PIN   | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ12     | 42    | I/O  | Interrupt Request 12. This pin is assigned as the mouse interrupt gener-<br>ated from internal P25 of the Keyboard Controller.                                                                                                                                                                                                                                                                          |

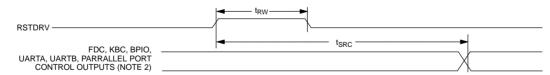

| RSTDRV    | 54    | I    | <b>Master Reset.</b> Active high input resets the floppy disk controller to the idle state, and resets all disk interface outputs to their inactive states. The DOR, DSR, CCR, Mode command, Configure command, and Lock command parameters are cleared to their default values. The Specify command parameters are not affected. The Configuration Registers are set to their selected default values. |

| SA[15,,0] | 12–27 | I    | <b>System Address.</b> These system address lines determine which internal DS83CH20 register is addressed. 16–bit decoding on all internal register is implemented. SA15–SA0 are don't cares during a DMA transfer.                                                                                                                                                                                     |

| SD[70]    | 2–9   | I/O  | <b>System Data.</b> Bi–directional system data bus. D0 is the LSB and D7 is the MSB. These signals all have 12 mA (sink) buffered outputs.                                                                                                                                                                                                                                                              |

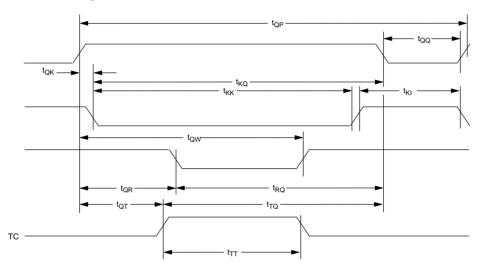

| TC        | 59    | I    | <b>Terminal Count.</b> Control signal from the DMA controller to indicate the termination of a DMA transfer. TC is accepted only when an assigned DMA channel is active. TC is active high in PC–AT mode, and active low in PS/2 mode.                                                                                                                                                                  |

| ZEROWS    | 55    | 0    | <b>Zero Wait State.</b> This pin is the Zero Wait State open drain output pin. ZEROWS is driven low when the EPP or ECP is written and the access can be shortened.                                                                                                                                                                                                                                     |

### FLOPPY DISK PIN SUMMARY Table 2–3

| SYMBOL   | PIN   | TYPE | FUNCTION                                                                                                                                                                                                                         |

|----------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DENSEL   | 90    | 0    | <b>FDC Density Select.</b> Indicates that a high FDC density data rate (500 Kbps or 1 Mbps) or a low density data rate (250 or 300 Kbps) is selected. DENSEL's polarity is controlled via the FDC Mode Configuration Register.   |

| DIR      | 86    | 0    | <b>FDC Direction.</b> This output determines the direction of the floppy disk drive head movement (low = step in, high = step out) during a seek operation. During reads or writes, DIR is inactive.                             |

| DR0, DR1 | 79,82 | 0    | <b>FDC Drive Select 0, 1.</b> These are the decoded drive select outputs that are controlled by the Digital Output Register bits D0, D1. The Drive Select outputs are gated with DOR bits 4–7. These are active low outputs.     |

| DRATE0   | 76    | 0    | <b>FDC Data Rate 0.</b> This output reflects the currently selected FDC data rate, as determined by the setting of the Configuration Control Register (CCR) or the Data Rate Select Register (DSR), which ever was written last. |

| DSKCHG   | 95    | I    | <b>FDC Disk Change.</b> This input indicates if the drive door has been opened. The state of this pin is available from the Digital Input Register.                                                                              |

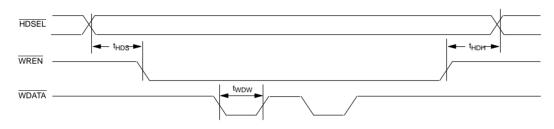

| HDSEL    | 88    | 0    | <b>FDC Head Select.</b> This output determines which side of the FDD is accessed. A low output selects side 1, a high output selects side 0.                                                                                     |

| INDEX    | 93    | I    | <b>FDC Index.</b> A high to low transition on this input signals the beginning of a FDC track.                                                                                                                                   |

| MSEN0,1  | 77,78 | I    | Media Sense. FDC Media Sense inputs.                                                                                                                                                                                             |

| SYMBOL | PIN    | TYPE | FUNCTION                                                                                                                                                                                                                               |

|--------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MTR0,1 | 83, 84 | 0    | <b>FDC Motor Select 0, 1.</b> These are the motor enable lines for drives 0 and 1, and are controlled by bits D7–D4 of the Digital Output register. They are active low outputs.                                                       |

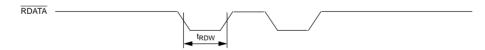

| RDATA  | 91     | I    | FDC Read Data. This input is the raw serial data read from the floppy disk drive.                                                                                                                                                      |

| STEP   | 87     | 0    | <b>FDC Step.</b> This output signal issues pulses to the disk drive at a software programmable rate to move the head during a seek operation.                                                                                          |

| TRKO   | 92     | I    | <b>FDC Track 0.</b> A low level on this input indicates to the controller that the head of the selected floppy disk drive is at track 0.                                                                                               |

| WP     | 94     | I    | <b>FDC Write Protect.</b> This input indicates that the disk in the selected drive is write–protected.                                                                                                                                 |

| WRDATA | 85     | 0    | <b>FDC Write Data.</b> This output is the write precompensated serial data that is written to the selected floppy disk drive. Precompensation is software selectable.                                                                  |

| WREN   | 89     | 0    | <b>FDC Write Enable.</b> This output signal enables the write circuitry of the selected disk drive. WREN has been designed to prevent glitches during power up and power down. This prevents writing to the disk when power is cycled. |

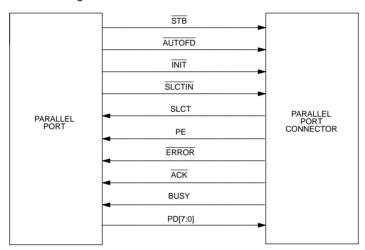

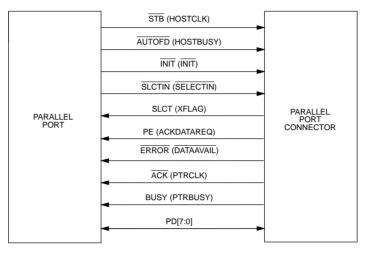

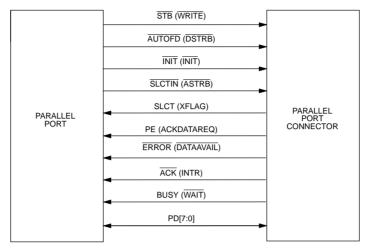

### PARALLEL PORT PIN SUMMARY Table 2-4

| SYMBOL            | PIN     | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

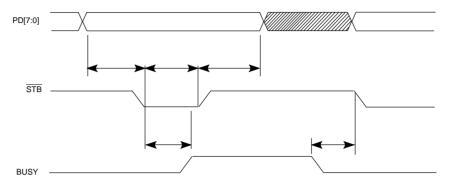

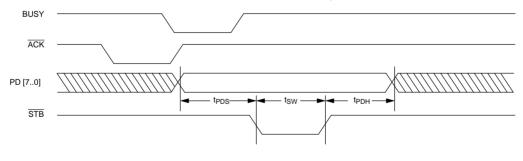

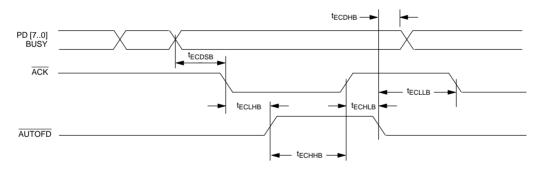

| ACK               | 122     | I    | <b>Parallel Port Acknowledge.</b> This input is pulsed low by the printer to indicate that it has received data from the parallel port.                                                                                                                                                                                                                             |

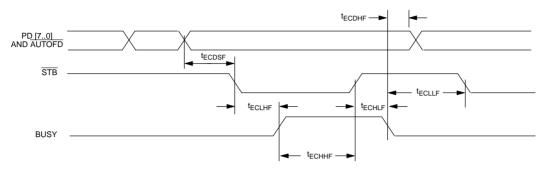

| AUTOFD /<br>DSTRB | 128     | 0    | <b>Parallel Port Automatic Feed/EPP Data Strobe.</b> In SPP mode, this pin is the AFD signal. When low, it indicates to the printer that it should automatically line feed after each line is printed. In EPP mode, this pin is the active low DSTRB signal. This pin is in High–Z condition 10 ns after a 0 is loaded into the corresponding Control Register bit. |

| BUSY /<br>WAIT    | 118     | I    | <b>Parallel Port Busy/EPP Wait.</b> In SPP mode, this pin serves as the BUSY input and will be set high by the printer when it cannot accept another character. In EPP mode, this pin is the WAIT input and is used by the parallel port device to extend its access cycle.                                                                                         |

| ERROR             | 125     | I    | Parallel Port Error. This input is set low by the printer when it has detected an error.                                                                                                                                                                                                                                                                            |

| ĪNIT              | 126     | 0    | <b>Initialize.</b> When this signal is low it causes the printer to be initialized. This pin is in a High–Z condition 10 ns after a 1 is loaded into the corresponding Control Register bit.                                                                                                                                                                        |

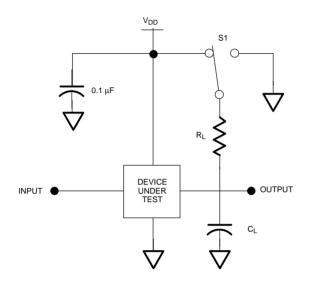

| PD[70]            | 110–117 | I/O  | <b>Parallel Port Data.</b> These bidirectional pins transfer data to and from the peripheral data bus and the parallel port Data Register. These pins have high current drive capability (see DC Electrical Characteristics).                                                                                                                                       |

| PE                | 124     | I    | <b>Parallel Port Paper End.</b> This input is set high by the printer when it is out of paper.                                                                                                                                                                                                                                                                      |

| SYMBOL            | PIN | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLCT              | 123 | I    | Parallel Port Select. This input is set high by the printer when it is selected.                                                                                                                                                                                                                                                                                 |

| SLCTIN /<br>ASTRB | 127 | 0    | <b>Parallel Port Select Input/EPP Address Strobe.</b> In SPP mode, this pin is <u>SLCTIN</u> , and selects the printer when it is low. In EPP mode, this pin is <u>ASTRB</u> , which is used as an active low address strobe. This pin is in High–Z condition 10 ns after a 0 is loaded into the corresponding Control Register bit.                             |

| STB/ WRITE        | 119 | 0    | <b>Parallel Port Data Strobe/EPP Write Strobe.</b> In SPP mode, this pin functions as the STB active low output to indicate to the printer that valid data is available at the printer port. In EPP mode, this pin serves as the WRITE active low output. This pin is in High–Z condition 10 ns after a 0 is loaded into the corresponding Control Register bit. |

# UARTS PIN SUMMARY Table 2–5

| SYMBOL        | PIN      | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTSA,<br>CTSB | 129, 139 | I    | <b>UARTs Clear to Send.</b> When low, this signal indicates that the modem or data set is ready to exchange data. The $\overline{CTS}$ signal is a modem status input whose condition the CPU can test by reading bit 4 (CTS) of the Modem Status Register (MSR) for the appropriate serial channel. Bit 4 is the complement of the $\overline{CTS}$ signal. Bit 0 (DCTS) of MSR indicates whether the $\overline{CTS}$ input has changed state since the previous reading of MSR. $\overline{CTS}$ has no effect on the transmitter. Whenever the DCTS bit of the MSR is set, an interrupt is generated if Modem Status interrupts are enabled. |

| DCDA,<br>DCDB | 130, 140 | Ι    | <b>UARTS Data Carrier Detect.</b> When low, this signal indicates that the modem or data set has detected the carrier. The DCD signal is a modem status input whose condition the CPU can test by reading bit 7 (DCD) of the Modem Status Register (MSR) for the appropriate serial channel. Bit 7 is the complement of the DCD signal. Bit 3 (DDCD) of MSR indicates either the DCD input has changed state since the previous reading of MSR. Whenever the DDCD bit of the MSR is set, an interrupt is generated if Modem Status interrupts are enabled.                                                                                       |

| DSRA,<br>DSRB | 131, 141 | Ι    | <b>UARTS Data Set Ready.</b> When low, this signal indicates that the modem or data set is ready to establish a communications link. The $\overline{\text{DSR}}$ signal is a modem status input whose condition the CPU can test by reading bit 5 (DSR) of the Modem Status Register (MSR) for the appropriate serial channel. Bit 5 is the complement of the $\overline{\text{DSR}}$ signal. Bit 1 (DDSR) of MSR indicates whether the $\overline{\text{DSR}}$ input has changed state since the previous reading of MSR. Whenever the DDSR bit of the MSR is set, an interrupt is generated if Modem Status interrupts are enabled.            |

| DTRA,<br>DTRB | 132, 142 | 0    | <b>UARTS Data Terminal Ready.</b> When low, this signal indicates to the modem or data set that the UART is ready to establish a communications link. The DTR signal can be set to an active low by programming bit 0 (DTR) of the Modem Control Register to a high level. A Master Reset operation sets this signal to its inactive (high) state. Loop mode operation holds this signal to its inactive state.                                                                                                                                                                                                                                  |

| SYMBOL          | PIN      | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RIA, RIB        | 133, 143 | I    | <b>UARTS Ring Indicator.</b> When low this signal indicates that a telephone ring signal has been received by the modem. The RI signal is a modem status input whose condition the CPU can test by reading bit 6 (RI) of the Modem Status Register (MSR) for the appropriate serial channel. Bit 6 is the complement of the RI signal. Bit 2 (TERI) of MSR indicates whether the RI input has changed state since the previous reading of MSR. Whenever the TERI bit of the MSR is set, an interrupt is generated if Modem Status interrupts are enabled. |

| RTSA,<br>RTSB   | 134,144  | 0    | <b>UARTs Request to Send.</b> When low, this signal indicates to the modem or data set that the UART is ready exchange data. The RTS signal can be set to an active low by programming bit 1 (RTS) of the Modem Control register to a high level. A master reset sets this signal to its inactive (high) state. Loop mode operation holds this signal to its inactive state.                                                                                                                                                                              |

| SINA, SINB      | 137,145  | I    | <b>UARTs Serial Input.</b> This input receives composite serial data from the communications link (peripheral device, modem, or data set).                                                                                                                                                                                                                                                                                                                                                                                                                |

| SOUTA,<br>SOUTB | 138, 146 | 0    | <b>UARTs Serial Output</b> . This output sends composite serial data to the communications link (peripheral device, Modem, or data set). This OUT signal is set to a marking state (logic 1) after a Master Reset operation. If test mode is selected, this pin provides the associated serial channel baud rate generator output signal.                                                                                                                                                                                                                 |

# **INFRARED PIN SUMMARY** Table 2–6

| SYMBOL | PIN | TYPE | FUNCTION              |

|--------|-----|------|-----------------------|

| IRRX   | 107 | I    | Infrared Receiver.    |

| IRTX   | 106 | 0    | Infrared Transmitter. |

# REAL TIME CLOCK PIN SUMMARY Table 2–7

| SYMBOL           | PIN | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWR              | 10  | 0    | <b>Power On Output; open drain.</b> The $\overline{\text{PWR}}$ pin is intended for use as an on/off control for the system power. With V <sub>CC</sub> voltage removed from the DS83CH20, $\overline{\text{PWR}}$ may be automatically activated from a kickstart input via the P16 / Kickstart pin, from an RTC Wake–up interrupt, from RIA, RIB, or IRRX. |

| V <sub>BAT</sub> | 75  | I    | <b>Battery.</b> Real Time Clock battery input pin. Connects to any standard 3–Volt lithium cell or other energy source. Battery voltage must be held between 2.5 and 3.7 volts for proper operation.                                                                                                                                                         |

030598 10/185

| SYMBOL            | PIN    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCTR</sub> | 80     | I    | <b>Trickle Supply Voltage.</b> Independent power supply input required to power the wake–up circuitry and all enabled kickstart inputs in the full–chip power down mode. This supply input also powers clock/calendar and RTC configuration RAM as long as $V_{CCTR}$ voltage $\geq V_{BAT}$ voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| X1, X2.           | 74, 73 | Ι    | 32 KHz Crystal Inputs. Connections for a standard 32.768 KHz crystal for<br>the on-chip real time clock. For greatest accuracy, the DS83CH20 must<br>be used with a crystal that has a specified load capacitance of either six pF<br>or 12.5 pF. The Crystal Select (CS) bit in Extended Control Register 4B is<br>used to select operation with a six pF or 12.5 pF crystal. The crystal is<br>attached directly to the X1 and X2 pins. There is no need for external<br>capacitors or resistors. Note: X1 and X2 are very high impedance nodes. It<br>is recommended that they and the crystal by guard-ringed with ground and<br>that high frequency signals be kept away from the crystal area.For more information on crystal selection and crystal layout consider-<br>ations, please consult Application Note 58, "Crystal Considerations with<br>Dallas Real Time Clocks". The DS83CH20 can also be driven by an exter-<br>nal 32.768 KHz oscillator. In this configuration, the X1 pin is connected to<br>the external oscillator signal and the X2 pin is floated. |

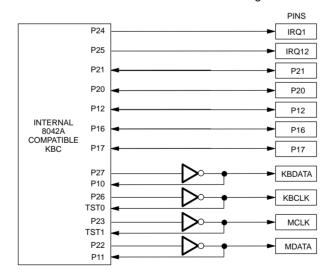

# KEYBOARD CONTROLLER PIN SUMMARY Table 2–8

| SYMBOL                         | PIN     | TYPE | FUNCTION                                                                                                                                                                               |

|--------------------------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KBCLK                          | 96      | I/O  | Keyboard Clock Output. Internally connected to the KBC's T0 line.                                                                                                                      |

| KBDATA                         | 97      | I/O  | Keyboard Data Output. Internally connected to the KBC's P10 line.                                                                                                                      |

| MCLK                           | 98      | I/O  | Mouse Clock Output. Internally connected to the KBC's T1 line.                                                                                                                         |

| MDATA                          | 99      | I/O  | Mouse Data Output. Internally connected to the KBC's P11 line.                                                                                                                         |

| P1 <u>2,</u><br>P16/KS,<br>P17 | 100–102 | I/O  | <b>KBC I/O Port 1.</b> Quasi–bidirectional port for general purpose input and output. P16 can be programmed to serve the alternate function of a kickstart soft system power on input. |

| P20, P21                       | 103–104 | I/O  | KBC I/O Port 2. Open drain port for general input/output.                                                                                                                              |

### GENERAL PURPOSE I/O PIN SUMMARY Table 2-9

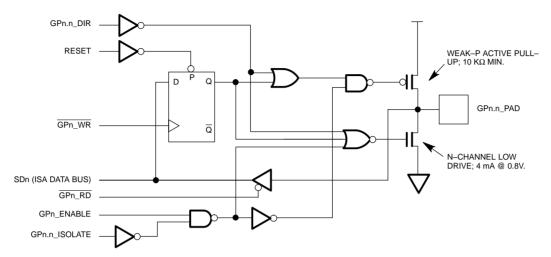

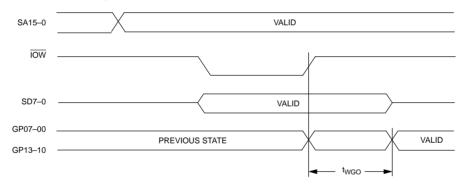

| SYMBOL  | PIN     | TYPE | FUNCTION                                                                                                                                                                                      |

|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0[70] | 147–154 | I/O  | <b>General Purpose I/O.</b> General Purpose I/O pin of I/O Port 0. These pins can be independently programmed as inputs or outputs, and can be individually isolated under software control.  |

| GP1[30] | 155–158 | I/O  | <b>General Purpose I/O.</b> General Purpose I/O pins of I/O Port 1. These pins can be independently programmed as inputs or outputs, and can be individually isolated under software control. |

### PROGRAMMABLE CHIP SELECT PIN SUMMARY Table 2–10

| SYMBOL   | PIN      | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                 |

|----------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

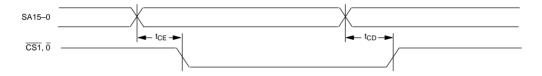

| CSO, CS1 | 159, 105 | 0    | <b>Programmable Chip Selects.</b> CS0 and CS1 are programmable chip select and/or latch enable and/or output enable signals that can be used for such devices as a game port, I/O port expander, etc. The enabling/ disabling, decoded address, and the assertion conditions are configured via the chip select configuration registers. |

| SYMBOL | PIN   | TYPE | FUNCTION                                                                                                                                                                                                                                                                                      |

|--------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XD[60] | 64–70 | I/O  | <b>X–Bus Data I/O.</b> Provides a buffered interface between the System Data Bus (SD6–0) and devices on the X–Bus.                                                                                                                                                                            |

| XD7    | 62    | I/O  | <b>X–Bus Data I/O.</b> Provides a buffered interface between the System Data Bus (SD7–0) and devices on the X–Bus. The frequency required for the CLK input is determined by the XD7 pin on reset; XD7 low selects 48 MHz; high selects 24 MHz.                                               |

| XDIR   | 71    | I    | <b>X–Bus Direction.</b> Used to control the data direction for transfers between the System Data Bus (SD7–0) and an external device on the X–Bus. A logic "1" on this pin sets the data direction for a write of data from SD7–0 to the X–bus, while a logic "0" sets the direction for read. |

| XE     | 61    | I    | <b>X–Bus Enable.</b> Used to enable a data transfer between the System Data Bus (SD7–0) and an external device on the X–Bus.                                                                                                                                                                  |

# X-BUS BUFFER PIN SUMMARY Table 2-11

# 2.2 PIN CHARACTERISTICS

Listed in the Table 2–12 is a summary of the pin characteristics. For each pin the table lists the functional block that it is associated with and the I/O buffer type field that describes the I/O buffer structure that is associated with the pin. An explanation of the I/O buffer type field is given in the notes section at the end of the table. Finally, the state of the pin during a reset state (RSTDRV=1) is given.

| PIN CHARACTERISTICS Table 2–12 |

|--------------------------------|

|--------------------------------|

| PIN | NAME | FUNCTIONAL BLOCK | I/O BUFFER TYPE | RESET STATE |

|-----|------|------------------|-----------------|-------------|

| 1   | GND  |                  |                 |             |

| 2   | SD7  | ISA I/F          | I/O12–6         | High–Z      |

| 3   | SD6  | ISA I/F          | I/O12–6         | High–Z      |

| 4   | SD5  | ISA I/F          | I/O12–6         | High–Z      |

| 5   | SD4  | ISA I/F          | I/O12–6         | High–Z      |

| 6   | SD3  | ISA I/F          | I/O12–6         | High–Z      |

| 7   | SD2  | ISA I/F          | I/O12–6         | High–Z      |

| 8   | SD1  | ISA I/F          | I/O12–6         | High–Z      |

| 9   | SD0  | ISA I/F          | I/O12–6         | High–Z      |

| 10  | PWR  | PWR CTRL         | OD12            | Unchanged   |

| 11  | GND  |                  |                 |             |

| 12  | SA15 | ISA I/F          | I               | Enabled     |

| 13  | SA14 | ISA I/F          | I               | Enabled     |

| 14  | SA13 | ISA I/F          | I               | Enabled     |

| 15  | SA12 | ISA I/F          | I               | Enabled     |

| 16  | SA11 | ISA I/F          | I               | Enabled     |

| 17  | SA10 | ISA I/F          | I               | Enabled     |

| 18  | SA9  | ISA I/F          | I               | Enabled     |

030598 12/185

| PIN | NAME            | FUNCTIONAL BLOCK | I/O BUFFER TYPE            | RESET STATE |

|-----|-----------------|------------------|----------------------------|-------------|

| 19  | SA8             | ISA I/F          | I                          | Enabled     |

| 20  | SA7             | ISA I/F          | I                          | Enabled     |

| 21  | SA6             | ISA I/F          | I                          | Enabled     |

| 22  | SA5             | ISA I/F          | I                          | Enabled     |

| 23  | SA4             | ISA I/F          | I                          | Enabled     |

| 24  | SA3             | ISA I/F          | I                          | Enabled     |

| 25  | SA2             | ISA I/F          | I                          | Enabled     |

| 26  | SA1             | ISA I/F          | I                          | Enabled     |

| 27  | SA0             | ISA I/F          | I                          | Enabled     |

| 28  | V <sub>CC</sub> |                  |                            | +5V         |

| 29  | GND             |                  |                            |             |

| 30  | IRQ1            | ISA I/F          | I/O4–PB2/10K               | High        |

| 31  | IRQ3            | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 32  | IRQ4            | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 33  | IRQ5            | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 34  | IRQ6            | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 35  | IRQ7            | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 36  | IRQ8            | ISA I/F          | O12–6<br>(see note 1)      | Low         |

| 37  | IRQ9            | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 38  | IRQ10           | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 39  | IRQ11           | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 40  | V <sub>CC</sub> |                  |                            | +5V         |

| 41  | GND             |                  |                            |             |

| 42  | IRQ12           | ISA I/F          | I/O4–PB2/10K               | High        |

| 43  | IRQ14           | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

| 44  | IRQ15           | ISA I/F          | O12–6/OD12<br>(see note 1) | High–Z      |

030598 13/185

| PIN | NAME             | FUNCTIONAL BLOCK | I/O BUFFER TYPE | RESET STATE |

|-----|------------------|------------------|-----------------|-------------|

| 45  | DRQ3             | ISA I/F          | O12–6           | High–Z      |

| 46  | DRQ2             | ISA I/F          | O12–6           | High–Z      |

| 47  | DRQ1             | ISA I/F          | O12–6           | High–Z      |

| 48  | DRQ0             | ISA I/F          | O12–6           | High–Z      |

| 49  | DACK3            | ISA I/F          | I               | Enabled     |

| 50  | DACK2            | ISA I/F          | I               | Enabled     |

| 51  | DACK1            | ISA I/F          | I               | Enabled     |

| 52  | DACK0            | ISA I/F          | I               | Enabled     |

| 53  | CLK              | CLOCK            | ICLK            | Enabled     |

| 54  | RSTDRV           | ISA I/F          | IS              | High        |

| 55  | ZEROWS           | ISA I/F          | OD12            | High–Z      |

| 56  | IOCHRDY          | ISA I/F          | OD12            | High–Z      |

| 57  | IOR              | ISA I/F          | I               | Enabled     |

| 58  | IOW              | ISA I/F          | I               | Enabled     |

| 59  | тс               | ISA I/F          | I               | Enabled     |

| 60  | AEN              | ISA I/F          | I               | Enabled     |

| 61  | XE               | X BUFFER         | I               | Enabled     |

| 62  | XD7              | X BUFFER         | I/O4–2          | High–Z      |

| 63  | V <sub>CC</sub>  |                  |                 | +5V         |

| 64  | XD6              | X BUFFER         | I/O4–2          | High–Z      |

| 65  | XD5              | X BUFFER         | I/O4–2          | High–Z      |

| 66  | XD4              | X BUFFER         | I/O4–2          | High–Z      |

| 67  | XD3              | X BUFFER         | I/O4–2          | High–Z      |

| 68  | XD2              | X BUFFER         | I/O4–2          | High–Z      |

| 69  | XD1              | X BUFFER         | I/O4–2          | High–Z      |

| 70  | XD0              | X BUFFER         | I/O4–2          | High–Z      |

| 71  | XDIR             | X BUFFER         | I               | Enabled     |

| 72  | GND              |                  |                 |             |

| 73  | X2               | RTC              | IOSC            | Enabled     |

| 74  | X1               | RTC              | IOSC            | Enabled     |

| 75  | V <sub>BAT</sub> | RTC              |                 | +3V         |

| 76  | DRATE0           | FLOPPY           | OD40            | High–Z      |

| 77  | MSEN0            | FLOPPY           | IS              | Enabled     |

030598 14/185

| PIN | NAME              | FUNCTIONAL BLOCK | I/O BUFFER TYPE | RESET STATE |

|-----|-------------------|------------------|-----------------|-------------|

| 78  | MSEN1             | FLOPPY           | IS              | Enabled     |

| 79  | DR0               | FLOPPY           | OD40            | High–Z      |

| 80  | V <sub>CCTR</sub> |                  |                 | +5V         |

| 81  | GND               |                  |                 |             |

| 82  | DR1               | FLOPPY           | OD40            | High–Z      |

| 83  | MTR0              | FLOPPY           | OD40            | High–Z      |

| 84  | MTR1              | FLOPPY           | OD40            | High–Z      |

| 85  | WRDATA            | FLOPPY           | OD40            | High–Z      |

| 86  | DIR               | FLOPPY           | OD40            | High–Z      |

| 87  | STEP              | FLOPPY           | OD40            | High–Z      |

| 88  | HDSEL             | FLOPPY           | OD40            | High–Z      |

| 89  | WREN              | FLOPPY           | OD40            | High–Z      |

| 90  | DENSEL            | FLOPPY           | OD40            | High–Z      |

| 91  | RDATA             | FLOPPY           | IS              | Enabled     |

| 92  | TRK0              | FLOPPY           | IS              | Enabled     |

| 93  | INDEX             | FLOPPY           | IS              | Enabled     |

| 94  | WP                | FLOPPY           | IS              | Enabled     |

| 95  | DSKCHG            | FLOPPY           | IS              | Enabled     |

| 96  | KBCLK             | KBC              | I/OD16–P10K     | Low         |

| 97  | KBDATA            | КВС              | I/OD16–P10K     | Low         |

| 98  | MCLK              | KBC              | I/OD16–P10K     | Low         |

| 99  | MDATA             | КВС              | I/OD16–P10K     | Low         |

| 100 | P12               | КВС              | I/O4–PB2/10K    | High        |

| 101 | P16               | KBC              | I/O4–PB2/10K    | High        |

| 102 | P17               | КВС              | I/O4–PB2/10K    | High        |

| 103 | P20               | KBC              | I/O4–PB2/10K    | High        |

| 104 | P21               | KBC              | I/O4–PB2/10K    | High        |

| 105 | CS1               | CHIP SELECT      | O4–2            | High–Z      |

| 106 | IRTX              | IR PORT          | O4–2            | Low         |

| 107 | IRRX              | IR PORT          | IS              | Enabled     |

| 108 | V <sub>CC</sub>   |                  |                 | +5V         |

| 109 | GND               |                  |                 |             |

| 110 | PD7               | PARALLEL PORT    | I/O14–14        | Low         |

030598 15/185

| PIN | NAME            | FUNCTIONAL BLOCK | I/O BUFFER TYPE                | RESET STATE |

|-----|-----------------|------------------|--------------------------------|-------------|

| 111 | PD6             | PARALLEL PORT    | I/O14–14                       | Low         |

| 112 | PD5             | PARALLEL PORT    | I/O14–14                       | Low         |

| 113 | PD4             | PARALLEL PORT    | I/O14–14                       | Low         |

| 114 | PD3             | PARALLEL PORT    | I/O14–14                       | Low         |

| 115 | PD2             | PARALLEL PORT    | I/O14–14                       | Low         |

| 116 | PD1             | PARALLEL PORT    | I/O14–14                       | Low         |

| 117 | PD0             | PARALLEL PORT    | I/O14–14                       | Low         |

| 118 | BUSY            | PARALLEL PORT    | I                              | Enabled     |

| 119 | STB/WRITE       | PARALLEL PORT    | OD14 or O14–14<br>(see note 2) | High–Z      |

| 120 | V <sub>CC</sub> |                  |                                | +5V         |

| 121 | GND             |                  |                                |             |

| 122 | ACK             | PARALLEL PORT    | I                              | Enabled     |

| 123 | SLCT            | PARALLEL PORT    | I                              | Enabled     |

| 124 | PE              | PARALLEL PORT    | I                              | Enabled     |

| 125 | ERROR           | PARALLEL PORT    | I                              | Enabled     |

| 126 | ĪNIT            | PARALLEL PORT    | OD14 or O14–14<br>(see note 2) | High–Z      |

| 127 | SLCTIN          | PARALLEL PORT    | OD14 or O14–14<br>(see note 2) | High–Z      |

| 128 | AUTOFD          | PARALLEL PORT    | OD14 or O14–14<br>(see note 2) | High–Z      |

| 129 | CTSA            | SERIAL PORT A    | I                              | Enabled     |

| 130 | DCDA            | SERIAL PORT A    | I                              | Enabled     |

| 131 | DSRA            | SERIAL PORT A    | I                              | Enabled     |

| 132 | DTRA            | SERIAL PORT A    | O4–2                           | High        |

| 133 | RIA             | SERIAL PORT A    | I                              | High        |

| 134 | RTSA            | SERIAL PORT A    | O4–2                           | High        |

| 135 | V <sub>CC</sub> |                  |                                | +5V         |

| 136 | GND             |                  |                                |             |

| 137 | SINA            | SERIAL PORT A    | I                              | Enabled     |

| 138 | SOUTA           | SERIAL PORT A    | O4–2                           | High        |

| 139 | CTSB            | SERIAL PORT B    | I                              | Enabled     |

| 140 | DCDB            | SERIAL PORT B    | I                              | Enabled     |

| 141 | DSRB            | SERIAL PORT B    | I                              | Enabled     |

| 142 | DTRB            | SERIAL PORT B    | O4–2                           | High        |

| 143 | RIB             | SERIAL PORT B    | I                              | High        |

| 144 | RTSB            | SERIAL PORT B    | O4–2                           | High        |

030598 16/185

| PIN | NAME            | FUNCTIONAL BLOCK | I/O BUFFER TYPE | RESET STATE |

|-----|-----------------|------------------|-----------------|-------------|

| 145 | SINB            | SERIAL PORT B    | I               | Enabled     |

| 146 | SOUTB           | SERIAL PORT B    | O4–2            | High        |

| 147 | GP07            | GPIO             | I/OD4–P10K      | High–Z      |

| 148 | GP06            | GPIO             | I/OD4–P10K      | High–Z      |

| 149 | GP05            | GPIO             | I/OD4–P10K      | High–Z      |

| 150 | GP04            | GPIO             | I/OD4–P10K      | High–Z      |

| 151 | GP03            | GPIO             | I/OD4–P10K      | High–Z      |

| 152 | GP02            | GPIO             | I/OD4–P10K      | High–Z      |

| 153 | GP01            | GPIO             | I/OD4–P10K      | High–Z      |

| 154 | GP00            | GPIO             | I/OD4–P10K      | High–Z      |

| 155 | GP13            | GPIO             | I/OD4–P10K      | High–Z      |

| 156 | GP12            | GPIO             | I/OD4–P10K      | High–Z      |

| 157 | GP11            | GPIO             | I/OD4–P10K      | High–Z      |

| 158 | GP10            | GPIO             | I/OD4–P10K      | High–Z      |

| 159 | CS0             | CHIP SELECT      | O4–2            | High–Z      |

| 160 | V <sub>CC</sub> |                  |                 | +5V         |

# NOTES:

1. The IRQ3-7, 9-11, 12, 14, and 15 pins can be programmed as open drain or totem-pole outputs.

2. AUTOFD, INIT, SLCTIN, and STB/WRITE have output structures which are configured as open–drain when ISA–or PS/2– compatible parallel port operating modes are selected. When any other parallel port mode is selected the output structures are push–pull.

| PIN (I/O I   | BUFFER) TYPE DESCRIPTIONS                                                                                                              | OD12 – Open drain output, 12 mA sink                           |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| I            | – Input                                                                                                                                | OD14 – Open drain output, 14 mA sink                           |

| ICLK         | <ul> <li>Clock input</li> </ul>                                                                                                        | OD40 – Open drain Output; 40 mA sink,                          |

| IOSC         | <ul> <li>Oscillator input</li> </ul>                                                                                                   | -4 mA source                                                   |

| IS<br>I/O04– | <ul> <li>Schmitt input</li> </ul>                                                                                                      | OD4–P10K – Open–drain Output, 4 mA sink, 10KΩ<br>min. pull–up  |

| PB2/10K      | <ul> <li>Pseudo-bidrectional I/O; 4 mA sink, -2<br/>mA source (for 10 ns on low to high<br/>transition), 10 KΩ min. pull-up</li> </ul> | OD16–P10K– Open–drain Output, 16 mA sink, 10KΩ<br>min. pull–up |

| 04–2         | <ul> <li>Totem–pole output; 4 mA sink, –2 mA<br/>source</li> </ul>                                                                     | PIN STATE DESCRIPTIONS<br>High–Z – High Impedance              |

| O12–6        | <ul> <li>Totem–pole output; 12 mA sink, 6 mA<br/>source</li> </ul>                                                                     | Enabled – Power applied; electrically function<br>ing input    |

| O14–14       | <ul> <li>Totem-pole output; 14 mA sink,<br/>-14 mA source</li> </ul>                                                                   | Unchanged – Previous state not affected                        |

#### 3.0 CHIP CONFIGURATION

The configuration of the I/O resources of the DS83CH20 is very flexible and is optimized for design in Plug and Play compatible motherboards in which the resources required by their components are known. With its flexible resource allocation architecture, the DS83CH20 allows the BIOS to assign resources at POST.

# 3.1 CONFIGURATION REGISTER OVERVIEW

The configuration of the DS83CH20 is controlled via a series of registers which are accessed via an index and data register pair are located within the ISA I/O memory map at locations 02EH, and 02FH, respectively.

A summary of the DS83CH20 chip configuration registers is given in Table 3–1.

| INDEX<br>ADDRESS | ТҮРЕ | RESET<br>VALUE | CONFIGURATION REGISTER              |  |

|------------------|------|----------------|-------------------------------------|--|

| 002H             | R/W  | FCH            | FDC Enable                          |  |

| 003H             | R/W  | Сон            | FDC Mode                            |  |

| 006H             | R/W  | A6H            | FDC Resource Select                 |  |

| 007H             | R/W  | F8H            | Parallel Port Enable                |  |

| 008H             | R/W  | 00H            | Parallel Port Mode                  |  |

| 009H             | R/W  | 00H            | Parallel Port Base Address Select   |  |

| 00BH             | R/W  | 40H            | Parallel Port Resource Select       |  |

| 00CH             | R/W  | F8H            | UART A Enable                       |  |

| 00DH             | R/W  | FEH            | UART A Mode                         |  |

| 00EH             | R/W  | 00H            | UART A Base Address Select          |  |

| 010H             | R/W  | F0H            | UART A Resource Select              |  |

| 011H             | R/W  | F8H            | UART B Enable                       |  |

| 012H             | R/W  | C4H            | UART B Mode                         |  |

| 013H             | R/W  | 00H            | UART B Base Address Select          |  |

| 015H             | R/W  | F0H            | UART B Resource Select              |  |

| 016H             | R/W  | FCH            | RTC Enable                          |  |

| 018H             | R/W  | СОН            | KBC Enable                          |  |

| 01AH             | R/W  | 00H            | Chip Select Enable                  |  |

| 01BH             | R/W  | 00H            | CS0 Lower Base Address/Range Select |  |

| 01CH             | R/W  | 00H            | CS0 Upper Base Address Select       |  |

| 01DH             | R/W  | 00H            | CS1 Lower Base Address/Range Select |  |

| 01EH             | R/W  | 00H            | CS1 Upper Base Address Select       |  |

| 020H             | R    | 20H            | Model Byte                          |  |

| 022H             | R/W  | 00H            | GP0,1 Enable                        |  |

| 023H             | R/W  | 00H            | GP0,1 Base Address Select           |  |

### DS83CH20 CONFIGURATION REGISTER SUMMARY Table 3-1

030598 18/185

| INDEX<br>ADDRESS | ТҮРЕ | RESET<br>VALUE | CONFIGURATION REGISTER     |

|------------------|------|----------------|----------------------------|

| 025H             | R/W  | 00H            | GP0 Data Direction         |

| 026H             | R/W  | 00H            | GP0 Isolation Control      |

| 027H             | R/W  | F0H            | GP1 Data Direction         |

| 028H             | R/W  | F0H            | GP1 Isolation Control      |

| 029H             | R/W  | N/A            | Kickstart Source Select    |

| 02AH             | R/W  | N/A            | Kickstart Source Status    |

| 30H              | R/W  | 31H            | IRQ8–15 Open Drain Control |

| 31H              | R/W  | 07H            | IRQ2–7 Open Drain Control  |

A detailed description of each of the configuration registers is given the tables below. Unless otherwise noted, "RESET VALUE" refers to the initialized state of the register which results when the RSTDRV signal is applied.

030598 19/185

**3.2 FLOPPY DISK CONTROLLER** Table 3–2 is a description of the configuration registers for the floppy disk controller.

| REGISTER   | ADDRESS   | RESET<br>VALUE |           | DESCRIPTION                                                                           |

|------------|-----------|----------------|-----------|---------------------------------------------------------------------------------------|

| FDC Enable | 002H, R/W | FCH            | Bit [0]   | FDC Enable                                                                            |

|            |           |                |           | <ul> <li>= 0 FDC disabled from memory map and in<br/>power down</li> </ul>            |

|            |           |                |           | = 1 FDC enabled; (FDC out of power down; s/w reset required to initialize.)           |

|            |           |                | Bit [1]   | Reserved, read as 0.                                                                  |

|            |           |                | Bit [7:2] | Reserved, read as 1's                                                                 |

| FDC Mode   | 003H, R/W | COH            | Bit [0]   | TDR Mode                                                                              |

|            |           |                |           | = 0 AT Compatible TDR                                                                 |

|            |           |                |           | = 1 Enhanced Floppy Mode 2                                                            |

|            |           |                | Bit [2:1] | Interface Mode                                                                        |

|            |           |                |           | = 00 AT Mode                                                                          |

|            |           |                |           | = 01 (Reserved)                                                                       |

|            |           |                |           | = 10 (Reserved)                                                                       |

|            |           |                |           | = 11 PS/2                                                                             |

|            |           |                | Bit [3]   | Secondary FDC Base I/O Addr. Select                                                   |

|            |           |                |           | = 0 Primary FDC Addr. selected (03F0–03F7H)                                           |

|            |           |                |           | = 1 Secondary FDC Addr. selected<br>(0370–0377H)                                      |

|            |           |                | Bit [4]   | Drive Mapping Enable                                                                  |

|            |           |                |           | = 0 Drive map disabled                                                                |

|            |           |                |           | <ul><li>= 1 Drive map enabled; selection via Drive Map<br/>1,0 bits in TDR.</li></ul> |

|            |           |                | Bit [5]   | Density Select Polarity Bit (inverse)                                                 |

|            |           |                |           | = 0 DENSEL pin is active low for 500K bps or 1<br>Mbps data rates                     |

|            |           |                |           | <ul> <li>1 DENSEL pin is active high for 500K bps or 1<br/>Mbps data rates</li> </ul> |

|            |           |                | Bit [7:6] | Reserved, read as 1's                                                                 |

# FLOPPY DISK CONFIGURATION TABLE 3-2

030598 20/185

| REGISTER           | ADDRESS   | RESET<br>VALUE |           | DESCRIPTION                   |

|--------------------|-----------|----------------|-----------|-------------------------------|

| FDC                | 006H, R/W | A6H            | Bit [3:0] | Interrupt channel assignment  |

| Resource<br>Select |           |                |           | = 0000 No interrupt assigned  |

| Select             |           |                |           | = 0001 Reserved               |

|                    |           |                |           | = 0010 Reserved               |

|                    |           |                |           | = 0011 IRQ3                   |

|                    |           |                |           | = 0100 IRQ4                   |

|                    |           |                |           | = 0101 IRQ5                   |

|                    |           |                |           | = 0110 IRQ6                   |

|                    |           |                |           | = 0111 IRQ7                   |

|                    |           |                |           | = 1000 Reserved               |

|                    |           |                |           | = 1001 IRQ9                   |

|                    |           |                |           | = 1010 IRQ10                  |

|                    |           |                |           | = 1011 IRQ11                  |

|                    |           |                |           | = 1100 Reserved               |

|                    |           |                |           | = 1101 Reserved               |

|                    |           |                |           | = 1110 IRQ14                  |

|                    |           |                |           | = 1111 IRQ15                  |

|                    |           |                | Bit [6:4] | DMA channel assignment        |

|                    |           |                |           | = 000 DMA0                    |

|                    |           |                |           | = 001 DMA1                    |

|                    |           |                |           | = 010 DMA2                    |

|                    |           |                |           | = 011 DMA3                    |

|                    |           |                |           | = 1XX No DMA channel assigned |

|                    |           |                | Bit [7]   | Reserved, read as 1           |

030598 21/185

**3.3 PARALLEL PORT** Table 3–3 is a description of the configuration registers for the parallel port.

| REGISTER      | INDEX<br>ADDRESS | RESET<br>VALUE |           | DESCRIPTION                                                                                            |

|---------------|------------------|----------------|-----------|--------------------------------------------------------------------------------------------------------|

| Parallel Port | 007H, R/W        | F8H            | Bit [0]   | Parallel Port Enable                                                                                   |

| Enable        |                  |                |           | = 0 Parallel port disabled from memory map and<br>in power down                                        |

|               |                  |                |           | = 1 Parallel port enabled                                                                              |

|               |                  |                | Bit [1]   | Parallel Port Auto–Power Management Enable                                                             |

|               |                  |                |           | = 0 Auto-power Management disabled                                                                     |

|               |                  |                |           | = 1 Auto-power Management enabled                                                                      |

|               |                  |                | Bit [2]   | Parallel Port Leakage Control                                                                          |

|               |                  |                |           | <ul> <li>= 0 Parallel port pins in normal operation during<br/>power down</li> </ul>                   |

|               |                  |                |           | <ul> <li>= 1 Parallel port output pins in High–Z; input<br/>pins disabled during power down</li> </ul> |

|               |                  |                | Bit [7:3] | Reserved, read as 1's                                                                                  |

| Parallel Port | 008H, R/W        | 00H            | Bit [2:0] | Mode Select                                                                                            |

| Mode          |                  |                |           | = 000 ISA Compatible*                                                                                  |

|               |                  |                |           | = 001 PS/2 Compatible**                                                                                |

|               |                  |                |           | = 010 EPP-1.7 and ISA Compatible                                                                       |

|               |                  |                |           | = 011 EPP-1.9 and ISA Compatible                                                                       |