# Application Note 352 General E1 Network Interface Design

www.dalsemi.com

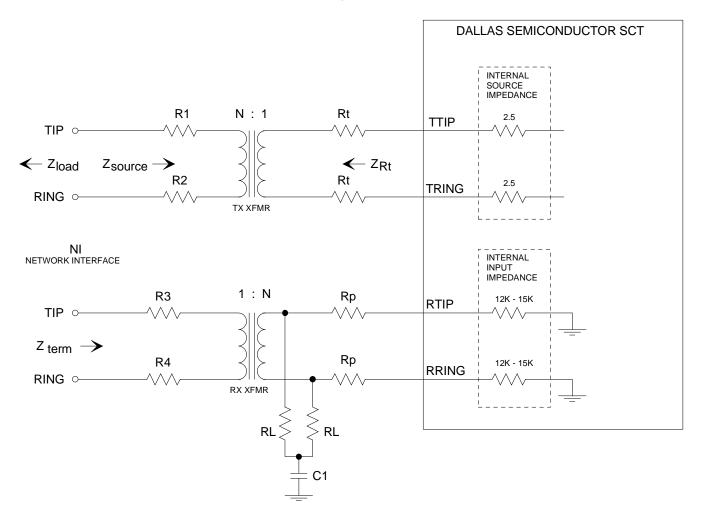

### General network interface circuit: Figure 1

Figure 1 illustrates a general form of the interface circuit for E1 transceiver chips. Not all of the components are necessary in all applications. This circuit is used to illustrate how to distribute resistance around the transformers. Application note 324 discusses over voltage protection in more detail.

The transmitter output drivers present a low impedance to inbound surges and must be able to drive sufficient current in the primary of the transmit transformer in order to produce the required output pulse at the network interface. The receiver inputs present a high impedance to inbound surges and require very little input current to operate. For these reasons, the transmitter and receiver pins require different protection techniques.

The receiver inputs are designed to recover a signal under these conditions:

- 1:1 transformer

- 0Ω series resistance

- Load resistance matched to cable impedance.  $75\Omega$  or  $120\Omega$ .

The 5.0 volt transmitter output drivers are designed to fit a pulse into a template, measured under these conditions:

- 1:1.15 step up transformer.

- 0Ω series resistance.

- Specified load.  $75\Omega$  or  $120\Omega$ .

The 3.3 volt transmitter output drivers are designed to fit a pulse into a template, measured under these conditions:

- 1:2 step up transformer.

- 0Ω series resistance.

- Specified load.  $75\Omega$  or  $120\Omega$ .

#### **Receive circuit:**

The receive circuit is the most straight forward. Generally a 1:1 transformer is used to interface to the receiver inputs. The primary consideration in the receive circuit is the accurate termination of the transmission line. E1 is carried on 75 $\Omega$  unbalanced Coax or 120 $\Omega$ balanced twisted pair. The components involved in the termination are R<sub>3</sub>, R<sub>4</sub> and the two R<sub>L</sub> resistors. R<sub>3</sub> and R<sub>4</sub> are added as part of the protection network. As these resistance values increase, R<sub>L</sub> resistance decreases. This then becomes a voltage divider. If R<sub>3</sub> and R<sub>4</sub> are too large, then the signal is divided down and the receiver may be unable to recover weak signals. The two R<sub>P</sub> resistors do not significantly affect the termination due to the relatively high input impedance of the receiver inputs. The following equation describes the termination:

$Z_{term} = R_3 + R_4 + 2R_L/N^2$ Substitute  $Z_{term} = 75\Omega$  or  $Z_{term} = 120\Omega$  and N = 1Then solve for  $R_3$ ,  $R_4$ ,  $2R_L$

Capacitor C<sub>1</sub>, along with resistors R<sub>L</sub>, form a high frequency cutoff filter for improved noise immunity.

#### Transmit circuit:

Several considerations must be made for the transmit interface circuit. Some applications require that the source impedance be closely matched to the characteristic impedance of the network. Along with this there may be a need to provide for protection of the circuit against power line cross (UL) and transient (FCC) conditions. All of these requirements must be considered simultaneously. Matching source impedance to the characteristic impedance of the line prevents reflection of stray signals by the transmitter, and is referred to as Return Loss which is calculated as

Return Loss (dB) = 20 log<sub>10</sub> |Z<sub>source</sub> - Z<sub>load</sub>|/|Z<sub>source</sub> + Z<sub>load</sub>|

Where

$$Z_{load}$$

= 120 $\Omega$  or 75 $\Omega$

$Z_{source}$  =  $R_1 + R_2 + N^2 (2R_t + 5)$

When designing for high return loss without the need for circuit protection, R1 and R2 = 0. Resistors  $R_1$ ,  $R_2$  and  $R_t$  are added as part of a protection network. See application note 324. The Dallas Semiconductor

E1 transceivers have programmable output levels which along with the transmit transformer turns ratio are used to compensate for resistive components between TTIP and TRING and the network interface so that signals arrive at the network interface with a peak voltage of 3.0 V for 120  $\Omega$  applications or 2.37 V for 75  $\Omega$  applications. Table 1 shows which Line Build Out (LBO) settings to choose based on transformer turns ratio and Z<sub>rt</sub>. All resistance between the device and the network interface must be included in the Z<sub>rt</sub> which is calculated as

$$Z_{rt} = 2R_t + ((R_1 + R_2)/N^2)$$

## Table 1 LINE BUILD OUT SELECT IN LICR FOR 5 VOLT DEVICES

| L2 | L1 | LO | APPLICATION      | TRANSFORMER | RETURN   | $Z_{Rt}^{2}$ |

|----|----|----|------------------|-------------|----------|--------------|

|    |    |    |                  | Ν           | $LOSS^1$ |              |

| 0  | 0  | 0  | 75 ohm normal    | 1.15        |          | 0            |

| 0  | 0  | 1  | 120 ohm normal   | 1.15        |          | 0            |

| 0  | 1  | 0  | 75 ohm normal    |             |          |              |

|    |    |    | with protection  | 1.15        |          | 16.4         |

|    |    |    | resistors        |             |          |              |

| 0  | 1  | 1  | 120 ohm normal   |             |          |              |

|    |    |    | with protection  | 1.15        |          | 16.4         |

|    |    |    | resistors        |             |          |              |

| 1  | 0  | 0  | 75 ohm           | 1.15        | 21dB     | 54           |

|    |    |    | high return loss |             |          |              |

| 1  | 1  | 0  | 75 ohm           | 1.36        | 21dB     | 36           |

|    |    |    | high return loss |             |          |              |

| 1  | 0  | 0  | 120 ohm          | 1.36        | 21dB     | 54           |

|    |    |    | high return loss |             |          |              |

## Table 2 LINE BUILD OUT SELECT IN LICR FOR 3.3 VOLT DEVICES

| L2 | L1 | LO | APPLICATION      | TRANSFORMER | RETURN   | $Z_{Rt}^2$ |

|----|----|----|------------------|-------------|----------|------------|

|    |    |    |                  | Ν           | $LOSS^1$ |            |

| 0  | 0  | 0  | 75 ohm normal    | 1:2         |          | 0          |

| 0  | 0  | 1  | 120 ohm normal   | 1:2         |          | 0          |

| 0  | 1  | 0  | 75 ohm normal    |             |          |            |

|    |    |    | with protection  | 1:2         |          | 5          |

|    |    |    | resistors        |             |          |            |

| 0  | 1  | 1  | 120 ohm normal   |             |          |            |

|    |    |    | with protection  | 1:2         |          | 5          |

|    |    |    | resistors        |             |          |            |

| 1  | 0  | 0  | 75 ohm           | 1:2         | 21dB     | 12.4       |

|    |    |    | high return loss |             |          |            |

| 1  | 0  | 1  | 120 ohm          | 1:2         | 21dB     | 23.2       |

|    |    |    | high return loss |             |          |            |

## NOTE:

- 1. The return loss in this table is a minimum value, the actual calculated value will exceed 21dB. Empty cells indicate that return loss is less than 21dB.

- 2. The above table differs from the data book in that it shows the total  $Z_{Rt.}$  The table in the data book shows the individual values of Rt and assumes R1 and R2 = 0.